# **TE0865 TRM**

### Download PDF version of this document. Table of contents

# Overview 1 Overview

The Trenz Election of the Dest is a high-performance MPSoC module integrating a Xilinx Zynq UltraScale+ ZU17EG (other assembly options for the FPGA are available), up to 8 GByte DDR4 SDRAM with ECC on SS, up Mag GByte DDR4 SDRAM on PL, 256 MByte Flash memory for configuration and operation, Gigabit Ethernet PHY, and powerful switch-mode power supplies for all on-board voltages. A large number of configuration of the PINA and provided via rugged high-speed stacking connections.

The prototype contiguration options available with many configuration options available that you can customize to meet your specific needs.

All parts are at least extended temperature range of 0°C to +85°C. The module operating temperature range depends on Listomer design and cooling solution. Please contact us for options.

Refer to http://tranz System 689 thol for the current online version of this manual and other available documentation. 3.2 Dual CO. 3.3 eMMC Memory

- - 3.4 Gigabit Ethernet

# Key Features OM

- 3.7 Crypto Authentication

- SoC/FBGAOPTIGA Authentication

- ° 3.9Packader C \$760AM

- ° 8. Engine KEGurces

- 4 Power an Speeder Or 2 Sequence

- 4.1 Emperatureply, E,\*, \*

- RAM/Storagever Consumption

- 4.30 PR4conDRS invitrion Corporation Corporation

- 4.4 Power-Dataevidemc64 bit

- 4.5 VoltageSilveniterC4GBit

- 4.6 Power Spiced: 2400 (Gb/s) \*\*\*

- · 4. DBR 4 of Rages

- 5 Board to Board CoDate Width: 64 bit

- 5.1 FeatureSize: def. 4GB\*

- 5.2 Connecspeddtingak@666 (Gb/s) \*\*\*

- Settimeter Speed Ratings

- ° 5.4 Current Datangidth: 8 Bit

- 5.5 Connective/Meehanical Ratings

- o 5.6 War QSR boot Rashin data parallel mode (size depends on assembly version)

- 6 Technical Specific and Swidth: 8bit

- 6.1 Absolutsizeadefu64 MBtings

- €.2/A@addressiseriapEERROOdwithieUI-48™ node identity (Microchip 24AA025E48)

- On Board Physical Dimensions

- 7 Currendy Infét Max/100 #PCGA as CPLD

- 8 Revision bis MEMS Oscillator

- 8. GigabityEthernerisianstervery PHY (Marvell Alaska 88E1512)

- 8.24 Speeded SB2 add PI Hranssceiver with full OTG support (Microchip USB3340C)

- O Diselfacer

- · 9. 96 PHD POSACY

- 9.2400 PIP 05 Warranty

- 9.34 IPStation of Liability

- 9.3 Samiect Abceterate HD B2B connector

- 9.57 Miles logy Licenses

Power9.6 Environmental Protection

- 9.72 EAGUL SUPPLY FOR AGEEE

- 10 Tableof vanable Bank IO Power Input

- Dimension

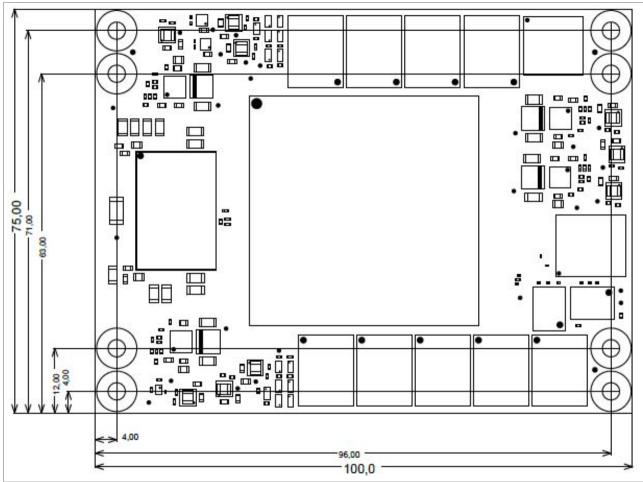

- ° 7.5 cm x 10 cm

- Notes

- \* depends on assembly version

\*\* also non low power assembly options possible

\*\*\* depends on used U+ Zynq and DDR4 combination

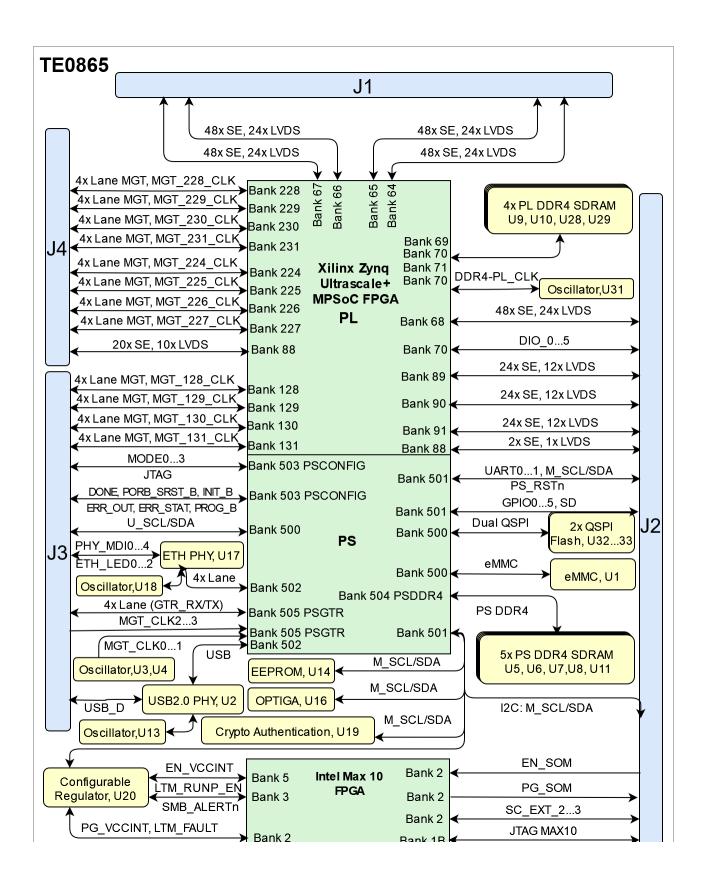

# **Block Diagram**

| ^ |  |

|---|--|

|   |  |

TE0865 block diagram

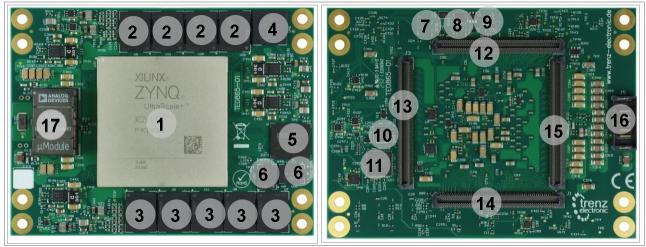

### **Main Components**

### TE0865 main components

- 1. ZYNQ Ultrascale+ MPSoC FPGA, U30

- PL DDR4 SDRAM, U9, U10, U28, U29

PS DDR4 SDRAM, U9, U10, U28, U29

Intel MAX 10 FPGA, U46

- 5. eMMC RAM, U1

- 6. Dual QSPI Flash, U32, U33

- 7. Crypto Authentication IC, U19

- 8. OPTIGA Trust M Authentication IC, U16

- 9. EEPROM MAC Address, U1410. USB2.0 Transceiver, U2

- 11. Gigabit Ethernet Transceiver, U17

- B2B Connector, J2

B2B Connector, J3

- 14. B2B Connector, J1

- B2B Connector, J4

Power Terminal, J5

- 17. Configurable Regulator, U20

## **Initial Delivery State**

| Storage device name    | Content        | Notes        |

|------------------------|----------------|--------------|

| Quad SPI Flash         | Not Programmed |              |

| EEPROM                 | Programmed     | MAC Address  |

| System Controller CPLD | Programmed     | Intel MAX 10 |

| PL DDR4 SDRAM          | Not Programmed |              |

| PS DDR4 SDRAM          | Not Programmed |              |

| eMMC                   | Not Programmed |              |

Initial delivery state of programmable devices on the module

# **Configuration Signals**

| Function              | Schematic | Connected to  | Direction | Description |

|-----------------------|-----------|---------------|-----------|-------------|

| Boot Mode             | MODE03    | B2B, J3A      | Input     |             |

| Reset                 | PERST0    | B2B, J1B      | Input     |             |

| Power Good            | PG_SOM    | B2B, J2B      | Output    |             |

| Power Enable          | EN_SOM    | B2B, J2B      | Input     |             |

| Manual Reset          | MR        | B2B, J2B      | Output    |             |

|                       |           | CPLD, U46     | Output    |             |

| Power Signal          | PG_+3.3V  | B2B, J2B      | Output    |             |

| Battery Supply        | V_BAT     | Bank PSCONFIG | Input     |             |

| Control Signal        | DONE      | B2B, J3B      | Output    | Pull up     |

| Control Signal        | POR_B     | B2B, J3B      | Input     | Pull up     |

| Initialization Signal | INIT_B    | B2B, J3B      | Output    | Pull up     |

| Program Signal        | PROG_B    | B2B, J3B      | Output    | Pull up     |

| Reset Signal          | SRST_B    | B2B, J3B      | Input     | Pull up     |

Controller signal.

# Signals, Interfaces and Pins

## Board to Board (B2B) I/Os

FPGA bank number and number of I/O signals connected to the B2B connector:

| Bank | Туре    | B2B Connector | I/O Signal Count                    | Voltage  | Notes            |

|------|---------|---------------|-------------------------------------|----------|------------------|

| 64   | HP      | JM2           | 48x Single Ended,<br>24x LVDS Pairs | Variable | Max voltage 1.8V |

| 65   | HP      | JM2           | 24x Single Ended,<br>12x LVDS Pairs | Variable | Max voltage 1.8V |

| 65   | HP      | JM3           | 24x Single Ended,<br>12x LVDS Pairs | Variable | Max voltage 1.8V |

| 66   | HP      | JM1           | 48x Single Ended,<br>24x LVDS Pairs | Variable | Max voltage 1.8V |

| 500  | MIO     | JM1           | 26x Single Ended                    | 1.8V     | MIO025           |

| 501  | MIO     | JM1           | 6x Single Ended                     | Variable | Max voltage 3.3V |

| 505  | GTR     | JM3           | 16x Single Ended,<br>8x LVDS Pairs  | 0.85V    | 4x Lanes         |

| 505  | GTR CLK | JM3           | 2x differential Clock               | -        |                  |

General PL I/O to B2B connectors information

For detailed information about the pin-out, please refer to the Pin-out table.

## **MGT Lanes**

The Xilinx Zynq UltraScale+ device used on the TE0865 module has 4x Lanes MGT transceivers connected to Bank 505 PSGTR. All 4x lanes are wired directly to B2B connector J3B consisting of one transmit and one receive (TX/RX) differential pairs, four signals total per one MGT lane. Furthuremore, MGT clocks are sourced by oscillators U3 and U4 at 27 and 100 MHz respectively.

Following table lists lane number, FPGA bank number, transceiver type, signal schematic name, boardto-board pin connection and FPGA pins connection:

| Bank           | Pin        | Signal Name                                                                            | B2B Pin                                                                        | Note    |

|----------------|------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------|

| 505<br>(PSGTR) | MGT Lane 0 | <ul> <li>GTR_RX0_P</li> <li>GTR_RX0_N</li> <li>GTR_TX0_P</li> <li>GTR_TX0_N</li> </ul> | <ul> <li>J3B-D39</li> <li>J3B-D40</li> <li>J3B-C38</li> <li>J3B-C39</li> </ul> |         |

|                | MGT Lane 1 | • GTR_RX1_P<br>• GTR_RX1_N<br>• GTR_TX1_P<br>• GTR_TX1_N                               | <ul> <li>J3B-D36</li> <li>J3B-D37</li> <li>J3B-C35</li> <li>J3B-C36</li> </ul> |         |

|                | MGT Lane 2 | • GTR_RX2_P<br>• GTR_RX2_N<br>• GTR_TX2_P<br>• GTR_TX2_N                               | <ul> <li>J3B-D33</li> <li>J3B-D34</li> <li>J3B-C32</li> <li>J3B-C33</li> </ul> |         |

|                | MGT Lane 3 | <ul> <li>GTR_RX3_P</li> <li>GTR_RX3_N</li> <li>GTR_TX3_P</li> <li>GTR_TX3_N</li> </ul> | <ul> <li>J3B-D30</li> <li>J3B-D31</li> <li>J3B-C29</li> <li>J3B-C30</li> </ul> |         |

|                | MGT_CLK0   | MGT505_CLK0 (P<br>/N)                                                                  | Oscillator, U3                                                                 | 27 MHz  |

|                | MGT_CLK1   | MGT505_CLK1 (P<br>/N)                                                                  | Oscillator, U4                                                                 | 100 MHz |

|                | MGT_CLK2   | <ul> <li>MGT505_CLK<br/>2_P</li> <li>MGT505_CLK<br/>2_N</li> </ul>                     | <ul><li>J3A-A29</li><li>J3A-A30</li></ul>                                      |         |

|                | MGT_CLK3   | <ul> <li>MGT505_CLK</li> <li>2_P</li> <li>MGT505_CLK</li> <li>2_N</li> </ul>           | <ul><li>J3A-B30</li><li>J3A-B31</li></ul>                                      |         |

#### MGT Lanes connection

There are 3 clock sources for the GTR transceivers. B505\_CLK0 is connected directly to B2B connector JM3, so the clock can be provided by the carrier board. Clocks B505\_CLK1 and B505\_CLK3 are provided by the on-board clock generator (U10). As there are no capacitive coupling of the data and clock lines that are connected to the connectors, these may be required on the user's PCB depending on the application.JTAG Interface

JTAG access to the UltraScale+ MPsoC FPGA through B2B connector J3B.

| JTAG Signal | B2B Connector |

|-------------|---------------|

| TMS         | J3B- D59      |

| TDI | J3B- D57 |

|-----|----------|

| TDO | J3B- D58 |

| тск | J3B- D56 |

### JTAG pins connection

JTAG access to the system controller CPLD, Intel MAX10 FPGA(U46) through B2B connector J2B.

| JTAG Signal | B2B Connector |

|-------------|---------------|

| TCK_MAX10   | J2B- D56      |

| TMS_MAX10   | J2B- D57      |

| TDO_MAX10   | J2B- D58      |

| TDI_MAX10   | J2B- D59      |

| JTAGEN      | Pulled Up     |

JTAG pins connection

## **I2C Addresses**

| I2C Address | Designator | Notes                  |

|-------------|------------|------------------------|

| 0x53        | U14        | EEPROM                 |

| 0x30        | U16        | OPTIGA Trust M         |

| 0x4E        | U20        | Configurable Regulator |

I2C addresses

### **MIO Pins**

| MIO Pin | Connected to     | Notes                                       |

|---------|------------------|---------------------------------------------|

| MIO05   | QSPI Flash, U32  |                                             |

| MIO611  | QSPI, Flash, U33 |                                             |

| MIO1322 | eMMC, U1         |                                             |

| MIO23   | B2B, J2A         | U_INIT                                      |

| MIO2425 | B2B, J3B         | I <sup>2</sup> C via Voltage Transform, U15 |

| MIO2627 | B2B, J2A         | UART0_RX                                    |

| MIO2829 | B2B, J2A         | UART1_RX                                    |

| MIO3031 | B2B, J2A         | I <sup>2</sup> C via Voltage Transform, U12 |

| MIO3237 | B2B, J2A         | GPI005                                      |

| MIO38   | B2B, J2A         | M_INIT                                      |

| MIO3942 | B2B, J2B         | SD                                          |

| MIO43     | B2B, J2A     | PS_RSTn |

|-----------|--------------|---------|

| MIO4451   | B2B, J2A     | SD      |

| MIO5263   | USB2.0, U2   | USB2.0  |

| MIO6477   | ETH PHY, U17 | ETH PHY |

| MIQa nina |              |         |

MIOs pins

## **Test Points**

| Test Point | Signal                 | Notes |

|------------|------------------------|-------|

| TP12       | +12.0V                 |       |

| TP34       | +3.3V                  |       |

| TP56       | +3.3V_SW               |       |

| TP78       | +2.3V                  |       |

| TP910      | +1.8V                  |       |

| TP1112     | +1.8V_AUX              |       |

| TP1314     | +1.8V_VCCADC           |       |

| TP1516     | +0.85V_VCCINT          |       |

| TP1718     | +1.2V_PL_DDR           |       |

| TP1920     | +2.5V_PL_DDR           |       |

| TP2122     | +0.<br>85V_GTR_AVCC_PS |       |

| TP2324     | +1.8V_GTR_AVTT_PS      |       |

| TP2526     | +1.8V_AUX_PS           |       |

| TP2728     | +1.2V_PLL_PS           |       |

| TP2930     | +1.2V_PS_DDR           |       |

| TP3132     | +2.5V_PS_DDR           |       |

| TP3334     | VREFA_DDR_PS           |       |

| TP3536     | VREFA_DDR_PL           |       |

| TP3738     | VTT_DDR_PS             |       |

| TP3940     | VTT_DDR_PL             |       |

| TP4142     | +0.9V_GTH_AVCC         |       |

| TP4344     | +1.8V_GTH_AUX          |       |

| TP4546     | +1.2V_GTH_AVTT         |       |

| TP4748     | +0.9V_GTY_AVCC         |       |

| TP4950     | +1.8V_GTY_AUX          |       |

| TP5152     | +1.2V_GTY_AVTT         |       |

#### **Test Points Information**

# **On-board Peripherals**

| Chip/Interface               | Designator                 | Notes |

|------------------------------|----------------------------|-------|

| Intel MAX 10 CPLD            | U46                        |       |

| PL DDR4 SDRAM                | U9, U10, U28, U29          |       |

| PS DDR4 SDRAM                | U5U8, U11                  |       |

| Dual QSPI Flash              | U32, U33                   |       |

| eMMC Memory                  | U1                         |       |

| USB2.0 Transceiver           | U2                         |       |

| Gigabit Ethernet Transceiver | U17                        |       |

| EEPROM                       | U14                        |       |

| Crypto Authentication        | U19                        |       |

| OPTIGA Authentication        | U16                        |       |

| MEMS Oscillator              | U3, U4, U13, U18, U31, U34 |       |

On board peripherals

# System Controller CPLD

The TE0865 is equipped with an Intel MAX 10 as System Controller CPLD (U46). Please check further information in the TE0865 CPLD page.

| Bank    | Schematic       | Connectced to  | Notes                      |

|---------|-----------------|----------------|----------------------------|

| Bank 1A | VCCIO1A         | 3.3V           |                            |

| Bank 1B | TCK_MAX10       | B2B, J2B       |                            |

|         | TMS_MAX10       | B2B, J2B       |                            |

|         | TDO_MAX10       | B2B, J2B       |                            |

|         | TDI_MAX10       | B2B, J2B       |                            |

|         | VCCIO1B         | 3.3V           |                            |

| Bank 2  | EN_VTT_DDR_PL   | Regulator, U26 |                            |

|         | EN_+2.5V_PL_DDR | Regulator, U22 | Enable Power DDR4 PL       |

|         | EN_+1.2V_PL_DDR | Regulator, U24 | Enable Power DDR4 PL       |

|         | PG_+1.2V_PL_DDR | Regulator, U24 | Power Good DDR4 PL         |

|         | EN_+1.8V_AUX_PS | Regulator, U43 |                            |

|         | EN_SOM          | B2B, J2B       | Main 'Power Enable' signal |

|         | PG_SOM          | B2B, J2B       | Main 'Power Good' signal   |

|         | SC_EXT_23       | B2B, J2B       |                            |

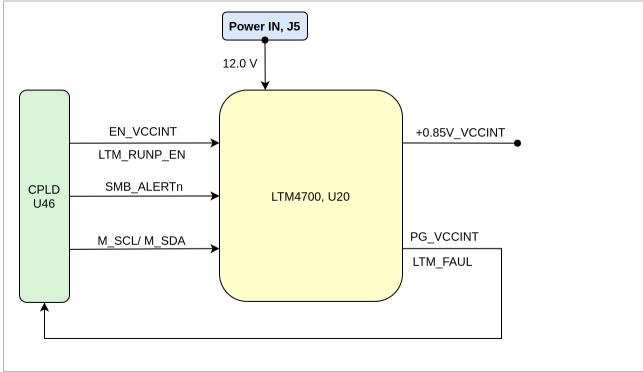

|         | PG_VCCINT       | Regulator, U20 | Configurable Regulator     |

|        | LTM_FAULT             | Regulator, U20       | Configurable Regulator           |

|--------|-----------------------|----------------------|----------------------------------|

|        | MR                    | B2B, J2B             |                                  |

|        |                       | Regulator, U51       |                                  |

| Bank 3 | SMB_ALERTn            | Regulator, U20       | Configurable Regulator           |

|        | PG_+2.5V_PL_DDR       | Regulator, U22       | Power Good DDR4 PL               |

|        | LTM_RUNP_EN           | Regulator, U20       | Configurable Regulator           |

|        | M_SDA                 | I <sup>2</sup> C Bus | B2B, J2A via level shifter (U12) |

|        | M_SCL                 | I <sup>2</sup> C Bus | B2B, J2A via level shifter (U12) |

|        | RST_SYSn              | Diod, U53B           | Reset                            |

|        | EN_+0.9V_GTH_AVCC     | Regulator, U35       |                                  |

|        | EN_+0.9V_GTY_AVCC     | Regulator, U38       |                                  |

|        | PG_+1.2V_PS_DDR       | Regulator, U25       | Power Good DDR4 PS               |

|        | PG_+0.9V_GTH_AVCC     | Regulator, U35       |                                  |

|        | PG_+0.9V_GTY_AVCC     | Regulator, U38       |                                  |

|        | EN_+3.3V_SW           | Regulator, U52       | Secondary Power                  |

|        | EN_+1.2V_PLL_PS       | Regulator, U42       |                                  |

|        | PG_+1.8V_GTR_AVTT_PS  | Regulator, U47       |                                  |

|        | PG_+1.8V              | Regulator, U41       |                                  |

|        | EN_+2.5V_PS_DDR       | Regulator, U23       | Enable Power DDR4 PS             |

|        | PG_+1.2V_GTY_AVTT     | Regulator, U39       |                                  |

|        | EN_+1.2V_GTY_AVTT     | Regulator, U39       |                                  |

|        | M_INT                 | B2B, J2A             |                                  |

|        | EN_+1.8V_VCCADC       | Regulator, U49       |                                  |

|        | PG_+0.85V_GTR_AVCC_PS | Regulator, U48       |                                  |

|        | EN_VTT_DDR_PS         | Regulator, U27       |                                  |

|        | EN_+1.8V              | Regulator, U41       |                                  |

|        | EN_+1.8V_GTY_AUX      | Regulator, U40       |                                  |

|        | PG_+2.3V              | Regulator, U45       |                                  |

| Bank 6 | VCCIO6                | 3.3V                 |                                  |

| Bank 5 | EN_+1.8V_GTR_AVTT_PS  | Regulator, U47       |                                  |

|        | EN_+1.8V_GTH_AUX      | Regulator, U37       |                                  |

|        | EN_+1.8V_AUX          | Regulator, U50       |                                  |

|        | EN_+1.2V_GTH_AVTT     | Regulator, 36        |                                  |

|        | PG_+1.2V_GTH_AVTT     | regulator, U36       |                                  |

|        | +3.3V_SW              | eMMC, U1             |                                  |

|        | EN_+1.2V_PS_DDR       | Regulator, U25       | Power Good DDR4 PS               |

|        | EN_+0.85V_GTR_AVCC_PS | Regulator, U48       |                                  |

|        | PG_+1.2V_GTH_AVTT     | Regulator, U48       |                                  |

|        | EN_VCCINT             | Regulator, U20       |                                  |

|        | EN_+2.3V              | Regulator, U45       |                                  |

| PG_+1.8V_AUX        | Regulator, U50 |                    |

|---------------------|----------------|--------------------|

| <br>PG_+2.5V_PS_DDR | Regulator, U23 | Power Good DDR4 PS |

CPLD pin connections

## **Dual QSPI Flash Memory**

The TE0865 is equipped with dual 128 Mb (256 Mb) QSPI flash memory, U32 and U33 for configuration and operation storage.

| Designator | Pin       | Schematic | Notes |  |

|------------|-----------|-----------|-------|--|

| U32        | CLK       | MIO0      |       |  |

|            | DI/IO0    | MIO4      |       |  |

|            | DO/IO1    | MIO1      |       |  |

|            | nWP/IO2   | MIO2      |       |  |

|            | nHOLD/IO3 | MIO3      |       |  |

|            | nCS       | MIO5      |       |  |

| U33        | CLK       | MIO12     |       |  |

|            | DI/IO0    | MIO8      |       |  |

|            | DO/IO1    | MIO9      |       |  |

|            | nWP/IO2   | MIO10     |       |  |

|            | nHOLD/IO3 | MIO11     |       |  |

|            | nCS       | MIO7      |       |  |

Quad SPI interface MIOs and pins

### eMMC Memory

The TE0865 is equipped with an eMMC Flash memory IC(U1) connected to the PS MIO pins MIO13.. MIO22.

| Designator | Pin    | Schematic | Connected to | Notes               |

|------------|--------|-----------|--------------|---------------------|

| U32        | CLK    | MMC-CCLK  | MIO22        |                     |

|            | nRESET | RST_PERn  | -            | PS_RSTn,<br>PS_SYSn |

|            | CMD    | MMC-CMD   | MIO21        |                     |

|            | DAT07  | MMCD07    | MIO1320      |                     |

eMMC connections

## **Gigabit Ethernet**

On-board Gigabit Ethernet PHY (U17) is provided with Marvell Alaska 88E1512 IC (U17). The Ethernet PHY RGMII interface is connected to the ZynqMP Ethernet3 PS GEM3. I/O voltage is fixed at 1.8V for HSTL signaling. The reference clock input of the ETH is supplied from an on-board 25.00 MHz oscillator (U18).

| Pin | Schematic | Connected to | Note |

|-----|-----------|--------------|------|

|-----|-----------|--------------|------|

| MDIP03  | PHY_MDI03 | B2B, J3A        |                                |

|---------|-----------|-----------------|--------------------------------|

| MDC     | ETH_MDC   | MIO76           |                                |

| MDIO    | ETH_MDIO  | MIO77           |                                |

| S_IN    | S_IN      | N.C             |                                |

| S_OUT   | S_OUT     | N.C             |                                |

| TXD03   | ETH_TXD03 | MIO6568         |                                |

| TX_CTRL | ETH_TXCTL | MIO69           |                                |

| TX_CLK  | ETH_TXCK  | MIO64           |                                |

| RXD03   | ETH_RXD03 | MIO7174         |                                |

| RX_CTRL | ETH_RXCTL | MIO75           |                                |

| RX_CLK  | ETH_RXCK  | MIO70           |                                |

| LED1    | PHY_LED1  | B2B, J3A        |                                |

| RESETn  | ETH_RST   | MIO24           |                                |

| XTAL_IN | ETH_CLK   | Oscillator, U18 | Input Clock of ETH Transciever |

| nRESET  | RST_PERn  | B2B, J2A        | PS_RSTn, PS_SYSn               |

GigaBit Ethernet connection

### **USB2.0 Transceiver**

Hi-speed USB2.0 transceiver (U2) is provided with USB3340 from Microchip. The transceiver is connected to the PS MIO via MIO52..63. The I/O voltage is fixed at 3.3V (VBAT) and PHY reference clock input is supplied from the on-board 24.00 MHz oscillator (U13).

| Pin            | Schematic         | MIO                       | B2B<br>Name | Notes                                                             |

|----------------|-------------------|---------------------------|-------------|-------------------------------------------------------------------|

| RESETB         | RST_PERn          | -                         |             | RST_PERn                                                          |

| VBAT           | VBAT              | -                         |             | 3.3V                                                              |

| CPEN           | USB_CPEN          | -                         | B2B, J3A    |                                                                   |

| VBUS           | USB_VBUS          | -                         | B2B, J3A    |                                                                   |

| ID             | USB_ID            | -                         | B2B, J3A    |                                                                   |

| DP,<br>DM      | USB_DP<br>USB_ DM | -                         | B2B, J3A    |                                                                   |

| REFCLK         | USB_CLK2<br>4_PHY | -                         | -           | 24.00MHz from on-board oscillator (U13).                          |

| REFSE<br>L[02] | -                 | -                         | -           | Reference clock frequency select, all set to 1.8V selects 24 MHz. |

| DATA0<br>7     | USB_DATA<br>07    | MIO<br>56,57,54, 59<br>62 | -           | USB Data                                                          |

| STP            | USB_STP           | MIO58                     | -           |                                                                   |

| NXT            | USB_NXT           | MIO55                     | -           |                                                                   |

| DI             | USB_DI            | MIO53                     | -           |                                                                   |

| CLKO<br>UT     | USB_CLKO<br>UT    | MIO52                     | -           |                                                                   |

General overview of the USB PHY signals

### **EEPROM**

There is an EEPROM (U14) provided on the module TE0865 for storing MAC Address. The EEPROM has the  $I^2C$  bus address 0x53.

| MIO Pin | Schematic | U25 Pin | Notes |

|---------|-----------|---------|-------|

| MIO39   | I2C_SDA   | SDA     |       |

| MIO38   | I2C_SCL   | SCL     |       |

I2C EEPROM interface MIOs and pins

## **Crypto Authentication**

The TE0865 is equipped with an authentication IC, ATECC608A (U19) which includes an EEPROM array for storage of up to 16 keys, certificates, miscellaneous read/write, read-only or secret data, consumption logging, and security configurations. Access to the various sections of memory can be restricted in a variety of ways and then the configuration can be locked to prevent changes.

| Pin | Schematic | Connected to | Notes    |

|-----|-----------|--------------|----------|

| SDA | M_SDA     | B2B, J2A     | M_SDA_PS |

| SCL | M_SDA     | B2B, J2A     | M_SCL_PS |

**Crypto Authentication connection**

### **OPTIGA** Authentication

The TE0865 is equipped with an OPTIGA Trust M IC, SLS32AIA010MH (U16). The OPTIGA Trust M comes with up to 10kB of user memory that can be used to store X.509 certificates and data. OPTIGA Trust M is based on Common Criteria (CC) Certified EAL6+ (high) hardware enabling it to prevent physical attacks on the device itself and providing high assurance that the keys or arbitrary data stored cannot be accessed by an unauthorized entity. The OPTIGA Trust M is connected via I<sup>2</sup>C with address of 0x30.

| Pin | Schematic | Connected to | Notes   |

|-----|-----------|--------------|---------|

| SDA | M_SDA     | B2B, J2A     |         |

| SCL | M_SDA     | B2B, J2A     |         |

| RST | RST_SECn  | B2B, J2A     | PS_RSTn |

**OPTIGA** Authentication connection

### PL DDR4 SDRAM

The TE0865 SoM has four volatile DDR4 SDRAM ICs connected to Programmable Logic(PL) for operations, storing and streaming data.

- Part number: MT40A1G16RC-062E\*

- Supply voltage: 1.2V

- Speed: 3200 MT/s\*

- Temperature: -40 ~ 95 °C\*

\* depends on assembly version

## **PS DDR4 SDRAM**

The TE0865 SoM has five volatile DDR4 SDRAM ICs connected to Processing System (PS) for operations, storing and streaming data.

- Part number: MT40A1G16RC-062E\*

- Supply voltage: 1.2V

Speed: 3200 MT/s\*

- Temperature: -40 ~ 95 °C\*

\* depends on assembly version

## **Clock Sources**

| Designator | Description     | Frequency | Note       |

|------------|-----------------|-----------|------------|

| U3         | MEMS Oscillator | 27 MHz    | MGT_CLK0   |

| U4         | MEMS Oscillator | 100 MHz   | MGT_CLK1   |

| U13        | MEMS Oscillator | 24 MHz    | USB_CLK    |

| U18        | MEMS Oscillator | 25 MHz    | ETH_CLK    |

| U31        | MEMS Oscillator | 200 MHz   | DDR4 Clock |

| U34        | MEMS Oscillator | 33.33 MHz | PS REF CLK |

Osillators

# Power and Power-On Sequence

## **Power Supply**

Power supply with minimum current capability of 3.0 A for system startup is recommended.

## **Power Consumption**

| Power Input Pin | Typical Current |

|-----------------|-----------------|

| VIN             | TBD*            |

**Power Consumption**

\* TBD - To Be Determined

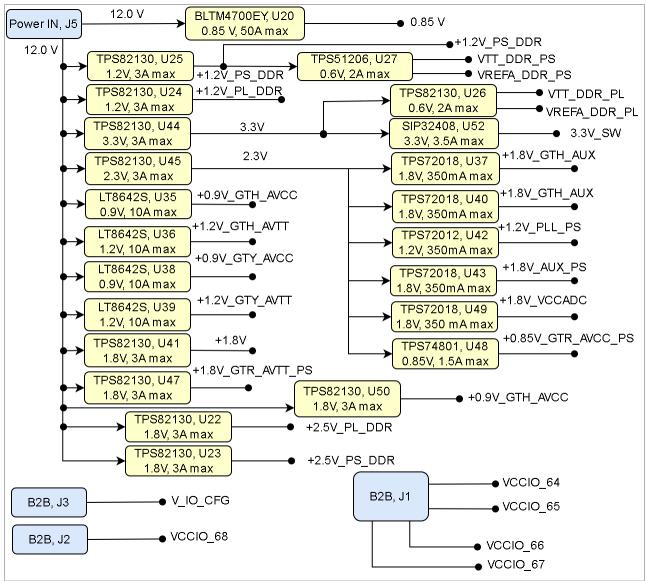

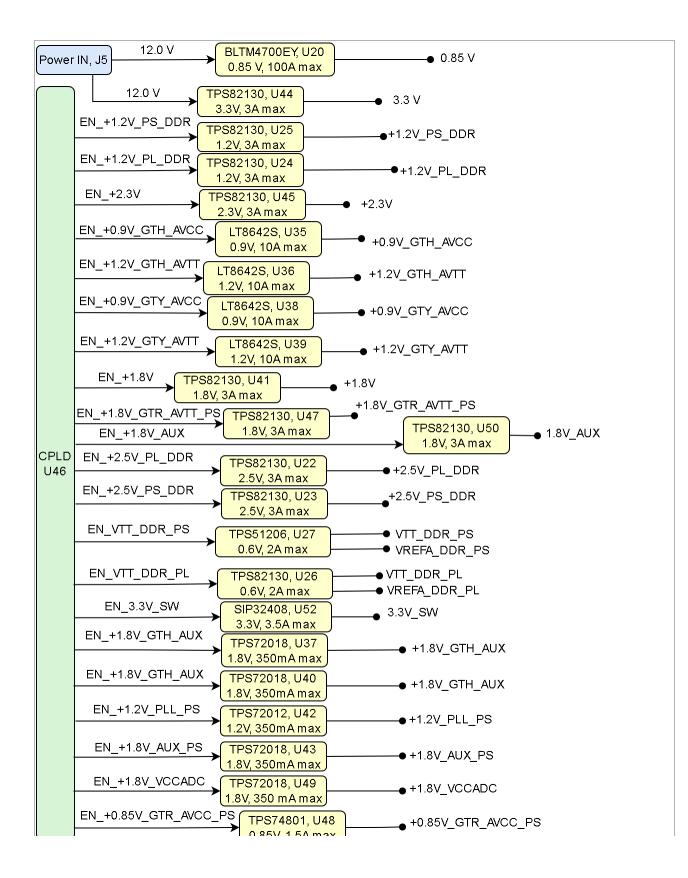

## **Power Distribution Dependencies**

**Power Distribution**

### **Power-On Sequence**

#### ( 0.00 V, 1.0A IIIAA J

Power Sequency

## **Voltage Monitor Circuit**

The LTM4700 (U20) is a dual 50A or single 100A step-down µModule(power module) DC/DC regulator featuring remote configurability and telemetry-monitoring of power management parameters over standard I2C-based digital interface protocol.

Voltage Monitor Circuit

### **Power Rails**

| Power<br>Rail Name | B2B J1<br>Pin | B2B J2<br>Pin | B2B J3<br>Pin | B2B J4<br>Pin | Direction | Notes |

|--------------------|---------------|---------------|---------------|---------------|-----------|-------|

| VCCIO_67           | D10           | -             | -             | -             | In        |       |

| VCCIO_66           | D20           | -             | -             | -             | In        |       |

| VCCIO_64           | D35           | -             | -             | -             | In        |       |

| VCCIO_65           | D45           | -             | -             | -             | In        |       |

| VCCIO_91           | -             | A6,           | -             | -             | In        |       |

| VCCIO_90           | -             | B10           | -             | -             | In        |       |

| VCCIO_89           | -             | A21           | -             | -             | In        |       |

| V_IO_CFG           | -             | A45           | -             | -             | In        |       |

| +1.<br>2V_PL_DDR   | -             | B44           | -             | -             | Out       |       |

| VCCIO_68 | - | C29 | -   | - | In  |  |

|----------|---|-----|-----|---|-----|--|

| VCCIO_88 | - | D44 | -   | - | In  |  |

| +3.3V    | - | D60 | -   | - | Out |  |

| +1.8V    | - |     | D60 | - | Out |  |

Module power rails.

# **Bank Voltages**

| Bank      | Schematic<br>Name  | Voltage   | Notes           |

|-----------|--------------------|-----------|-----------------|

| 64 HP     | VCCIO_64           | max 1.8 V |                 |

| 65 HP     | VCCIO_65           | max 1.8 V |                 |

| 66 HP     | VCCIO_66           | max 1.8 V |                 |

| 67 HP     | VCCIO_67           | max 1.8 V |                 |

| 68 HP     | VCCIO_68           | max 1.8 V |                 |

| 69 HP     | VCCIO_69           | 1.2 V     |                 |

| 70 HP     | VCCIO_70           | 1.2 V     |                 |

| 71 HP     | VCCIO_71           | 1.2 V     |                 |

| 88 HD     | VCCIO_88           | max 3.3V  | ZU17 Bank 90 HD |

| 89 HD     | VCCIO_88           | max 3.3 V | ZU17 Bank 91 HD |

| 90 HD     | VCCIO_88           | max 3.3V  | ZU17 Bank 93 HD |

| 91 HD     | VCCIO_88           | max 3.3V  | ZU17 Bank 94 HD |

| 128 GTY   | MGTAVCC_L          | 0.9 V     |                 |

| 129 GTY   | MGTAVCC_L          | 0.9 V     |                 |

| 224 GTH   | MGTAVCC_RS         | 0.9 V     |                 |

| 225 GTH   | MGTAVCC_RS         | 0.9 V     |                 |

| 228 GTH   | MGTAVCC_RN         | 0.9 V     |                 |

| 229 GTH   | MGTAVCC_RN         | 0.9 V     |                 |

| 500 PSMIO | VCCO_PSIO0_5<br>00 | 1.8 V     |                 |

| 501 PSMIO | VCCO_PSIO0_5<br>01 | max 3.3 V |                 |

| 502 PSMIO | VCCO_PSIO0_5<br>02 | 1.8 V     |                 |

| 504 PSDDR | VCCO_PSDDR_5<br>04 | 1.2 V     |                 |

| 505 PSGTR | PS_MGTRAVCC        | 0.85 V    |                 |

Zynq SoC bank voltages.

# Board to Board Connectors

The 7.5 x 10 cm modules use four Samtec AcceleRate HD High-Density on the bottom side.

• 4 x ADM6-60-01.5-L-4-2 (compatible to ADF6-60-01.5-L-4-2), (240 pins, "60" per row)

The carriers for 7.5 x 10 cm modules use four Samtec AcceleRate HD High-Density on the bottom side.

• 4 x ADF6-60-03.5-L-4-2 (compatible to ADF6-60-01.5-L-4-2), (240 pins, "60" per row)

#### Features

- Board-to-Board Connector 240-pins, 60 contacts per row

- 0.025" (0.635 mm) pitch

- Data Rate: max 56 Gbps

- Mates with: ADM6/APF6

- Insulator Material: LCP, Black

- Contact Material: Copper Alloy

- Plating: Au or Sn over 50 μ" (1.27 μm) N

- Operating Temperature Range: -55 °C to +125 °C

- PCle 5.0 capable: Yes

- Lead-Free Solderable: Yes

- RoHS Compliant: Yes

#### Connector Mating height

When using the same type on baseboard, the mating height is 5mm. Other mating heights are possible by using connectors with a different height

| Order number | Connector on baseboard | compatible to      | Mating height |

|--------------|------------------------|--------------------|---------------|

| 30095        | REF-30095              | ADM6-60-01.5-L-4-2 | 5 mm          |

| 31137        | REF-31137              | ADF6-60-03.5-L-4-2 | 5 mm          |

Connectors.

The module can be manufactured using other connectors upon request.

#### **Connector Speed Ratings**

The AcceleRate HD High-Density connector speed rating depends on the stacking height; please see the following table:

| Stacking height | Speed rating    |

|-----------------|-----------------|

| 5 mm            | 10/ 25/ 56 Gbps |

#### Speed rating.

#### **Current Rating**

Current rating of Samtec AcceleRate HD High-Density B2B connectors is 1.34 A per pin (4 pins powered)

#### Connector Mechanical Ratings

- Shock: 100G, 6 ms Sine

- Vibration: 7.5G random, 2 hours per axis, 3 axes total

#### Manufacturer Documentation

Modified

| PDF File 20200225_hsc_adm6-xx-01p5-xxx-4-a_adf6-xx-<br>03p5-xxx-4-a.pdf | 22 07, 2021 by Pedram<br>Babakhani |

|-------------------------------------------------------------------------|------------------------------------|

| PDF File adf6.pdf                                                       | 22 07, 2021 by Pedram<br>Babakhani |

| PDF File adm6.pdf                                                       | 22 07, 2021 by Pedram<br>Babakhani |

| PDF File adm6-xxx-xx.x-xxx-4-x-x-r-mkt.pdf                              | 22 07, 2021 by Pedram<br>Babakhani |

| PDF File adm6-xxx-xx.x-xxx-x-x-footprint.pdf                            | 22 07, 2021 by Pedram<br>Babakhani |

Technical Specifications

# **Absolute Maximum Ratings**

| Symbols  | Description            | Min  | Max | Unit | Note    |

|----------|------------------------|------|-----|------|---------|

| VCCR     | Input Supply Voltage   | 5.75 | 16  | V    | B2B, J5 |

| V_IO_CFG | Config Voltage         | -0.5 | 3.4 | V    | B2B,J3  |

| VCCIO_64 | Bank 64 Supply Voltage | -0.5 | 2   | V    | B2B,J1  |

| VCCIO_65 | Bank 65 Supply Voltage | -0.5 | 2   | V    | B2B,J1  |

| VCCIO_66 | Bank 66 Supply Voltage | -0.5 | 2   | V    | B2B,J1  |

| VCCIO_67 | Bank 67 Supply Voltage | -0.5 | 2   | V    | B2B,J1  |

| VCCIO_68 | Bank 68 Supply Voltage | -0.5 | 2   | V    | B2B,J2  |

| T_STG    | Storage Temperature    | -40  | 85  | °C   |         |

PS absolute maximum ratings

## **Recommended Operating Conditions**

Operating temperature range depends also on customer design and cooling solution. Please contact us for options.

| Parameter | Min  | Мах  | Units | Reference<br>Document           |

|-----------|------|------|-------|---------------------------------|

| VCCR      | 11.5 | 12.5 | V     | See LTM4700<br>(U20) datasheet. |

| V_IO_CFG  | 1.14 | 3.4  | V     |                                 |

| VCCIO_64  | 0.95 | 1.9  | V     |                                 |

| VCCIO_65  | 0.95 | 1.9  | V     |                                 |

| VCCIO_66  | 0.95 | 1.9  | V     |                                 |

| VCCIO_67 | 0.95 | 1.9 | V |                          |

|----------|------|-----|---|--------------------------|

| VCCIO_68 | 0.95 | 1.9 | V |                          |

| T_OPT    | 0    | 85  | C | See components datasheet |

Recommended operating conditions.

Components are mainly classified in 3 temperature groups, according to range specifications: commercial: 0°C - 75°C extended: 0°C - 85°C industrial: -40°C - 85°C

Classification of the module can be locked up here: Article Number Information i.e.: TE0803-03-5D"I"21-AS (The I indicates industrial)

The actual operation temperature range depends on the FPGA/SoC design/utilization and cooling, as well as other variables. Please note: These are only indications!

# **Physical Dimensions**

- Module size: 75 mm × 100 mm. Please download the assembly diagram for exact numbers.

- Mating height with standard connectors: 5 mm.

PCB thickness: 2 mm.

**Physical Dimension**

# **Currently Offered Variants**

| Trenz shop TE0865 overview page |             |  |  |  |

|---------------------------------|-------------|--|--|--|

| English page                    | German page |  |  |  |

| Tranz Electronic Shop Overview  |             |  |  |  |

#### Trenz Electronic Shop Overview

# **Revision History**

# Hardware Revision History

Board hardware revision number.

| Date       | Revision | Changes                                                                                                                                                                               | Documentation Link |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 2021-04-15 | REV01    | Initial Release                                                                                                                                                                       | REV01              |

| 2021-10-21 | REV02    | <ul> <li>Improved PCB trace<br/>to simplify<br/>production with<br/>increased reliability</li> <li>All pull down<br/>resistors on DCDC<br/>enable inputs<br/>changed to 1K</li> </ul> | REV02              |

Hardware Revision History

Hardware revision number can be found on the PCB board together with the module model number separated by the dash.

# **Document Change History**

| Date      | Revision  | Contributor | Description                                                                   |

|-----------|-----------|-------------|-------------------------------------------------------------------------------|

| Error     | ]         | ]           | <ul> <li>Key features: defaul<br/>DDR4 capacity<br/>changed to 4GB</li> </ul> |

| renderi   | Error     | Error       | <ul> <li>Added a notes in PL<br/>DDR4 SDRAM and</li> </ul>                    |

| ng        | renderi   | renderi     | PL DDR4 SDRAM<br>chapter                                                      |

| macro     | ng        | ng          | <ul> <li>Minor change in<br/>Overview chapter</li> </ul>                      |

| 'page-    | macro     | macro       |                                                                               |

| info'     | 'page-    | 'page-      |                                                                               |

| Ambiguo   | info'     | info'       |                                                                               |

| us        | Ambiguo   | Ambiguo     |                                                                               |

| method    | us        | us          |                                                                               |

| overload  | method    | method      |                                                                               |

| ing for   | overload  | overload    |                                                                               |

| method    | ing for   | ing for     |                                                                               |

| jdk.      | method    | method      |                                                                               |

| proxy27   | jdk.      | jdk.        |                                                                               |

| 9.\$Proxy | proxy27   | proxy27     |                                                                               |

| 4022#ha   | 9.\$Proxy | 9.\$Proxy   |                                                                               |

| sConten   | 4022#ha   | 4022#ha     |                                                                               |

| tLevelPe  | sConten   | sConten     |                                                                               |

| rmission  | tLevelPe  | tLevelPe    |                                                                               |

|           | rmission  | rmission    |                                                                               |

| Cannot    |           |             |                                                                               |

| resolve   | Cannot    | Cannot      |                                                                               |

| which      | resolve    | resolve    |

|------------|------------|------------|

| method     | which      | which      |

| to         | method     | method     |

| invoke     | to         | to         |

| for [null, | invoke     | invoke     |

| class      | for [null, | for [null, |

| java.      | class      | class      |

| lang.      | java.      | java.      |

| String,    | lang.      | lang.      |

| class      | String,    | String,    |

| com.       | class      | class      |

| atlassian  | com.       | com.       |

|            | atlassian  | atlassian  |

| confluen   |            |            |

| ce.        | confluen   | confluen   |

| pages.     | ce.        | ce.        |

| Page]      | pages.     | pages.     |

| due to     | Page]      | Page]      |

| overlapp   | due to     | due to     |

| ing        | overlapp   | overlapp   |

| prototyp   | ing        | ing        |

| es         | prototyp   | prototyp   |

| between    | es         | es         |

| :          | between    | between    |

| [interfac  | :          | :          |

| e com.     | [interfac  | [interfac  |

| atlassian  | e com.     | e com.     |

|            | atlassian  | atlassian  |

| confluen   |            |            |

| ce.user.   | confluen   | confluen   |

| Conflue    | ce.user.   | ce.user.   |

| nceUser    | Conflue    | Conflue    |

| , class    | nceUser    | nceUser    |

| java.      | , class    | , class    |

| lang.      | java.      | java.      |

| String,    | lang.      | lang.      |

| class      | String,    | String,    |

| com.       | class      | class      |

| atlassian  | com.       | com.       |

| <u> </u>   | atlassian | atlassian     |                                                                                                                                               |

|------------|-----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| confluen   |           |               |                                                                                                                                               |

| ce.core.   | confluen  | confluen      |                                                                                                                                               |

| Content    | ce.core.  | ce.core.      |                                                                                                                                               |

| EntityOb   | Content   | Content       |                                                                                                                                               |

| ject]      | EntityOb  | EntityOb      |                                                                                                                                               |

| [interfac  | ject]     | ject]         |                                                                                                                                               |

| e com.     | [interfac | [interfac     |                                                                                                                                               |

| atlassian  | e com.    | e com.        |                                                                                                                                               |

| .user.     | atlassian | atlassian     |                                                                                                                                               |

| User,      | .user.    | .user.        |                                                                                                                                               |

| class      | User,     | User,         |                                                                                                                                               |

| java.      | class     | class         |                                                                                                                                               |

| lang.      | java.     | java.         |                                                                                                                                               |

| _          |           |               |                                                                                                                                               |

| String,    | lang.     | lang.         |                                                                                                                                               |

| class      | String,   | String,       |                                                                                                                                               |

| com.       | class     | class         |                                                                                                                                               |

| atlassian  | com.      | com.          |                                                                                                                                               |

|            | atlassian | atlassian     |                                                                                                                                               |

| confluen   |           |               |                                                                                                                                               |

| ce.core.   | confluen  | confluen      |                                                                                                                                               |

| Content    | ce.core.  | ce.core.      |                                                                                                                                               |

| EntityOb   | Content   | Content       |                                                                                                                                               |

| ject]      | EntityOb  | EntityOb      |                                                                                                                                               |

|            | ject]     | ject]         |                                                                                                                                               |

|            |           |               |                                                                                                                                               |

|            |           |               |                                                                                                                                               |

| 2024-02-07 | V.71      | John Hartfiel | <ul> <li>Correction Maximum<br/>DDR Speed on Key<br/>features according<br/>AMD Datasheet (still<br/>depends assembled<br/>ZynqMP)</li> </ul> |

| 2023-10-24 | v.69      | John Hartfiel | Correction Overview<br>Picture GTH B2B<br>connection                                                                                          |

| 2023-07-05 | v.68 | Vadim Yunitski                                                                                                                                                                   | <ul> <li>Updated table<br/>"CPLD Pin<br/>Connections": added<br/>signals EN_SOM<br/>and PG_SOM;<br/>SC_EXT_1 and<br/>SC_EXT_4 removed.</li> <li>Updated table<br/>"Controller signals":<br/>PG_VCCINT and<br/>EN_VCCINT<br/>replaced by<br/>PG_SOM and<br/>EN_SOM.<br/>Description updated<br/>respectivelly</li> <li>Block diagram<br/>updated: added<br/>PG_SOM and<br/>EN_SOM;<br/>SC_EXT_1 and<br/>SC_EXT_4 removed.</li> </ul> |

|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2022-10-17 | v.67 | JH                                                                                                                                                                               | Update link to the download area                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2022-05-30 | v.66 | ED                                                                                                                                                                               | Update to the latest version                                                                                                                                                                                                                                                                                                                                                                                                        |

|            | all  | Error<br>renderi<br>ng<br>macro<br>'page-<br>info'<br>Ambiguo<br>us<br>method<br>overload<br>ing for<br>method<br>jdk.<br>proxy27<br>9.\$Proxy<br>4022#ha<br>sConten<br>tLevelPe | •                                                                                                                                                                                                                                                                                                                                                                                                                                   |

rmission Cannot resolve which method to invoke for [null, class java. lang. String, class com. atlassian confluen ce. pages. Page] due to overlapp ing prototyp es between [interfac e com. atlassian confluen ce.user. Conflue nceUser , class java. lang.

Document change history.

# Disclaimer

## **Data Privacy**

Please also note our data protection declaration at https://www.trenz-electronic.de/en/Data-protection-Privacy

## **Document Warranty**

The material contained in this document is provided "as is" and is subject to being changed at any time without notice. Trenz Electronic does not warrant the accuracy and completeness of the materials in this document. Further, to the maximum extent permitted by applicable law, Trenz Electronic disclaims all warranties, either express or implied, with regard to this document and any information contained herein, including but not limited to the implied warranties of merchantability, fitness for a particular purpose or non infringement of intellectual property. Trenz Electronic shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein.

## **Limitation of Liability**

In no event will Trenz Electronic, its suppliers, or other third parties mentioned in this document be liable for any damages whatsoever (including, without limitation, those resulting from lost profits, lost data or business interruption) arising out of the use, inability to use, or the results of use of this document, any documents linked to this document, or the materials or information contained at any or all such documents. If your use of the materials or information from this document results in the need for servicing, repair or correction of equipment or data, you assume all costs thereof.

## **Copyright Notice**

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Trenz Electronic.

## **Technology Licenses**

The hardware / firmware / software described in this document are furnished under a license and may be used /modified / copied only in accordance with the terms of such license.

### **Environmental Protection**

To confront directly with the responsibility toward the environment, the global community and eventually also oneself. Such a resolution should be integral part not only of everybody's life. Also enterprises shall be conscious of their social responsibility and contribute to the preservation of our common living space. That is why Trenz Electronic invests in the protection of our Environment.

### **REACH, RoHS and WEEE**

#### REACH

Trenz Electronic is a manufacturer and a distributor of electronic products. It is therefore a so called downstream user in the sense of REACH. The products we supply to you are solely non-chemical products (goods). Moreover and under normal and reasonably foreseeable circumstances of application, the goods supplied to you shall not release any substance. For that, Trenz Electronic is obliged to neither register nor to provide safety data sheet. According to present knowledge and to best of our knowledge, no SVHC (Substances of Very High Concern) on the Candidate List are contained in our products. Furthermore, we will immediately and unsolicited inform our customers in compliance with REACH - Article 33 if any substance present in our goods (above a concentration of 0,1 % weight by weight) will be classified as SVHC by the European Chemicals Agency (ECHA).

#### RoHS

Trenz Electronic GmbH herewith declares that all its products are developed, manufactured and distributed RoHS compliant.

WEEE

Information for users within the European Union in accordance with Directive 2002/96/EC of the European Parliament and of the Council of 27 January 2003 on waste electrical and electronic equipment (WEEE).

Users of electrical and electronic equipment in private households are required not to dispose of waste electrical and electronic equipment as unsorted municipal waste and to collect such waste electrical and electronic equipment separately. By the 13 August 2005, Member States shall have ensured that systems are set up allowing final holders and distributors to return waste electrical and electronic equipment at least free of charge. Member States shall ensure the availability and accessibility of the necessary collection facilities. Separate collection is the precondition to ensure specific treatment and recycling of waste electrical and electronic equipment and is necessary to achieve the chosen level of protection of human health and the environment in the European Union. Consumers have to actively contribute to the success of such collection and the return of waste electrical and electronic equipment. Presence of hazardous substances in electrical and electronic equipment results in potential effects on the environment and human health. The symbol consisting of the crossed-out wheeled bin indicates separate collection for waste electrical and electronic equipment.

Trenz Electronic is registered under WEEE-Reg.-Nr. DE97922676.

#### Error rendering macro 'page-info'

Ambiguous method overloading for method jdk. proxy279.\$Proxy4022#hasContentLevelPermission. Cannot resolve which method to invoke for [null, class java.lang.String, class com.atlassian.confluence.pages.Page] due to overlapping prototypes between: [interface com.atlassian.confluence.user. ConfluenceUser, class java.lang.String, class com.atlassian.confluence.core. ContentEntityObject] [interface com.atlassian.user.User, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject]