# AVN-20220429 Problems with PCIe on TEBF0808 with TE080x

#### Download PDF version of this document.

| Company    | Trenz Electronic GmbH                                                 |

|------------|-----------------------------------------------------------------------|

| AVN Number | AVN-20220429                                                          |

| Title      | AVN-20220429 Problems with PCIe                                       |

| Subject    | Information and remedy concerning problematic with PCIe (SoC as Host) |

| Issue Date | 2022-04-29                                                            |

## **Description:**

From time to time problems with PCIe on some TEBF0808/TE080x combinations are reported. The problems can have various causes and are usually one or a combination of the following:

- 72992 Design Advisory for Zynq UltraScale+ MPSoC/RFSoC: Possible link training failures or data errors on PCIe, SATA, or USB 3.0 protocol links using PS GTR

- Xilinx provides patches for older Vivado Versions, Vivado 2021.1 or newer should be fixed (Status 22.03.22 Xilinx has changed this one time, so please check always AR#72992)

- TE080x PCIe Reference Clock initialisation will be done mostly via I2C on FSBL. Xilinx provides custom access on FSBL after MIO and GTR

initialisation. PLL initialisation before GTR initialisation will improve the initialisation of the link:

- Trenz Electronic provides special FSBL inside Xilinx PSU (between MIO initialisation and GTR initialisation) to solve this problem. This is done since Vivado 18.3 reference design releases.

- Alignment Problems with SS5, ST5 connectors, which can cause connection problems:

- $^{\circ}\;$  Trenz Electronic has improved production to minimize tolerances.

- Trenz Electronic starts to publish new Series TE081X which has same functionality but uses ADM6 connectors, which have very good self alignment capabilities.

- PCle Reference CLK can cause problem with PCle:

- SoC/FPGA side: Xilinx GTR reference CLK supports LVDS/LVPECL. PLL will be configured with correct LVDS standard on Trenz Reference Designs. In case of custom carrier and external reference clock, see also Xilinx ARx43641.

- PCIe Card side: PCIe requires HCSL IO or similar standard. Currently on the TEBF0808 AC coupled LVDS is used, which is generated

by the PLL of the module. However, the PLLs (SI5338 of SI5345) also support HCSL. SI5338 has internal termination and SI5345

require external termination for HCSL.

- Trenz plan to update TEBF0808 to revision 05 with LVDS to HCSL multiplexer.

- For older Revisions, still use LVDS or in case of TE0803, it's possibke to archive better results when the PLL is changed to HCSL and the capacitors on the carrier are replaced by 00hm resistors in case.

### **Products Affected**

This AVN affects all Trenz Electronic TEBF0808 together with compatible SoMs: TE080x.

| Affected Product | Effected Changes                     |

|------------------|--------------------------------------|

| TEBF0808-*       | #2 (use together with #1 on module!) |

| TE0808-*         | #1                                   |

| TE0807-*         | #1                                   |

| TE0803-*         | #1                                   |

#### **Advices**

#### #1 Use HSCL standard for PCIe CLK

Type: Improvement

Reason: HSCL standard is more in compliance with PCIe specification and will improve PCIe stability.

Impact: Carrier which still use AC coupled reference CLK for PCIe on the carrier are recommended to be modify, see #2. Changes will be implemented in newer reference designs (2021.2 or newer)

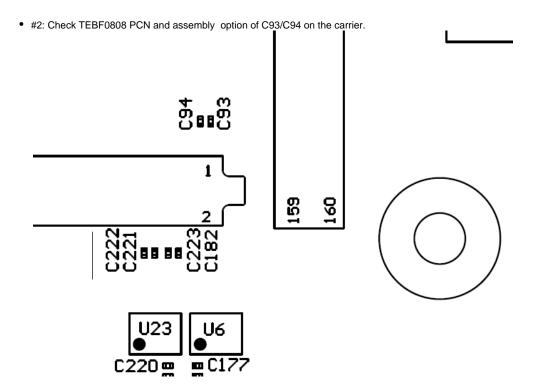

## #2 Replace C93 and C94 by 00hm resistor

Type: Improvement

Reason: DC coupled HSCL standard is more in compliance with PCIe specification and will improve PCIe stability. Capacitor C93 and C94 of PCI\_REF\_\*

/CLK0 \* should be replaced with 00hm resistor

Impact: Design which still use LVDS as PLL output for PCIe CLK to the carrier are recommended to be configured to use HSCL, see #1.

#### Method of Identification

· #1: Check PLL project files of your design TE0808/TE0807: CB Si5345-RevB-808-B-Project - ClockBuilder Pro ClockBuilder Pro v4.3 . Confi Step 9 of 16 - Output Clocks ▼ Disabled N Divider / DCO / ZDM Output Mode State Format Frequency Enabled 🔽 Stop Low HCSL 1.8 V 100 MHz Auto 🔽 🤡 TE0803: CB Si5338-RevB-Project - ClockBuilder Pro ClockBuilderPro 🟎 🗫 Step 6 of 8 - Output Driver ▼ Disabled Format State Output Frequency CLK0 100 MHz HCSL 1.8V Stop Low

## **Contact Information**

If you have any questions related to this AVN, please contact Trenz Electronics Technical Support at

- forum.trenz-electronic.de

- wiki.trenz-electronic.de

- support%trenz-electronic.de (subject = AVN-22220429)

- phone

- o national calls: 05741 3200-0

- o international calls: 0049 5741 3200-0

## Disclaimer

Any projected dates in this AVN are based on the most current product information at the time this AVN is being issued, but they may change due to unforeseen circumstances. For the latest schedule and any other information, please contact your local Trenz Electronic sales office, technical support or local distributor.

This AVN follows JEDEC Standard J-STD-046.