# **TE0722-Recovery**

#### **Short Description**

TE0722 does boot always from SPI Flash, changing the Boot Mode is not possible from any of the accessible connector or switches.

If TE0722 SPI Flash is accidentally programmed with Boot.bin that includes a FSBL that is not adapter for TE0722 DDR-less operation then ZYNQ Boot-ROM will not release JTAG DAP, and access to JTAG including reprogramming the SPI Flash is no longer possible.

Xilinx tools do not handle DDR-Less Design FSBL autogeneration correctly. To get around this problem manual modifications are necessary, see DDR less ZYNQ Design.

## Procedure

∕∄\

For this case, you can try the following steps without guarantee for success:

- 1. Close all Xilinx Programs

- 2. Power off TE0722

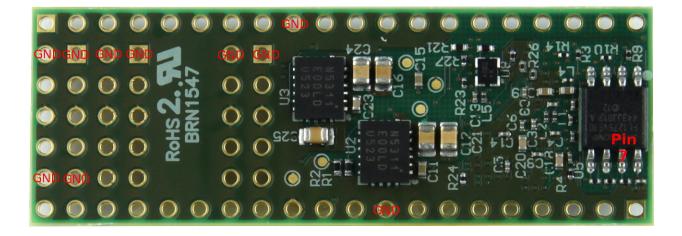

- 3. Bridge S25FL127S Pin 7 temporary with GND to change Boot Mode to JTAG Boot Mode only (See picture).

- 4. Power on TE0722

- 5. Disconnect the GND bridge wire from Pin 7

- 6. Open SDK

- 7. Program Flash with valid Boot.Bin, if programming failed try again from step 1.

## Changing bootmode

The easiest way to change the Boot Mode pinstrap is temporary connection of SPI Flash Pin 7 to ground. This pin connected with Pullup-Resistor to 3.3V, to set FPGA in Quad-SPI Mode. Shorting this Pin with GND will enable JTAG Boot Mode.

Connect Pin 7 to one of the GND Pins (Temporary during powerup). After startup, Pin 7 trace is used to program the Flash, so it must be floated (disconnected from ground).

#### References

- Zynq-7000 All Programmable SoC Technical Reference Manual (UG585):Page 167-Section 6.25 Boot Mode Pin Settings

TE0722 Schematics:TE0722 Download Page