## **AMD Development Tools**

The Vivado® Design Suite delivers a SoC-strength, IP-centric and system-centric, next generation development environment that has been built from the ground up to address the productivity bottlenecks in system-level integration and implementation. The Vivado Design suite is **a Generation Ahead** in overall productivity, ease-of-use, and system level integration capabilities.

Vivado is recommended for all Trenz Electronics products that are based on AMD 7 or UltraScale+ series. Trenz Electronics supplies Vivado Board Part Files for all products supported by Vivado.

#### Table of contents

- Table of contents

- Additional Trenz Electronic Description

- AMD Software Product Update Release Notes and Known Issues

- AMD Devices Erratas and solutions

- AMD Devices Solution Center

- AMD Software Basic User Guides

- AMD Wiki

- AMD Software Programming and Debugging

- Excerpt of AMD User Guides

### Additional Trenz Electronic Description

Expand all Collapse all

### AMD Software - Product Update Release Notes and Known Issues

| Version               | Vivado                           | SDK/Vitis                        | PetaLinux        |

|-----------------------|----------------------------------|----------------------------------|------------------|

| 2023.2                | AMD Vivado-2023-Known-Issues     | AMD Vitis-2023-Known-Issues***** | AMD AR#000035572 |

| 2022.2                | AMD Vivado-2022-Known-Issues     | AMD Vitis-2022-Known-Issues      | AMD AR#000034483 |

| 2021.2***,****        | *,**** AMD AR#76539 AMD AR#76498 |                                  | AMD AR#000032521 |

| 2020.2                | AMD AR#75186                     | AMD AR#73646                     | AMD AR#75775     |

| 2019.2**              | AMD AR#72162                     | AMD AR#72773                     | AMD AR#72950     |

| 2018.3**              | AMD AR#70860                     | AMD AR#69697                     | AMD AR#71653     |

|                       | AMD AR#70862                     | AMD AR#66374                     |                  |

| 2018.2**              | AMD AR#70860                     | AMD AR#69697                     | AMD AR#71201     |

|                       | AMD AR#70862                     | AMD AR#66303                     |                  |

| 2017.4** AMD AR#68923 |                                  | AMD AR#69697                     | AMD AR#70277     |

|                       | AMD AR#68925                     |                                  |                  |

| 2017.3*,**            | AMD AR#68923                     | AMD AR#70101                     | AMD AR#69952     |

|                       | AMD AR#68925                     | AMD AR#69697                     |                  |

| 2017.2*             | AMD AR#68923 | AMD AR#69699 | AMD AR#69372 |

|---------------------|--------------|--------------|--------------|

|                     | AMD AR#68925 | AMD AR#69697 |              |

| 2017.1*             | AMD AR#68923 | AMD AR#69698 | AMD AR#69074 |

|                     | AMD AR#68925 | AMD AR#69697 |              |

| 2016.4              | AMD AR#66830 |              | AMD AR#68370 |

| 2016.2 AMD AR#66830 |              | AMD AR#66230 | AMD AR#67409 |

Note: \* AR# 69908: 2017.1...3 - Vivado does not launch with Windows 10 Fall Creators Update

\*\* AR#70146: QSPI flash programming now requires that you specify an FSBL, AR#70548: Zynq-7000 - QSPI programming in QSPI-boot mode -

Trenz Electronic will provide special FSBL on 2017.4 an newer reference design.

\*\*\* Incompatibility of board files for ZyngMP with eMMC activated between 2021.2 and 2021.2.1 patch, see AMD Forum Request

\*\*\*\* Since 2021.2, AMD add Versal to Vivado as default installation. In case Versal is not used, Vivado installation size can be reduced around

40GB, when this folder will be deleted: C:\xilinx\Vivado\2021.2\data\parts\xilinx\devint\vault

\*\*\*\*\* With 2023.2 AMD changed Vitis to Vitis Unified IDE and renamed older IDE to Vitis Classic IDE. The Vitis Classic IDE will still be delivered with 23.2 but will probably be discontinued in the longer term.

### AMD Devices - Erratas and solutions

| Device                 | AMDLink      | Note                                                  |

|------------------------|--------------|-------------------------------------------------------|

| UltraScale+ RFSoC      | EN#291 (PDF) | Zynq UltraScale+ RFSoC Production Errata              |

| UltraScale+ Zynq       | AMD AR#68750 | Zynq UltraScale+ MPSoC - Errata Work-around Solutions |

| Zynq-7000 AMD AR#55539 |              | Zynq-7000 SoC - Errata Work-around Solutions          |

| 7 Series               | AMD AR#46370 | AMD 7 Series FPGA Solution Center                     |

### AMD Devices - Solution Center

| Device            | AMD Link | Note                                       |

|-------------------|----------|--------------------------------------------|

| UltraScale+ Zynq  | AR#64375 | AMD Zynq UltraScale+ MPSoC Solution Center |

| Zynq-7000 AR#5251 |          | AMD Zynq-7000 SoC Solution Center          |

| 7 Series          | AR#46370 | AMD 7 Series FPGA Solution Center          |

AMD Software - Basic User Guides

It's recommended to use AMDDocumentation Navigator (DocNav) to get access to all documentation of AMD with "Up to Date Catalog" of DocNav. Documents can be found easy by "DOC ID" via search function of the catalog view. Search documents on Web is also possible, but ensure to use the appropriate document version to your installed AMD software.

#### **AMD Wiki**

https://xilinx-wiki.atlassian.net/wiki/spaces/A/overview

## **AMD Software Programming and Debugging**

| Devices                            | Name                                                                      | DOC<br>ID | Description                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------|---------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| All                                | Vivado Design Suite User<br>Guide: Programming and<br>Debugging           | UG908     | Documents Vivado® tools for programming and debugging a AMD® FPGA design. Programming the FPGA includes generating a bitstream file from the implemented design and downloading the file to the target device. Also describes how to debug a design including RTL simulation and in-system debugging.  Chapter 4: Programming the FPGA Device Chapter 6 (5 on older versions of this document): Programming Configuration Memory Devices |

| Zynq,<br>Artix, Kint<br>ex, Virtex | Vivado Design Suite<br>Tutorial: Embedded<br>Processor Hardware<br>Design | UG940     | Demonstrates building a Zynq®-7000 All Programmable SoC processor-based design and a Microblaze™ processor design in the Vivado® tools. Uses the Vivado IP integrator to build a design and then debug the design with the AMD® Software Development Kit (SDK) and the Vivado logic analyzer.  ■ Zynq, Lab1: Step 8: Run the Software Application  ■ MicroBlaze, Lab3: Step 10: Executing the Software Application on a KC705 Board      |

| ZynqMP Zynq UltraScale+ MPSoC: Embedded Design Tutorial UG120 9 Demonstrates building a Zynq UltraScale+ MPSoC processor-based embedded and the AMD® Software Development Kit. Provides a hands-on tutorial for effection of the Chapter 4: Debugging with SDK  • Chapter 4: Debugging with SDK • Chapter 5: Boot and Configuration |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

# **Excerpt of AMD User Guides**

| Category            | Name                                                                                   | DOC<br>ID | Description                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|----------------------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

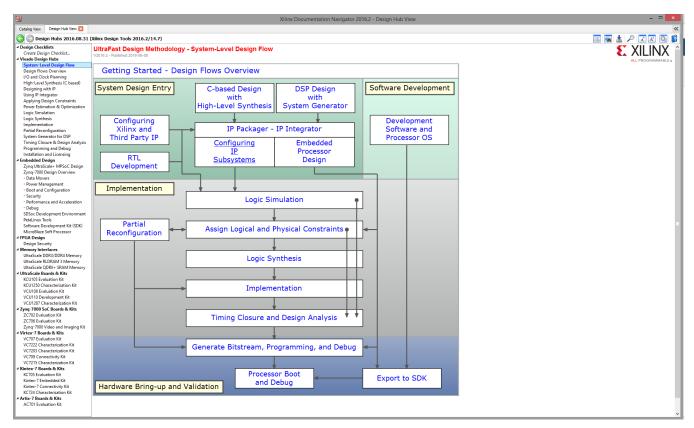

| Dev-Guide           | UltraFast Design<br>Methodology Guide for<br>the Vivado Design Suite                   | UG949     | Describes the recommended design methodology to achieve efficient utilization of AMD® FPGA device resources, and quicker design implementation and timing closure in Vivado® Design Suite. Provides the reasons behind the recommended method to support and enable informed design decisions.                                                                                     |

| Dev-Guide           | UltraFast Embedded<br>Design Methodology<br>Guide                                      | UG1046    | Describes the recommended design methodology for embedded designs using the Vivado® Design Suite and AMD SDK. Provides the reasons behind the recommended method to support and enable informed design decisions.                                                                                                                                                                  |

| Dev-Guide           | Vivado Design Suite<br>User Guide - Using the<br>Vivado IDE                            | UG893     | Describes the Vivado® Integrated Design Environment (IDE), providing an intuitive graphical user interface (GUI) to visualize and interact with an FPGA design. Describes how the Vivado IDE helps you configure tool options, analyze and refine timing, and floorplan a design to improve results.                                                                               |

| Dev-Guide           | Vivado Design Suite<br>User Guide - Embedded<br>Processor Hardware<br>Design           | UG898     | Discusses using the Vivado IP Integrator and AMD Software Development Kit (SDK) to design and debug microprocessor-based systems and embedded software applications using the Zynq®-7000 All Programmable (AP) SoC, Zynq UltraScale+™ MPSoC, or the MicroBlaze™ processor.                                                                                                         |

| Dev-Guide           | Vitis Unified Software<br>Platform Documentation<br>- Embedded Software<br>Development | UG1400    | The Vitis™ integrated development environment (IDE) is part of the Vitis unified software platform. The Vitis IDE is designed to be used for the development of embedded software applications targeted towards AMD® embedded processors. The Vitis IDE works with hardware designs created with Vivado® Design Suite. The Vitis IDE is based on the Eclipse open source standard. |

| Dev-Guide<br>ZYNQMP | Zynq<br>UltraScale+MPSoC<br>Software Developer<br>Guide                                | UG1137    | This document provides the software-centric information required for designing and developing system software and applications for the AMD® Zynq® UltraScale+™ MPSoC devices.                                                                                                                                                                                                      |

| Dev-Guide<br>ZYNQ   | Zynq-7000 All<br>Programmable SoC<br>Software Developers<br>Guide                      | UG821     | This document summarizes the software-centric information required for designing with AMD ® Zynq ® -7000 All Programmable SoC devices                                                                                                                                                                                                                                              |

| ZYNQ                | Zynq Migration Guide -<br>Zynq-7000 AP SoC to<br>Zynq UltraScale+<br>MPSoC Devices     | UG1213    | Summarizes the migration process from the AMD® Zynq®-7000 device to the Zynq UtlraScale+™ MPSoC device.                                                                                                                                                                                                                                                                            |

| ZYNQ                | Zynq-7000 All<br>Programmable SoC -<br>Technical Reference<br>Manual                   | UG585     | Technical reference manual for the Zynq®-7000 All Programmable SoC.                                                                                                                                                                                                                                                                                                                |

| ZYNQMP              | Zynq UltraScale+<br>MPSoC TRM                                                          | UG1085    | Describes the processing system in the Zynq® UltraScale+™ MPSoC including the Cortex®-A53 64-bit quad-core processor and Cortex-R5 dual-core realtime processor.                                                                                                                                                                                                                   |

A selection of AMD Answer Records are available on AMD Answer Record