### **TE0820 CPLD**

#### Table of contents

#### **Overview** 1 Overview

Foverview

CPLD Device with design and supported PCB Revision

2 Product Specification

2 Product Specificatio

- Boot Mode settings 3 Power

- LED

- 2.2.4 LED

2.2.5 I2C interface

2.2.6 NOSEQ pin

# 2.2.6 NOSEQ pin Firmware<sup>3</sup> Revision Part Supported PCB Revision 3.1 Revision Changes See Document Scale United Change History 4 Appx. B: Legal Notices 4.4 Data Brivage

- 4.1 Data Privacy

## • 4.4 Copyright Notice

4.5 Technology Licenses

Port Dest Protection 4.7 REACH, RoHS and WEEE

5 Table of co

| Name /<br>opt. VHD<br>Name | Direction | Pin | Pullup<br>/Down | Bank<br>Power | Description | Note:<br>PCB<br>REV04<br>REV05<br>Connection | Note:<br>PCB<br>REV01<br>REV02<br>Connection |

|----------------------------|-----------|-----|-----------------|---------------|-------------|----------------------------------------------|----------------------------------------------|

| C_TCK                      | in        | 30  | DOWN            | 3.3VIN        | JTAG B2B    |                                              |                                              |

| C_TDI                      | in        | 32  | DOWN            | 3.3VIN        | JTAG B2B    |                                              |                                              |

| C_TDO                      | out       | 1   | DOWN            | 3.3VIN        | JTAG B2B    |                                              |                                              |

| C_TMS                      | in        | 29  | DOWN            | 3.3VIN        | JTAG B2B    |                                              |                                              |

| RST_EN   | inout | 27 | NONE | 3.3VIN | Reset pin<br>output to<br>reset FPGA<br>via CPLD chip                                                                  | For PCB<br>REV04 EN1<br>(input) (pulled<br>up in CPLD) /<br>For PCB<br>REV05<br>REST_EN<br>(output)<br>(Floating in<br>CPLD)<br>Power<br>Enable from<br>B2B                                                                                                                                                                              |                                             |

|----------|-------|----|------|--------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

|          |       |    |      |        |                                                                                                                        | Connector<br>(Positive<br>Enable)<br>(input pin) for<br>PCB revision<br>O4 in this<br>case used<br>only for<br>PGOOD<br>feedback /<br>Reset<br>pin (output<br>pin) for PCB<br>revision 5 in<br>this case this<br>pin is reset<br>pin that is<br>activated by<br>firmware and<br>not by<br>hardware<br>after<br>changing the<br>boot mode |                                             |

| User_LED | out   | 4  | NONE | 3.3VIN | user defined<br>or status, see<br>LED<br>description                                                                   | For PCB<br>REV04<br>shows the<br>state of X1<br>and X0. / For<br>PCB REV05<br>shows the<br>boot mode<br>state for<br>selection via<br>hardware<br>(Dip switch in<br>carrier board)<br>or via<br>software<br>(related<br>command in<br>linux console<br>or FSBL<br>code)                                                                  | 1.8V input<br>ERR_OUT(P<br>S_ERROR_O<br>UT) |

| PG_ALL   | in    | 5  | NONE | 3.3VIN | This pin is<br>used as<br>power good<br>(input)                                                                        | Unused in<br>CPLD<br>firmware for<br>PCB REV04(<br>In hardware<br>is pulled up) /<br>Used in PCB<br>REV05 as<br>power<br>good input<br>pin                                                                                                                                                                                               | 1.8V input<br>ERR_STATU<br>S as input       |

| JTAGEN   | in    | 26 |      | 3.3VIN | Enable JTAG<br>access to<br>CPLD for<br>Firmware<br>update (zero:<br>JTAG routed<br>to module,<br>one: CPLD<br>access) |                                                                                                                                                                                                                                                                                                                                          |                                             |

| MODE     | in    | 25 | UP   | 3.3VIN  | Boot Mode<br>for Zynq<br>/ZynqMP<br>Devices<br>(Flash or SD)                                                                                                                                                                 |                                                                                                                                                     |                                                                                                                         |

|----------|-------|----|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| MODE0    | out   | 12 | DOWN | 1.8V    | ZynqMP Boot<br>Mode Pin 0                                                                                                                                                                                                    |                                                                                                                                                     |                                                                                                                         |

| MODE1    | out   | 13 | DOWN | 1.8V    | ZynqMP Boot<br>Mode Pin 1                                                                                                                                                                                                    |                                                                                                                                                     |                                                                                                                         |

| MODE2    | out   | 14 | DOWN | 1.8V    | ZynqMP Boot<br>Mode Pin 2                                                                                                                                                                                                    |                                                                                                                                                     |                                                                                                                         |

| MODE3    | out   | 16 | DOWN | 1.8V    | ZynqMP Boot<br>Mode Pin 3                                                                                                                                                                                                    |                                                                                                                                                     |                                                                                                                         |

| NOSEQ    | inout | 23 | UP   | 3.3VIN  | Usage CPLD<br>Variant<br>depends                                                                                                                                                                                             | Used as<br>GPIO pin by<br>user. This pin<br>can be<br>written or<br>read via<br>i2cset<br>command in<br>linux console<br>or FSBI code<br>functions. | Used as boot<br>mode<br>selection pin,<br>if CPLD is<br>programmed<br>using<br>SC0820_qspi<br>_sd_jtag.jed<br>jed-file. |

| PGOOD    | inout | 28 | UP   | 3.3VIN  | Module<br>Power Good<br>(only<br>Feedback<br>from EN1 for<br>PCB revision<br>4 or older). /<br>For PCB<br>revision 5 is<br>used as boot<br>mode<br>selection pin<br>or power<br>good pin<br>(feedback<br>from PG_ALL<br>pin) | Module<br>Power Good<br>(only<br>Feedback<br>from EN1 for<br>PCB revision<br>4 or older). /<br>Boot mode<br>selection pin<br>for PCB<br>REV05       |                                                                                                                         |

| PHY_LED1 | in    | 17 |      | 1.8V    | ETH PHY<br>LED1 / curren<br>tly_not_used                                                                                                                                                                                     |                                                                                                                                                     |                                                                                                                         |

| тск      | out   | 9  | DOWN | 1.8V    | JTAG<br>ZynqMP                                                                                                                                                                                                               |                                                                                                                                                     |                                                                                                                         |

| TDI      | out   | 8  | DOWN | 1.8V    | JTAG<br>ZynqMP                                                                                                                                                                                                               |                                                                                                                                                     |                                                                                                                         |

| TDO      | in    | 10 | DOWN | 1.8V    | JTAG<br>ZynqMP                                                                                                                                                                                                               |                                                                                                                                                     |                                                                                                                         |

| TMS      | out   | 11 | DOWN | 1.8V    | JTAG<br>ZynqMP                                                                                                                                                                                                               |                                                                                                                                                     |                                                                                                                         |

| XO       | in    | 20 | UP   | VCCO_65 | I2C SCL pin                                                                                                                                                                                                                  | Used as tri-<br>state enable-<br>input for<br>User_LED<br>pin for PCB<br>REV04 /<br>Used as i2c<br>SCL pin for<br>PCB REV05                         |                                                                                                                         |

| X1       | inout | 21 | UP   | VCCO_65 | I2C SDA pin                                                                                                                                                                                                                  | Used as tri-<br>state<br>input for<br>User_LED<br>pin for PCB<br>REV04 /<br>Used as i2c<br>SDA pin for<br>PCB REV05                                 |                                                                                                                         |

#### **Functional Description**

#### **JTAG**

JTAG signals routed directly through the CPLD to FPGA. Access between CPLD and FPGA can be multiplexed via JTAGEN (logical one for CPLD, logical zero for FPGA) on JM1-89.

#### **Boot Mode**

Boot mode can be set either by hardware (dip-switch) on the carrier board or by firmware in linux console or FSBL code. Even after booting boot mode can be changed . After changing the boot mode FPGA is restarted automatically by CPLD, if PCB revision is REV05, otherwise for PCB revision 4 user must reset manually to execute boot mode changing correctly. To change boot mode a state machine continuously monitors the corresponding register that can be change via I2C interface between CPLD and FPGA.

| Change method | Boot Mode | CPLD PGOOD<br>Pin (B2B Pin<br>JM1-30) | CPLD MODE<br>Pin (B2B Pin<br>JM1-32) | Description |

|---------------|-----------|---------------------------------------|--------------------------------------|-------------|

| Hardware      | JTAG      | 0                                     | 0                                    |             |

| Hardware      | eMMC      | 0                                     | 1                                    |             |

| Hardware      | SD Card   | 1                                     | 0                                    |             |

| Hardware      | QSPI      | 1                                     | 1                                    |             |

| Change method | Boot Mode | Command in<br>linux console   | Command in<br>FSBL                 | Description                                             |

|---------------|-----------|-------------------------------|------------------------------------|---------------------------------------------------------|

| Software      | JTAG      | i2cset -y 1<br>0x20 0x01 0x91 | iic_write8<br>(0x20,0x01,<br>0x91) | 0x20 is device<br>address. 0x01 is<br>register address. |

| Software      | SD Card   | i2cset -y 1<br>0x20 0x01 0x93 | iic_write8<br>(0x20,0x01,<br>0x93) | 0x20 is device<br>address. 0x01 is<br>register address. |

| Software      | QSPI      | i2cset -y 1<br>0x20 0x01 0x92 | iic_write8<br>(0x20,0x01,<br>0x92) | 0x20 is device<br>address. 0x01 is<br>register address. |

| Software      | eMMC      | i2cset -y 1<br>0x20 0x01 0x90 | iic_write8<br>(0x20,0x01,<br>0x90) | 0x20 is device<br>address. 0x01 is<br>register address. |

If PCB revision is REV04, then user must reset manually the carrier board after changing the boot mode using i2cset command in linux console. If PCB revision is REV05, it is not necessary to reset the FPGA by user, because FPGA will be reset automatically via CPLD after changing the boot mode via i2cset command in linux console.

For other UltraScale+ Boot Modes options custom firmware is needed, see also Table 11.1 Boot Modes from Xilinx UG1085.

#### **Power**

For PCB revision 4 or older PGOOD depends on EN1. There is no additional power management controlled by CPLD. For PCB revision 5 PGOOD depends on PG\_ALL signal.

#### LED

Green LED D2 glows depending on boot mode and whether boot mode is selected by hardware or firmware.

| LED state               | Condition                                                        | Related command                                                 | Description   |

|-------------------------|------------------------------------------------------------------|-----------------------------------------------------------------|---------------|

| OFF                     | JTAG boot mode and<br>software boot mode<br>selection not active | Boot mode is adjusted by<br>dip switch on the carrier<br>board. | CPLD_BM = '0' |

| Blink sequence *ooooooo | QSPI boot mode and<br>software boot mode<br>selection not active | Boot mode is adjusted by<br>dip switch on the carrier<br>board. | CPLD_BM = '0' |

| Blink sequence **oooooo | eMMC boot mode and<br>software boot mode<br>selection not active | Boot mode is adjusted by<br>dip switch on the carrier<br>board. | CPLD_BM = '0' |

| Blink sequence ***ooooo | SD card boot mode and software boot mode selection not active    | Boot mode is adjusted by<br>dip switch on the carrier<br>board. | CPLD_BM = '0' |

| Blink sequence ****oooo | JTAG boot mode and<br>software boot mode<br>selection active     | i2cset -y 1 0x20<br>0x01 0x91 in<br>linux console               | CPLD_BM = '1' |

| Blink sequence *****ooo | QSPI boot mode and<br>software boot mode<br>selection active     | i2cset -y 1 0x20<br>0x01 0x92 in<br>linux console               | CPLD_BM = '1' |

| Blink sequence *******  | eMMC boot mode and<br>software boot mode<br>selection active     | i2cset -y 1 0x20<br>0x01 0x93 in<br>linux console               | CPLD_BM = '1' |

| ON                      | SD card boot mode and software boot mode selection active        | i2cset -y 1 0x20<br>0x01 0x90 in<br>linux console               | CPLD_BM = '1' |

Note: asterisk mean one blink. So for example \*\*oooooo mean 2 time blink with a longer break(with the time of 6 blinks)

#### **I2C interface**

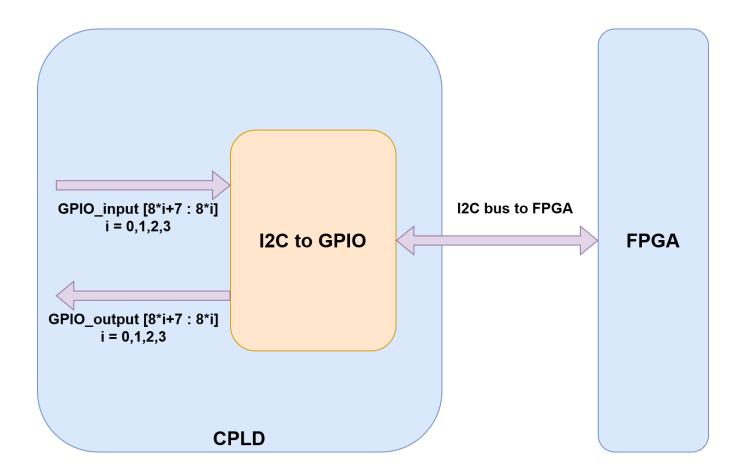

CPLD firmware consists of a i2c t GPIO block. This subsystem provides i2c protocol interface to 32-bit (4 x 8-bit) (GPIO\_input[31:0]) registers for reading from CPLD and (4 x 8-bit) (GPIO\_output[31:0]) registers for writing in CPLD as general purpose parallel input and output (I/Os). The written and read data is communicated from/to FPGA via i2c bus interface protocol. The address of this block in the firmware is 0x20.In this case related i2c bus is bus 1.

| Register           | Direction in CPLD          | Address |

|--------------------|----------------------------|---------|

| GPIO_input[7:0]    | Output (reading from CPLD) | 0x00    |

| GPIO_input[15:8]   | Output (reading from CPLD) | 0x01    |

| GPIO_input[23:16]  | Output (reading from CPLD) | 0x02    |

| GPIO_input[31:24]  | Output (reading from CPLD) | 0x03    |

| GPIO_output[7:0]   | Input (writing to CPLD)    | 0x00    |

| GPIO_output[15:8]  | Input (writing to CPLD)    | 0x01    |

| GPIO_output[23:16] | Input (writing to CPLD)    | 0x02    |

| GPIO_output[31:24] | Input (writing to CPLD)    | 0x03    |

#### **NOSEQ** pin

This pin in PCB REV04 with old CPLD firmware version (REV04) is used as boot mode pin select. If CPLD is programmed with SC0820\_qspi\_sd\_jtag.jed as jed file and NOSEQ is high, JTAG boot mode will be selected. For PCB REV05 or PCB REV04 with new CPLD firmware (CPLD firmware REV05) NOSEQ pin can be used by user as GPIO pin and accessed via i2c interface. In this case the following table can be used:

| NOSEQ pin as output        | Condition              | Command in linux console      |

|----------------------------|------------------------|-------------------------------|

| 41                         | GPIO_output(16) = '1'  | i2cset -y 1 0x20 0x02<br>0x01 |

| '0'                        | GPIO_output(16) = '0'  | i2cset -y 1 0x20 0x02<br>0x00 |

| NOSEQ pin as input         | Description            | Command in linux console      |

| Reading state of NOSEQ pin | GPIO_input(16) = NOSEQ | i2cget -y 1 0x20 0x02         |

#### Access to CPLD Registers

CPLD registers can be accessed via i2c interface. In the following table is shown how these registers can be read or written:

| Register           | Direction in CPLD          | Address | Related instruction in<br>linux console to<br>access the register |

|--------------------|----------------------------|---------|-------------------------------------------------------------------|

| GPIO_input[7:0]    | Output (reading from CPLD) | 0x00    | i2cget -y 1 0x20 0x00                                             |

| GPIO_input[15:8]   | Output (reading from CPLD) | 0x01    | i2cget -y 1 0x20 0x01                                             |

| GPIO_input[23:16]  | Output (reading from CPLD) | 0x02    | i2cget -y 1 0x20 0x02                                             |

| GPIO_input[31:24]  | Output (reading from CPLD) | 0x03    | i2cget -y 1 0x20 0x03                                             |

| GPIO_output[7:0]   | Input (writing to CPLD)    | 0x00    | i2cset -y 1 0x20 0x00<br><data></data>                            |

| GPIO_output[15:8]  | Input (writing to CPLD)    | 0x01    | i2cset -y 1 0x20 0x01<br><data></data>                            |

| GPIO_output[23:16] | Input (writing to CPLD)    | 0x02    | i2cset -y 1 0x20 0x02<br><data></data>                            |

| GPIO_output[31:24] | Input (writing to CPLD)    | 0x03    | i2cset -y 1 0x20 0x03<br><data></data>                            |

Some of these registers are using to show some information same as CPLD revision and boot mode while booting.

| Register        | Address | related data           | Read/write by user | Description |

|-----------------|---------|------------------------|--------------------|-------------|

| GPIO_input[7:0] | 0x00    | CPLD REVISION (8 bits) | No                 |             |

| GPIO_input[15:8] | 0x01    | "00" &<br>BOOTMODE_GEN<br>(2 bits) & PUDC (1<br>bit) & CPLD_BM (1<br>bit) & BOOT_MODE<br>(2 bits) | No  | BOOTMODE_GEN<br>is a generic<br>parameter in<br>firmware code to<br>select type of jed-<br>file. For example if<br>this parameter is 3,<br>then by<br>programming the<br>related jed-file the<br>user can have all<br>boot mode options.<br>(QSPI/JTAG/SD<br>Card/eMMC).<br>PUDC is the state of<br>PUDC pin of FPGA.<br>CPLD_BM is a<br>parameter to show if<br>boot mode selection<br>is executed via<br>hardware (if low) or<br>software (if high)<br>BOOT_MODE<br>shows selected boot<br>mode. |

|------------------|---------|---------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO_input8[16]  | 0x02    | NOSEQ pin                                                                                         | Yes |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Register         | Address | related data                                                                                      |     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIO_output[16]  | 0x02    | NOSEQ pin                                                                                         | Yes |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

If CPLD firmware version is REV05, then boot mode, CPLD revision and some features of the board will be displayed in the linux console via FSBL code while booting. The format of these informations are shown in the following:

| Information                         | Displayed in Linux console             | Description                                                                                                                                                                                                |

|-------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPLD Revision                       | CPLD_REV = <cpld revision=""></cpld>   |                                                                                                                                                                                                            |

| Boot mode selection procedure       | CPLD_BM = < bm selection<br>procedure> | <ul> <li>If boot mode via hardware<br/>is selected Deactive(0)</li> <li>If boot mode via software<br/>(in linux console or via<br/>FSBL code) is selected<br/>Active(1)</li> </ul>                         |

| Jed file that on CPLD is programmed | BOOTMODE_GEN = < jed file<br>type>     | <ul> <li>Jed file type can be one of<br/>the following types :         <ul> <li>(0) QSPI/SD</li> <li>(1) QSPI/JTAG</li> <li>(2) JTAG/SD</li> <li>(3) default QSPI/JTAG<br/>/SD/eMMC</li> </ul> </li> </ul> |

| PUDC pin state                      | PUDC_MODE = <pudc state=""></pudc>     | <ul> <li>PUDC can have one of the following state:         <ul> <li>Pull-up activated (0)</li> <li>Pull-up deactivated (1)</li> </ul> </li> </ul>                                                          |

| Boot mode |  | The following boot modes<br>can displayed:<br>eMMC (0)<br>JTAG (1)<br>QSPI (2)<br>SD Card (3) |

|-----------|--|-----------------------------------------------------------------------------------------------|

|-----------|--|-----------------------------------------------------------------------------------------------|

The CPLD revision, boot mode and other informations will be displayed while booting as shown:

| TE0820 TE_XFsbl_BoardInit_Custom              |

|-----------------------------------------------|

| Initializing I2C Bus<br>Reading CPLD register |

| CPLD_REV=05                                   |

| CPLD_BM=Deactive(0)                           |

| BOOTHOD_GEN=3(default QSPI/JTAG/SD/eNMC)      |

| PUDC_MODE=Pull-up activated(0)                |

| BOOT_MODE=SD Card(3)                          |

|                                               |

| TE0830 TE_XTebl_HookAfterBSDownload_Custom    |

All information while booting

If PCB revision is REV04 and CPLD firmware version is older than REV05 (for example REV04), then it will not be displayed these informations same as boot mode while booting and the following message will be displayed:

| TE0820 TE XFabl HookAfter8SDownload_Custom<br>InitializIng I3C Bus                                                       |

|--------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                          |

|                                                                                                                          |

|                                                                                                                          |

|                                                                                                                          |

|                                                                                                                          |

| NOTICE: BL31: v2.4(release):xlnx_rebase_v2.4_2021.1_update1=23-g9100496b9<br>NOTICE: BL31: Built : 07:41:24, Oct 13 2021 |

|                                                                                                                          |

Message while booting if CPLD firmware version is old for PCB REV04

#### Appx. A: Change History

For PCB REV01 and REV02 Documentation available on: TE0820-REV01\_REV02 CPLD

#### **Revision Changes**

- REV04 to REV05

- ° Adding configuration of boot mode in linux console and via generic parameters

- PGOOD pin used as boot mode selector pin.

- Adding boot mode configuration via hardware

- JTAG time constraint correction

- Adding i2c to gpio ip (i2c\_slave.vhd)

- LED function is changed.

- New generic parameter defined : PCB\_REV

- ° EN1 pin

- is renamed to RST\_EN.

- pin is input for PCB\_REV=4 and it is enable pin same as before.

- is reset output for PCB\_REV=5 or newer.

- REV03 to REV04

- PCB REV03 support only

- X1 is input for USER LED

- X0 select X0 or Firmware Blink status to User LE

- blink modes for QSPI/SD firmware

- REV02 to REV03

- new Boot Mode variants

- new X0 status blink sequencingREV01 to REV02

- - Boot Mode variants

- X1

Remove ERR\_STATUS

#### **Document Change History**

To get content of older revision got to "Change History" of this page and select older document revision number.

| Date        | Document<br>Revision | CPLD<br>Firmware<br>Revision  | Supported<br>PCB Revision | Authors             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                           |

|-------------|----------------------|-------------------------------|---------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|             |                      | REV05                         | REV04,REV05               | Err                 | • add LED<br>Designator<br>pr renderinggaacro 'page-inf                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | o'                                                                        |

| Error       | re Error             | <b>geridéo</b> ing macro 'pag | ge-info'                  | Am                  | piguous method overloading fo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | or method jdk.proxy241.\$Proxy3496#hasContentLevell                       |

| Ambig       | u Ambig              | tirogi sometikthod d yekkpac  | biyg:4dr.\$Ræbbyd3}96¢hæ  | ĸ                   | ziQantizmbetreiSelveiszliách                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Gænlinod nesiolvekveltiont (moletholaists janvao kæntip Stimiolity, odæææ |

| 2022-10-05  | v.3                  | REV05                         | REV04,REV05               | Mohsen<br>Chamanbaz | <ul> <li>REV05<br/>release</li> <li>Firmware<br/>release for<br/>PCB REV04<br/>(SC-PCM-<br/>TE0820-<br/>04_SC820-<br/>05_2022100<br/>5_zip)</li> <li>Firmware<br/>release for<br/>PCB REV05<br/>(SC-PCM-<br/>TE0820-<br/>05_SC820-<br/>05_SC820-<br/>05_SC820-<br/>05_SC820-<br/>05_2022100<br/>5_zip)</li> <li>Firmware<br/>release ()</li> <li>Access to<br/>boot mode in<br/>linux console<br/>or FSBI code</li> <li>Indicating<br/>CPLD<br/>revision ,<br/>boot mode<br/>and PUDC<br/>state while<br/>booting</li> </ul> |                                                                           |

| 2018-08-29  | v.2                  | REV04                         | REV03                     | John Hartfiel       | • typo correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                           |

| 06 Jul 2018 | v.1                  | REV04                         | REV03                     | John Hartfiel       | Revision 04<br>finished     separate<br>page for<br>PCB REV01<br>and REV02                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |

| 06 Jul 2018 | v.1 | REV04 | REV03 |       | <ul> <li>Initial release</li> </ul> |                                                          |

|-------------|-----|-------|-------|-------|-------------------------------------|----------------------------------------------------------|

|             |     |       |       | Error | rendering macro 'pag                | ge-info'                                                 |

|             |     |       |       | Ambig | uous method overload                | ing for method jdk.proxy241.\$Proxy3496#hasContentLevell |

|             |     |       |       |       |                                     |                                                          |

|             | All |       |       |       |                                     |                                                          |

|             |     |       |       |       |                                     |                                                          |

|             |     |       |       | Error | rendering macro 'pag                | je-info'                                                 |

|             |     |       |       | Ambig | uous method overload                | ing for method jdk.proxy241.\$Proxy3496#hasContentLevell |

|             |     |       |       |       |                                     |                                                          |

#### Appx. B: Legal Notices

#### **Data Privacy**

Please also note our data protection declaration at https://www.trenz-electronic.de/en/Data-protection-Privacy

#### **Document Warranty**

The material contained in this document is provided "as is" and is subject to being changed at any time without notice. Trenz Electronic does not warrant the accuracy and completeness of the materials in this document. Further, to the maximum extent permitted by applicable law, Trenz Electronic disclaims all warranties, either express or implied, with regard to this document and any information contained herein, including but not limited to the implied warranties of merchantability, fitness for a particular purpose or non infringement of intellectual property. Trenz Electronic shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein.

#### **Limitation of Liability**

In no event will Trenz Electronic, its suppliers, or other third parties mentioned in this document be liable for any damages whatsoever (including, without limitation, those resulting from lost profits, lost data or business interruption) arising out of the use, inability to use, or the results of use of this document, any documents linked to this document, or the materials or information contained at any or all such documents. If your use of the materials or information from this document results in the need for servicing, repair or correction of equipment or data, you assume all costs thereof.

#### **Copyright Notice**

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Trenz Electronic.

#### **Technology Licenses**

The hardware / firmware / software described in this document are furnished under a license and may be used /modified / copied only in accordance with the terms of such license.

#### **Environmental Protection**

To confront directly with the responsibility toward the environment, the global community and eventually also oneself. Such a resolution should be integral part not only of everybody's life. Also enterprises shall be conscious of their social responsibility and contribute to the preservation of our common living space. That is why Trenz Electronic invests in the protection of our Environment.

#### **REACH, RoHS and WEEE**

#### REACH

Trenz Electronic is a manufacturer and a distributor of electronic products. It is therefore a so called downstream user in the sense of REACH. The products we supply to you are solely non-chemical products (goods). Moreover and under normal and reasonably foreseeable circumstances of application, the goods supplied to you shall not release any substance. For that, Trenz Electronic is obliged to neither register nor to provide safety data sheet. According to present knowledge and to best of our knowledge, no SVHC (Substances of Very High Concern) on the Candidate List are contained in our products. Furthermore, we will immediately and unsolicited inform our customers in compliance with REACH - Article 33 if any substance present in our goods (above a concentration of 0,1 % weight by weight) will be classified as SVHC by the European Chemicals Agency (ECHA).

#### RoHS

Trenz Electronic GmbH herewith declares that all its products are developed, manufactured and distributed RoHS compliant.

#### WEEE

Information for users within the European Union in accordance with Directive 2002/96/EC of the European Parliament and of the Council of 27 January 2003 on waste electrical and electronic equipment (WEEE).

Users of electrical and electronic equipment in private households are required not to dispose of waste electrical and electronic equipment as unsorted municipal waste and to collect such waste electrical and electronic equipment separately. By the 13 August 2005, Member States shall have ensured that systems are set up allowing final holders and distributors to return waste electrical and electronic equipment at least free of charge. Member States shall ensure the availability and accessibility of the necessary collection facilities. Separate collection is the precondition to ensure specific treatment and recycling of waste electrical and electronic equipment and is necessary to achieve the chosen level of protection of human health and the environment in the European Union. Consumers have to actively contribute to the success of such collection and the return of waste electrical and electronic equipment. Presence of hazardous substances in electrical and electronic equipment results in potential effects on the environment and human health. The symbol consisting of the crossed-out wheeled bin indicates separate collection for waste electrical and electronic equipment.

Trenz Electronic is registered under WEEE-Reg.-Nr. DE97922676.

Error rendering macro 'page-info'

Ambiguous method overloading for method jdk.

proxy241.\$Proxy3496#hasContentLevelPermission. Cannot resolve which method to invoke for [null, class java.lang.String, class com.atlassian.confluence.pages.Page] due to overlapping prototypes between: [interface com.atlassian.confluence.user. ConfluenceUser, class java.lang.String, class com.atlassian.confluence.core. ContentEntityObject] [interface com.atlassian.user.User, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject]