# **TEC0850 Getting Started**

## Overview

The Trenz Electronic TEC0850 is an industrial-grade MPSoC SoM integrating a Xilinx Zynq UltraScale+ MPSoC, with 64-bit wide SODIMM DDR4 SDRAM, max. Dual 512 MByte Flash memory for configuration and operation. 24 Gigabit transceivers on PL side and 4 PS side. Powerful switch-mode power supplies for all onboard voltages. A large number of configurable I/Os. 3U form factor.

## Power supply

Board takes power from J1E connector. Voltage is 12V maximum current 6.65A. See TEC0850 TRM for details.

## **DIP-Switches**

#### **S1**

| Switch | Description                                                       |

|--------|-------------------------------------------------------------------|

| 1      | SC JTAGEN (OFF: MAX 10, ON SoC)                                   |

| 2      | EEPROM WP (Write protect, ON active)                              |

| 3      | FPGA PUDC (ON: internal pull-up resistors enabled, OFF: floating) |

| 4      | SC Switch (Reserved for future use)                               |

#### **S2**

| Switch | Description |

|--------|-------------|

| 1      | Boot Mode 3 |

| 2      | Boot Mode 2 |

| 3      | Boot Mode 1 |

| 4      | Boot Mode 0 |

See Zynq UltraScale+ Device Technical Reference Manual page 236 for full boot modes description. Most common modes are

| Boot Mode      | SW2:1 | SW2:2 | SW2:3 | SW2:4 |

|----------------|-------|-------|-------|-------|

| JTAG Boot Mode | ON    | ON    | ON    | ON    |

| Quad-SPI       | ON    | ON    | OFF   | ON    |

| SD Card        | ON    | OFF   | ON    | OFF   |

## **LEDs**

| LED | Signal | Chip | Pin | Description |

|-----|--------|------|-----|-------------|

|-----|--------|------|-----|-------------|

| Front panel LED 1 (Red)   | LED_FP_1 | FPGA U1 | AF15 | PL User defined LED |

|---------------------------|----------|---------|------|---------------------|

| Front panel LED 2 (Green) | LED_FP_2 | FPGA U1 | AG15 | PL User defined LED |

| Front panel LED 3 (Green) | LED_FP_3 | FPGA U1 | AE15 | PL User defined LED |

| Front panel LED 4 (Green) | LED_FP_4 | SC U18  | M4   | Power Good          |

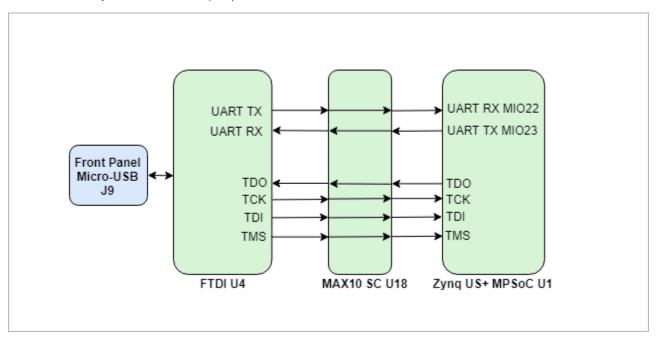

## JTAG/UART

Board has USB-UART bridge based on FTDI FT2232 chip. Use of this feature requires that USB driver is installed on your host PC. UART0 with MIO 22 .. 23 should be selected in "Zynq UltraScale+ MPSoC" configuration.

Connected device depends on JTAGEN DIP (S1-1)

# Reference Designs

TEC0850 Reference Designs

### **Notes**