# **TEC0850 TRM**

#### Download PDF version of this document.

#### **Table of Contents**

- Overview

- Key Features

- Block Diagram

- Main Components

Initial Delivery State

- Control Signals

- Signals, Interfaces, and Pins

CompactPCI Serial Backplane Connectors

- USB-C Connector Micro-USB2 Connector

- SD

- ° RJ45 Ethernet

- DDR4 SODIMM Socket

- Circular Push Pull Connector

- 26-Pin IDC Header

- 10-Pin Header

- 3-Pin PicoBlade Header

- Battery Holder

- 4-Wire PWM FAN Connectors

- Onboard Peripherals

- Zynq UltraScale XCZU15EG MPSoC

- MAX10 System Controller FPGA

- Programmable Clock Generator

- Oscillators

- FTDIs

- Quad-SPI Flash Memory

- EEPROMs

- USB2 PHY

- ° Gigabit Ethernet PHY

- 8bit DACs

- DIP-Switches

- Buttons

- LEDs

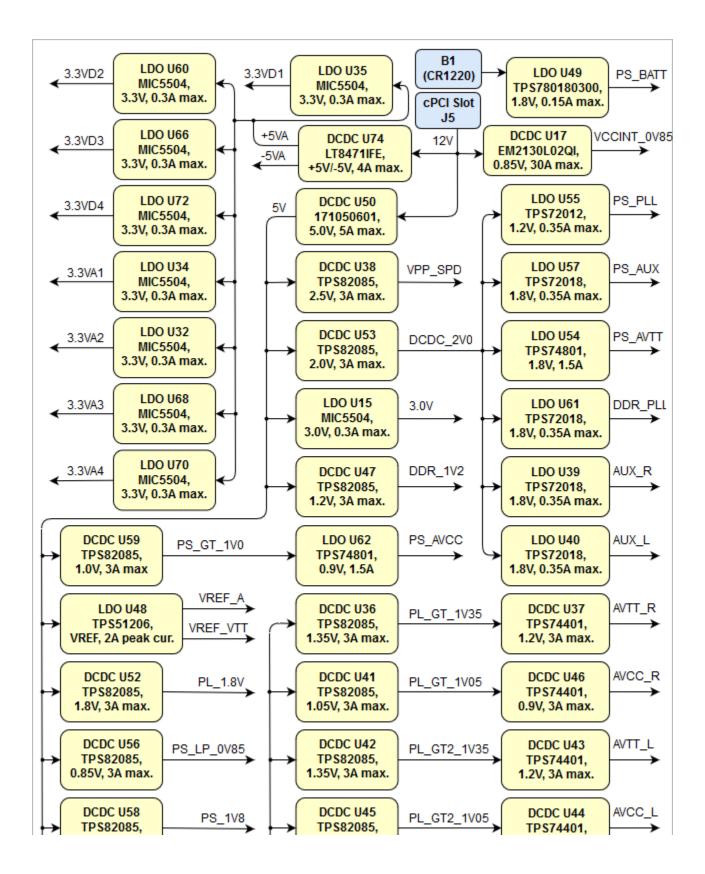

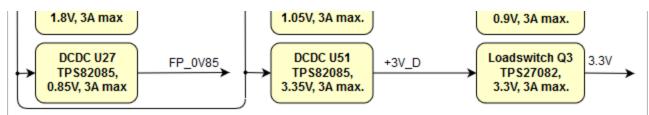

- Power and Power-On Sequence

Over Consumption

- Power Distribution Dependencies

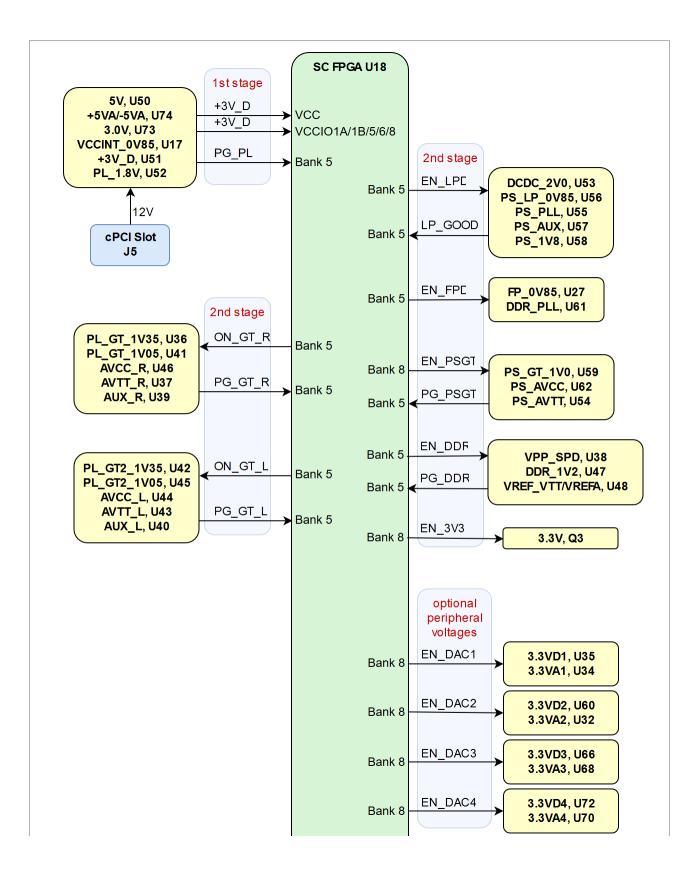

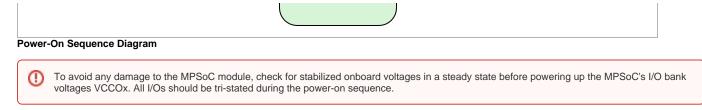

- Power-On Sequence

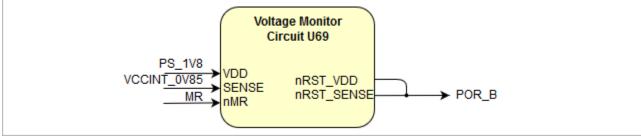

- Voltage Monitor Circuit

- Power Rails

- Bank Voltages

- Technical Specifications

- Absolute Maximum Ratings

- Recommended Operating Conditions

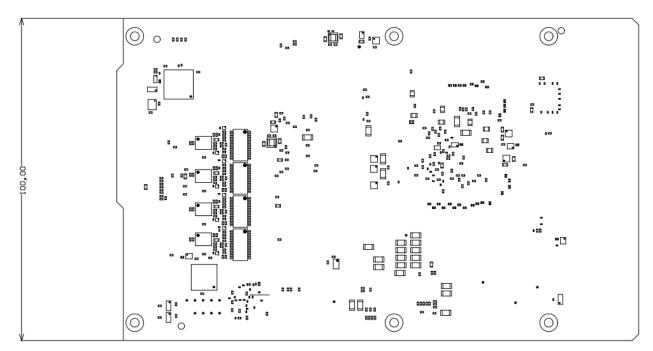

- Physical Dimensions

- Variants Currently In Production

- **Revision History**

- Hardware Revision History

- Document Change History

- Disclaimer

- Data Privacy

- Document Warranty

Limitation of Liability

- Copyright Notice

- Technology Licenses

- Environmental Protection

- REACH, RoHS and WEEE

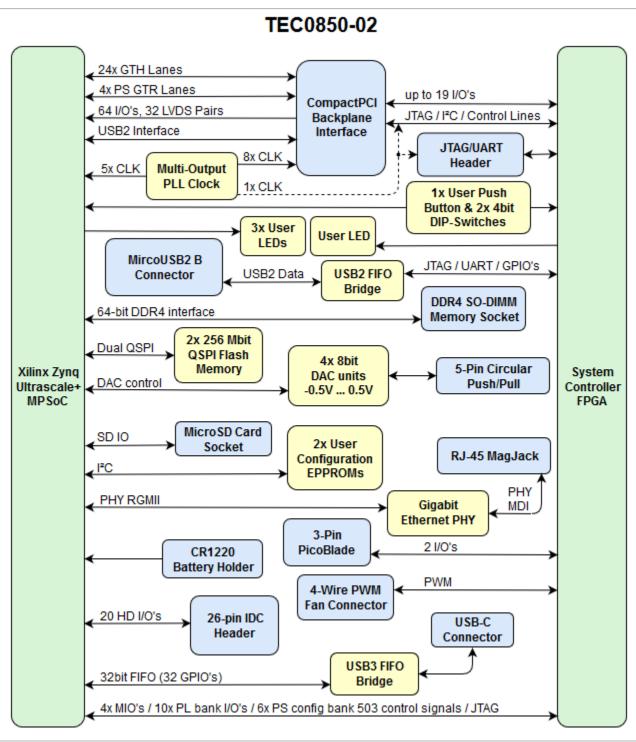

### Overview

The Trenz Electronic TEC0850 board is a CompactPCI Serial card (3U form factor) integrating a Xilinx Zynq UltraScale+ MPSoC, one DDR4 SDRAM SODIMM socket with 64bit wide data bus, max. dual 512 MByte Flash memory for configuration and operation, 24 Gigabit transceivers on PL side and 4 on PS side, powerful switch-mode power supplies for all onboard voltages, USB2 and USB3 FIFO bridges and a large number of configurable I/Os available on the CompactPCI Serial backplane connectors.

Refer to http://trenz.org/tec0850-info for the current online version of this manual and other available documentation.

## **Key Features**

٠

- Zyng UltraScale+ MPSoC ZU15

- Front side interface connectors

- RJ-45 GbE Ethernet interface

- ° Circular push/pull connector with 4x on-board 8bit DAC output

- MicroSD Card connector

- USB 2.0 and USB 3.0 to FIFO bridge connector

- 4x status LEDs

- 4 CompactPCI Serial connectors for backplane connection (3U form factor)

- ° 24 GTH lanes

- · 4 PS GTR lanes

- USB 2.0 interface

- ° 64 Zynq PL HP I/O's

- 8x PLL clock input

- JTAG, I<sup>2</sup>C and 7 user I/O's to MAX10 FPGA

- 64bit DDR4 SODIMM (PS connected), 8 GByte maximum

- Dual parallel QSPI Flash (bootable), 512 MByte maximum

- 26-pin header with 20 Zynq PL HD I/O's

- 3-pin header with 2 MAX10 FPGA I/O's

- System Controller (Altera MAX10 FPGA SoC)

- Power Sequencing

- ° System management and control for MPSoC and onboard peripherals

- Si5345 programmable 10 output PLL clock generator

- Si53340 Quad clock buffer

- 2x 4bit DIP switches

- 1x user push button

- Zynq MPSoC cooling FAN connector

- On-board high-efficiency DC-DC converters

### **Block Diagram**

TEC0850-02 block diagram

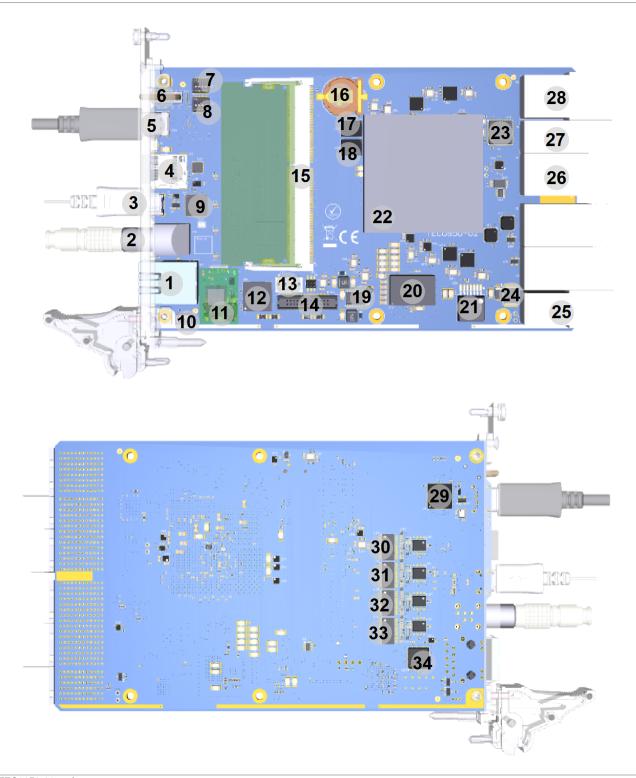

### **Main Components**

TEC0850-02 main components

- 1. GbE RJ-45 MagJack, J7

- 2. 5-pin circular push/pull receptacle connector for DAC output, J15

- 3. Micro USB 2.0 B receptacle connector, J9

- 4. MicroSD Card socket, J11

- 5. USB 3.0 Type C connector, J10

- 6. LED light pipes J14 integrating LEDs D1 ... D4

- 7. 4bit DIP-switch, S2

- 8. 4bit DIP-switch, S1

- 9. FTDI FT2232 USB 2.0 to UART/JTAG bridge, U4

- 10. 3-pin PicoBlade header, J8

- 11. MAX10 FPGA JTAG/UART 10-pin header, J13

- 12. Altera MAX10 System Controller FPGA, U18

- 13. 4-Wire PWM fan connector, J17

- 14. 26-pin IDC header for FPGA PL I/O's, J16

- 15. DDR4 SO-DIMM 260-pin socket, U3

- 16. Battery Holder CR1220, B1

- 17. 256 Mbit (32 MByte) Micron Serial NOR Flash Memory N25Q256A, U24

- 18. 256 Mbit (32 MByte) Micron Serial NOR Flash Memory N25Q256A, U25

- 19. DC-DC Converter LT8471IFE @+5VA/-5VA, U74

- 20. DC-DC Converter EM2130L02QI @VCCINT\_0V85, U17

- 21. DC-DC Converter 171050601 @5V, U50

- 22. Xilinx Zynq Ultrascale+ MPSoC, U1

- 23. Si5345A 10-output I<sup>2</sup>C programmable PLL clock, U14

- 24. Main power fuse @2.5A/16V, F1

- 25. cPCI connector, J1

- 26. cPCI connector, J4

- 27. cPCI connector, J5

- 28. cPCI connector, J6

- 29. FTDI FT601Q USB 3.0 to FIFO bridge, U9

- 30. TI THS5641 8bit DAC ,U28

- **31.** TI THS5641 8bit DAC ,U31 **32.** TI THS5641 8bit DAC ,U29

- 33. TI THS5641 8bit DAC ,U33

- 34. Marvell Alaska 88E1512 GbE PHY ,U20

### **Initial Delivery State**

| Storage device name                                                                    | Content | Notes          |

|----------------------------------------------------------------------------------------|---------|----------------|

| User configuration EEPROMs (1x Microchip 24AA128T-I/ST, 1x Microchip 24AA025E48T-I/OT) | Empty   | Not programmed |

| USB 2.0 to UART/JTAG bridge configuration EEPROM (ST M93C66)                           | Empty   | Not programmed |

| Si5345A programmable PLL NVM OTP                                                       | Empty   | Not programmed |

| 2x QSPI Flash memory                                                                   | Empty   | Not programmed |

Initial delivery state of programmable devices on the module

### **Control Signals**

To get started with TEC0850 board, some initial signals should be set described in the following table:

| Control signal | Switch /<br>Button | Signal<br>Schematic<br>Names | Connected to                    | Functionality                                            | Notes |

|----------------|--------------------|------------------------------|---------------------------------|----------------------------------------------------------|-------|

| SC JTAGEN      | S1-1               | JTAGEN                       | SC FPGA U18, bank 1B, pin<br>E5 | OFF: MAX 10 JTAG enabled,<br>ON: Zynq MPSoC JTAG enabled | -     |

| EEPROM WP                   | S1-2                 | WP      | EEPROM U63, pin 7                          | Write protect, active on OFF position                                                           | -                                                                                                                     |

|-----------------------------|----------------------|---------|--------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| FPGA PUDC                   | S1-3                 | PUDC_B  | Zynq MPSOC PS Config<br>Bank 503, pin AD15 |                                                                                                 |                                                                                                                       |

| SC Switch                   | S1-4                 | SW4     | SC FPGA U18, bank 8, pin A5                | low active logic                                                                                | Reserved for future use                                                                                               |

| 4bit boot mode setting code | S2-1                 | MODE3   | Zynq MPSOC PS Config<br>Bank 503, pin R23  | Set 4-bit code for boot mode selection,                                                         | See Zynq UltraScale+ Device Technical<br>Reference Manual                                                             |

|                             | S2-2                 | MODE2   | Zynq MPSOC PS Config<br>Bank 503, pin T23  | most common modes are as follows:                                                               | page 236 for full boot modes descript                                                                                 |

|                             | S2-3                 | MODE1   | Zynq MPSOC PS Config<br>Bank 503, pin R22  | Set DIP-switches as bit pattern<br>"S1-4   S1-3   S1-2   S1-<br>1 : Mode":                      |                                                                                                                       |

|                             | S2-4                 | MODE0   | Zynq MPSOC PS Config<br>Bank 503, pin T22  | ON   ON   ON   ON : JTAG Boot<br>ON   ON   ON   OFF : Quad-SPI<br>ON   ON   OFF   OFF : SD Card |                                                                                                                       |

| Push button                 | S3                   | USR_BTN | SC FPGA U18, bank 5, pin<br>J10            | low active logic                                                                                | See the documentation of the firmware<br>of SC FPGA<br>U18 for current functionality of the<br>onboard Push Button S3 |

| SC FPGA U18<br>Reset        | header J13,<br>pin 6 | M10_RST | SC FPGA U18, bank 8, pin A7                | low active reset line                                                                           | -                                                                                                                     |

**TEC0850 Control Signals**

# Signals, Interfaces, and Pins

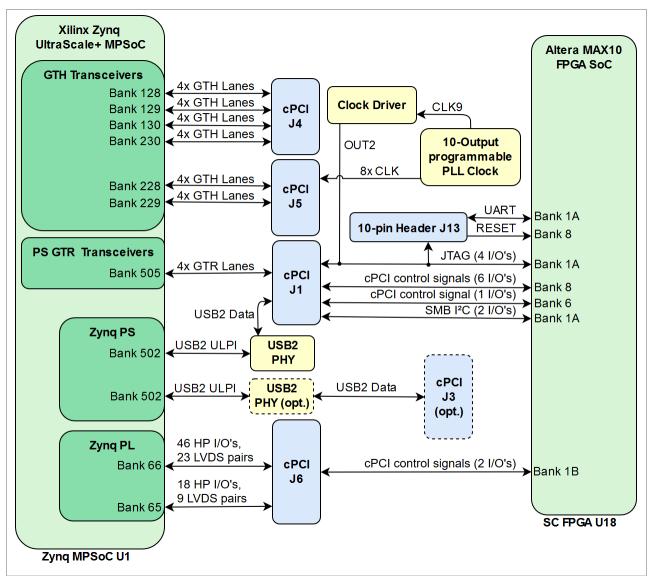

### **CompactPCI Serial Backplane Connectors**

The TEC0850 board is equipped with 3 CompactPCI Serial high-speed backplane connectors which provide serial high-speed interconnects with transmission rates up to 12 Gb/s to the Zynq MPSoCs MGT lanes. On the cPCI connectors are also available single-ended Zynq MPSoC PL HP I/O's, high-speed USB 2.0 interface and single-ended I/O's of the System Controller FPGA.

The connectors support single-ended and differential signaling to the Zynq MPSoC PL HP banks 65 and 66 as those FPGA I/O's are routed as LVDS-pairs to the backplane connector.

The TEC0850 board is designed to be connected to the System Slot of the backplane, whereby 4 of the 6 connectors of the System Slot configuration are fitted to the TEC0850 board.

Following diagram gives an overview of the CompactPCI Serial backplane connectors and their connections to the Zynq Ultrascale+ MPSoC and the System Controller FPGA U18:

TEC0850-02 CompactPCI I/O and high-speed interfaces

Following tables contains information about the interfaces, I/O's, clock and VCCIO sources available on the cPCI connectors:

- CompactPCI Serial Connector J1

CompactPCI Serial Connector J3

- 3. CompactPCI Serial Connector J4

- 4. CompactPCI Serial Connector J5

- 5. CompactPCI Serial Connector J6

**CompactPCI Serial Connector J1**

| Interfaces       | I/O Signal Count | LVDS-pairs count | Connected to        | VCCO bank Voltage | Notes                                       |

|------------------|------------------|------------------|---------------------|-------------------|---------------------------------------------|

| I/O              | 1                | -                | SC FPGA U18 Bank 6  | +3V_D             | control signals in cPCI pin assignment      |

|                  | 6                | -                | SC FPGA U18 Bank 8  | +3V_D             | control signals in cPCI pin assignment      |

| I <sup>2</sup> C | 2                | -                | SC FPGA U18 Bank 1A | +3V_D             | SC FPGA U18 I <sup>2</sup> C interface      |

| JTAG             | 4                | -                | SC FPGA U18 Bank 1A | +3V_D             | SC FPGA U18 JTAG interface                  |

| MGT              | -                | 8 (4 x RX/TX)    | Bank 502 PS GTR     | -                 | 4x PS GTR lanes                             |

| USB2             | -                | 1 (RX/TX)        | USB2 PHY U11        | -                 | USB2 OTG A-Device (host)                    |

| Clock Input      | -                | 1                | Clock Driver U73    | -                 | 1x Reference clock input from PLL clock U14 |

cPCI J1 interfaces

| MGT Lane | Bank | Туре | Signal Schematic Name                                                                  | cPCI Connector Pin               | FPGA Pin                                                                                         |

|----------|------|------|----------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------|

| 0        | 505  | GTR  | <ul> <li>PE1_RX0_P</li> <li>PE1_RX0_N</li> <li>PE1_TX0_P</li> <li>PE1_TX0_N</li> </ul> | J1-D5<br>J1-E5<br>J1-A5<br>J1-B5 | PS_MGTRRXP0_505, AB29<br>PS_MGTRRXN0_505, AB30<br>PS_MGTRTXP0_505, AB33<br>PS_MGTRTXN0_505, AB34 |

| 1        | 505  | GTR  | <ul> <li>PE1_RX1_P</li> <li>PE1_RX1_N</li> <li>PE1_TX1_P</li> <li>PE1_TX1_N</li> </ul> | J1-J5<br>J1-K5<br>J1-G5<br>J1-H5 | PS_MGTRRXP1_505, Y29<br>PS_MGTRRXN1_505, Y30<br>PS_MGTRTXP1_505, AA31<br>PS_MGTRTXN1_505, AA32   |

| 2        | 505  | GTR  | <ul> <li>PE1_RX2_P</li> <li>PE1_RX2_N</li> <li>PE1_TX2_P</li> <li>PE1_TX2_N</li> </ul> | J1-E6<br>J1-F6<br>J1-B6<br>J1-C6 | PS_MGTRRXP2_505, W31<br>PS_MGTRRXN2_505, W32<br>PS_MGTRTXP2_505, Y33<br>PS_MGTRTXN2_505, Y34     |

| 3        | 505  | GTR  | <ul> <li>PE1_RX3_P</li> <li>PE1_RX3_N</li> <li>PE1_TX3_P</li> <li>PE1_TX3_N</li> </ul> | J1-K6<br>J1-L6<br>J1-H6<br>J1-I6 | PS_MGTRRXP3_505, V29<br>PS_MGTRRXN3_505, V30<br>PS_MGTRTXP3_505, V33<br>PS_MGTRTXN3_505, V34     |

cPCI J1 MGT lanes

| Clock Signal Schematic Name | cPCI Connector Pin | Header J13 Pin | SC FPGA U18 Pin                    | Notes                                                                                                                                                              |

|-----------------------------|--------------------|----------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • SATA_SL<br>• SATA_SCL     | J1-K3<br>J1-J3     | J13-5<br>J13-1 | Bank 1B, Pin G1<br>Bank 1B, Pin G2 | Supplied by 10-output PLL clock U14,<br>optional if decoupling capacitors and resistors<br>are fitted (see schematic),<br>also shared with SC FPGA and header J13. |

cPCI J1 clock signals

### CompactPCI Serial Connector J3

CompactPCI Serial connector J3 is **not fitted** on the TEC0850 board by default, but is necessary if the second optional USB2 PHY U13 if fitted and its USB2 differential serial data interface is connected to the cPCI connector J2.

| Interfaces        | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes                    |

|-------------------|------------------|------------------|--------------|-------------------|--------------------------|

| USB2              | -                | 1 (RX/TX)        | USB2 PHY U13 | -                 | USB2 OTG A-Device (host) |

| cPCI J3 interface | )S               |                  |              |                   |                          |

### **CompactPCI Serial Connector J4**

| MGT Lane | Bank | Туре | Signal Schematic Name                                                                  | cPCI Connector Pin               | FPGA Pin                                                                         |

|----------|------|------|----------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------|

| 0        | 128  | GTH  | <ul> <li>PE3_RX0_P</li> <li>PE3_RX0_N</li> <li>PE3_TX0_P</li> <li>PE3_TX0_N</li> </ul> | J4-D1<br>J4-E1<br>J4-A1<br>J4-B1 | MGTHRXP0_128, T33<br>MGTHRXN0_128, T34<br>MGTHTXP0_128, T29<br>MGTHTXN0_128, T30 |

| 1        | 128  | GTH  | <ul> <li>PE3_RX1_P</li> <li>PE3_RX1_N</li> <li>PE3_TX1_P</li> <li>PE3_TX1_N</li> </ul> | J4-J1<br>J4-K1<br>J4-G1<br>J4-H1 | MGTHRXP1_128, P33<br>MGTHRXN1_128, P34<br>MGTHTXP1_128, R31<br>MGTHTXN1_128, R32 |

| 2        | 128  | GTH  | <ul> <li>PE3_RX2_P</li> <li>PE3_RX2_N</li> <li>PE3_TX2_P</li> <li>PE3_TX2_N</li> </ul> | J4-E2<br>J4-F2<br>J4-B2<br>J4-C2 | MGTHRXP2_128, N31<br>MGTHRXN2_128, N32<br>MGTHTXP2_128, P29<br>MGTHTXN2_128, P30 |

| 3        | 128  | GTH  | <ul> <li>PE3_RX3_P</li> <li>PE3_RX3_N</li> <li>PE3_TX3_P</li> <li>PE3_TX3_N</li> </ul> | J4-K2<br>J4-L2<br>J4-H2<br>J4-I2 | MGTHRXP3_128, M33<br>MGTHRXN3_128, M34<br>MGTHTXP3_128, M29<br>MGTHTXN3_128, M30 |

| 0        | 129  | GTH  | <ul> <li>PE4_RX0_P</li> <li>PE4_RX0_N</li> <li>PE4_TX0_P</li> <li>PE4_TX0_N</li> </ul> | J4-D3<br>J4-E3<br>J4-A3<br>J4-B3 | MGTHRXP0_129, L31<br>MGTHRXN0_129, L32<br>MGTHTXP0_129, K29<br>MGTHTXN0_129, K30 |

| 1        | 129  | GTH  | <ul> <li>PE4_RX1_P</li> <li>PE4_RX1_N</li> <li>PE4_TX1_P</li> <li>PE4_TX1_N</li> </ul> | J4-J3<br>J4-K3<br>J4-G3<br>J4-H3 | MGTHRXP1_129, K33<br>MGTHRXN1_129, K34<br>MGTHTXP1_129, J31<br>MGTHTXN1_129, J32 |

| 2                 | 129 | GTH | <ul> <li>PE4_RX2_P</li> <li>PE4_RX2_N</li> <li>PE4_TX2_P</li> <li>PE4_TX2_N</li> </ul> | J4-E4<br>J4-F4<br>J4-B4<br>J4-C4 | MGTHRXP2_129, H33<br>MGTHRXN2_129, H34<br>MGTHTXP2_129, H29<br>MGTHTXN2_129, H30 |

|-------------------|-----|-----|----------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------|

| 3                 | 129 | GTH | <ul> <li>PE4_RX3_P</li> <li>PE4_RX3_N</li> <li>PE4_TX3_P</li> <li>PE4_TX3_N</li> </ul> | J4-K4<br>J4-L4<br>J4-H4<br>J4-I4 | MGTHRXP3_129, F33<br>MGTHRXN3_129, F34<br>MGTHTXP3_129, G31<br>MGTHTXN3_129, G32 |

| 0                 | 130 | GTH | <ul> <li>PE5_RX0_P</li> <li>PE5_RX0_N</li> <li>PE5_TX0_P</li> <li>PE5_TX0_N</li> </ul> | J4-D5<br>J4-E5<br>J4-A5<br>J4-B5 | MGTHRXP3_130, B33<br>MGTHRXN3_130, B34<br>MGTHTXP3_130, A31<br>MGTHTXN3_130, A32 |

| 1                 | 130 | GTH | <ul> <li>PE5_RX1_P</li> <li>PE5_RX1_N</li> <li>PE5_TX1_P</li> <li>PE5_TX1_N</li> </ul> | J4-J5<br>J4-K5<br>J4-G5<br>J4-H5 | MGTHRXP2_130, C31<br>MGTHRXN2_130, C32<br>MGTHTXP2_130, B29<br>MGTHTXN2_130, B30 |

| 2                 | 130 | GTH | <ul> <li>PE5_RX2_P</li> <li>PE5_RX2_N</li> <li>PE5_TX2_P</li> <li>PE5_TX2_N</li> </ul> | J4-E6<br>J4-F6<br>J4-B6<br>J4-C6 | MGTHRXP1_130, D33<br>MGTHRXN1_130, D34<br>MGTHTXP1_130, D29<br>MGTHTXN1_130, D30 |

| 3                 | 130 | GTH | <ul> <li>PE5_RX3_P</li> <li>PE5_RX3_N</li> <li>PE5_TX3_P</li> <li>PE5_TX3_N</li> </ul> | J4-K6<br>J4-L6<br>J4-H6<br>J4-16 | MGTHRXP0_130, E31<br>MGTHRXN0_130, E32<br>MGTHTXP0_130, F29<br>MGTHTXN0_130, F30 |

| 0                 | 230 | GTH | <ul> <li>PE6_RX0_P</li> <li>PE6_RX0_N</li> <li>PE6_TX0_P</li> <li>PE6_TX0_N</li> </ul> | J4-D7<br>J4-E7<br>J4-A7<br>J4-B7 | MGTHRXP3_230, A4<br>MGTHRXN3_230, A3<br>MGTHTXP3_230, A8<br>MGTHTXN3_230, A7     |

| 1                 | 230 | GTH | <ul> <li>PE6_RX1_P</li> <li>PE6_RX1_N</li> <li>PE6_TX1_P</li> <li>PE6_TX1_N</li> </ul> | J4-J7<br>J4-K7<br>J4-G7<br>J4-H7 | MGTHRXP2_230, B2<br>MGTHRXN2_230, B1<br>MGTHTXP2_230, B6<br>MGTHTXN2_230, B5     |

| 2                 | 230 | GTH | <ul> <li>PE6_RX2_P</li> <li>PE6_RX2_N</li> <li>PE6_TX2_P</li> <li>PE6_TX2_N</li> </ul> | J4-E8<br>J4-F8<br>J4-B8<br>J4-C8 | MGTHRXP1_230, C4<br>MGTHRXN1_230, C3<br>MGTHTXP1_230, D6<br>MGTHTXN1_230, D5     |

| 3                 | 230 | GTH | <ul> <li>PE6_RX3_P</li> <li>PE6_RX3_N</li> <li>PE6_TX3_P</li> <li>PE6_TX3_N</li> </ul> | J4-K8<br>J4-L8<br>J4-H8<br>J4-18 | MGTHRXP0_230, D2<br>MGTHRXN0_230, D1<br>MGTHTXP0_230, E4<br>MGTHTXN0_230, E3     |

| cPCI J4 MGT lanes | 1   |     |                                                                                        | 1                                |                                                                                  |

cPCI J4 MGT lanes

#### **CompactPCI Serial Connector J5**

| MGT Lane | Bank | Туре | Signal Schematic Name                                                                  | cPCI Connector Pin               | FPGA Pin                                                                     |

|----------|------|------|----------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------|

| 0        | 228  | GTH  | <ul> <li>PE8_RX0_P</li> <li>PE8_RX0_N</li> <li>PE8_TX0_P</li> <li>PE8_TX0_N</li> </ul> | J5-D3<br>J5-E3<br>J5-A3<br>J5-B3 | MGTHRXP0_228, T2<br>MGTHRXN0_228, T1<br>MGTHTXP0_228, R4<br>MGTHTXN0_228, R3 |

| 1        | 228  | GTH  | <ul> <li>PE8_RX1_P</li> <li>PE8_RX1_N</li> <li>PE8_TX1_P</li> <li>PE8_TX1_N</li> </ul> | J5-J3<br>J5-K3<br>J5-G3<br>J5-H3 | MGTHRXP1_228, P2<br>MGTHRXN1_228, P1<br>MGTHTXP1_228, P6<br>MGTHTXN1_228, P5 |

| 2        | 228  | GTH  | <ul> <li>PE8_RX2_P</li> <li>PE8_RX2_N</li> <li>PE8_TX2_P</li> <li>PE8_TX2_N</li> </ul> | J5-E4<br>J5-F4<br>J5-B4<br>J5-C4 | MGTHRXP2_228, M2<br>MGTHRXN2_228, M1<br>MGTHTXP2_228, N4<br>MGTHTXN2_228, N3 |

| 3        | 228  | GTH  | <ul> <li>PE8_RX3_P</li> <li>PE8_RX3_N</li> <li>PE8_TX3_P</li> <li>PE8_TX3_N</li> </ul> | J5-K4<br>J5-L4<br>J5-H4<br>J5-I4 | MGTHRXP3_228, L4<br>MGTHRXN3_228, L3<br>MGTHTXP3_228, M6<br>MGTHTXN3_228, M5 |

| 0        | 229  | GTH  | <ul> <li>PE7_RX0_P</li> <li>PE7_RX0_N</li> <li>PE7_TX0_P</li> <li>PE7_TX0_N</li> </ul> | J5-D1<br>J5-E1<br>J5-A1<br>J5-B1 | MGTHRXP0_229, K2<br>MGTHRXN0_229, K1<br>MGTHTXP0_229, K6<br>MGTHTXN0_229, K5 |

| 1        | 229  | GTH  | <ul> <li>PE7_RX1_P</li> <li>PE7_RX1_N</li> <li>PE7_TX1_P</li> <li>PE7_TX1_N</li> </ul> | J5-J1<br>J5-K1<br>J5-G1<br>J5-H1 | MGTHRXP1_229, J4<br>MGTHRXN1_229, J3<br>MGTHTXP1_229, H6<br>MGTHTXN1_229, H5 |

| 2        | 229  | GTH  | <ul> <li>PE7_RX2_P</li> <li>PE7_RX2_N</li> <li>PE7_TX2_P</li> <li>PE7_TX2_N</li> </ul> | J5-E2<br>J5-F2<br>J5-B2<br>J5-C2 | MGTHRXP2_229, H2<br>MGTHRXN2_229, H1<br>MGTHTXP2_229, G4<br>MGTHTXN2_229, G3 |

| 3        | 229  | GTH  | <ul> <li>PE7_RX3_P</li> <li>PE7_RX3_N</li> <li>PE7_TX3_P</li> <li>PE7_TX3_N</li> </ul> | J5-K2<br>J5-L2<br>J5-H2<br>J5-I2 | MGTHRXP3_229, F2<br>MGTHRXN3_229, F1<br>MGTHTXP3_229, F6<br>MGTHTXN3_229, F5 |

cPCI J5 MGT lanes

| PLL Clock U14 Output | Signal Schematic Name | cPCI Connector J5 Pin | Notes |

|----------------------|-----------------------|-----------------------|-------|

|----------------------|-----------------------|-----------------------|-------|

| OUT1 | PE1_CLK_P     PE1_CLK_N | J5-A5<br>J5-B5 | reference clock signals supplied<br>by on-board 10-output<br>PLL clock generator U14 |

|------|-------------------------|----------------|--------------------------------------------------------------------------------------|

| OUT2 | PE2_CLK_P     PE2_CLK_N | J5-D5<br>J5-E5 |                                                                                      |

| OUT3 | PE3_CLK_P     PE3_CLK_N | J5-G5<br>J5-H5 |                                                                                      |

| OUT4 | PE4_CLK_P     PE4_CLK_N | J5-J5<br>J5-K5 |                                                                                      |

| OUT5 | PE5_CLK_P     PE5_CLK_N | J5-B6<br>J5-C6 |                                                                                      |

| OUT6 | PE6_CLK_P     PE6_CLK_N | J5-E6<br>J5-F6 |                                                                                      |

| OUT7 | PE7_CLK_P     PE7_CLK_N | J5-H6<br>J5-I6 |                                                                                      |

| OUT8 | PE8_CLK_P     PE8_CLK_N | J5-K6<br>J5-L6 |                                                                                      |

cPCI J5 clock signals

**CompactPCI Serial Connector J6**

| Interfaces | I/O Signal Count | LVDS-pairs count | Connected to        | VCCO bank Voltage | Notes                            |

|------------|------------------|------------------|---------------------|-------------------|----------------------------------|

| I/O        | 46               | 23               | PL bank 66          | PL_1.8V           | -                                |

|            | 18               | 9                | PL bank 65          | PL_1.8V           | -                                |

|            | 2                | -                | SC FPGA U18 Bank 1B | +3V_D             | Signalname: 'DET_RIO', 'DET_BPR' |

cPCI J6 Interfaces

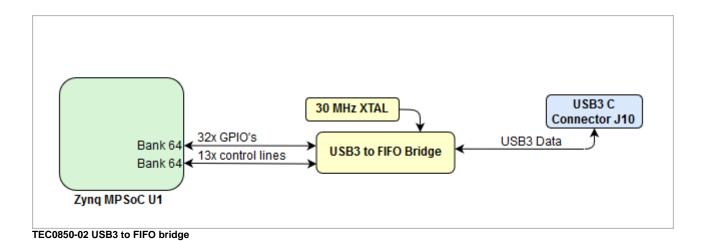

### **USB-C** Connector

Front panel USB-C Interface is connected to USB FIFO bridge chip FT601Q. 32-bit FIFO bridge provides a simple high-speed interface to Zynq UltraScale+ PL.

The USB 3.0 to FIFO bridge FTDI FT601Q U9 is connected to the Zynq MPSoC's PL bank 64 and is accessible through USB-C connector J10:

| Interface       | Signal Schematic Names                                                                                                                                                                                               | Connected to        | Notes               |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|

| USB3 data lane  | <ul> <li>SSRX_P</li> <li>SSRX_N</li> <li>SSTXX_P</li> <li>SSTXX_N</li> </ul>                                                                                                                                         | USB C Connector J10 | -                   |

| USB2 data lane  | • SS_D_P<br>• SS_D_N                                                                                                                                                                                                 | USB C Connector J10 | -                   |

| Control Lines   | <ul> <li>FTDI_RESET_N</li> <li>WAKEUP_N</li> <li>SIWU_N</li> <li>TXE_N</li> <li>RXF_N</li> <li>WR_N</li> <li>RD_N</li> <li>OE_N</li> <li>BE_0</li> <li>BE_1</li> <li>BE_2</li> <li>BE_3</li> <li>FIFO_CLK</li> </ul> | PL bank 64          | -                   |

| Parallel GPIO's | <ul> <li>DATA0</li> <li>.</li> <li>.</li> <li>DATA31</li> </ul>                                                                                                                                                      | PL bank 64          | 32bit FIFO register |

#### USB-C connector J10

See FT600Q-FT601Q IC Datasheet for interface details.

### **Micro-USB2 Connector**

Front panel Micro-USB2 Interface provides access to UART and JTAG functions via FTDI FT2232 chip. Use of this feature requires that USB driver is installed on your host PC. UART0 with MIO 22 .. 23 should be selected in "Zynq UltraScale+ MPSoC" configuration.

The Digilent plug-in software and cable drivers must be installed on your machine for you to be able to use JTAG interface.

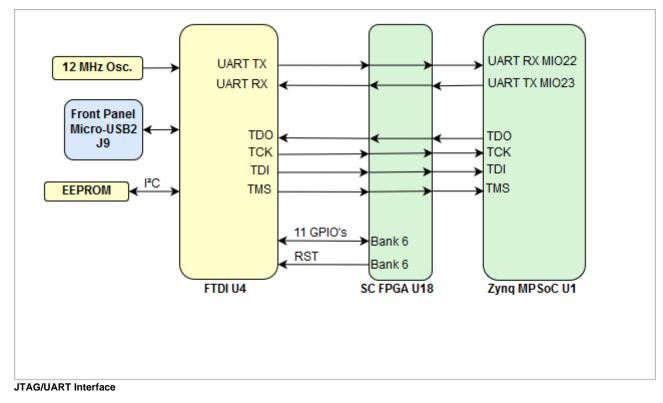

### The USB2 to FIFO bridge FTDI FT2232H U4 is connected to the SC FPGA U18 and is accessible through Micro-USB2 connector J9:

| Interface       | Signal Schematic Names                                                                                                                                                                                                                                                                                                     | Connected to            | Notes |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------|

| USB2 data lane  | • USB_P<br>• USB_N                                                                                                                                                                                                                                                                                                         | Micro-USB2 connector J9 | -     |

| Control Lines   | • FTDI_RST                                                                                                                                                                                                                                                                                                                 | SC FPGA U18, bank 6     | -     |

| Parallel GPIO's | <ul> <li>ADBUS0</li> <li>ADBUS1</li> <li>ADBUS2</li> <li>ADBUS3</li> <li>BDBUS0</li> <li>BDBUS1</li> <li>BDBUS2</li> <li>BDBUS3</li> <li>BDBUS4</li> <li>BDBUS5</li> <li>BDBUS6</li> <li>BDBUS7</li> <li>BCBUS0</li> <li>BCBUS1</li> <li>BCBUS2</li> <li>BCBUS3</li> <li>BCBUS3</li> <li>BCBUS3</li> <li>BCBUS4</li> </ul> | SC FPGA U18, bank 6     | -     |

#### Micro-USB2 connector J9

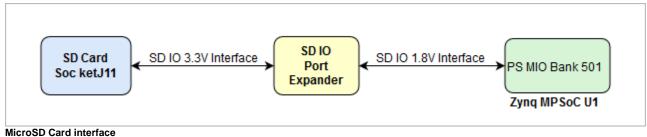

### SD

The SD Card interface of the TEC0850 board is not directly wired to the connector J11 pins but through a Texas Instruments TXS02612 SD IO Port Expander, which is needed for voltage translation due to different voltage levels of the Micro SD Card and MIO-bank of the Xilinx Zynq MPSoC. The Micro SD Card has 3.3V signal voltage level, but the PS MIO-bank on the Xilinx Zyng MPSoC has VCCIO of 1.8V.

There are some limitations to use SD card Interface in Linux.

- Zyng UltraScale+ SD controller is working only in the 3.3V mode as it connected to SD card socket using SD IO port expander U10 as 1.8V to 3.3 V level shifter.

- · Micro SD card socket has no "Write Protect" switch.

| 0 | To force Linux driver not to use these features to add following instructions to device tree file.<br>&sdhci1 { |

|---|-----------------------------------------------------------------------------------------------------------------|

|   | no-1-8-v;<br>disable-wp;<br>};                                                                                  |

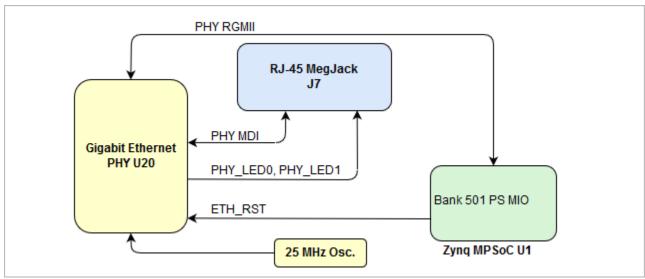

### **RJ45 - Ethernet**

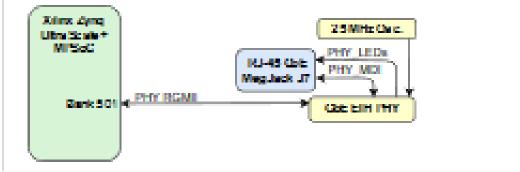

Onboard Gigabit Ethernet PHY is provided with Marvell Alaska 88E1512 IC U20. The Ethernet PHY RGMII interface is connected to the Zyng MPSoC Ethernet interface of the PS MIO bank 501. I/O voltage is fixed at 1.8V for HSTL signaling. The reference clock input of the PHY is supplied from the onboard 25.000000 MHz oscillator U21. The LEDs of the RJ-45 MegJack J13 are connected to the GbE PHY U20 status LED output.

Gigabit Ethernet Interface

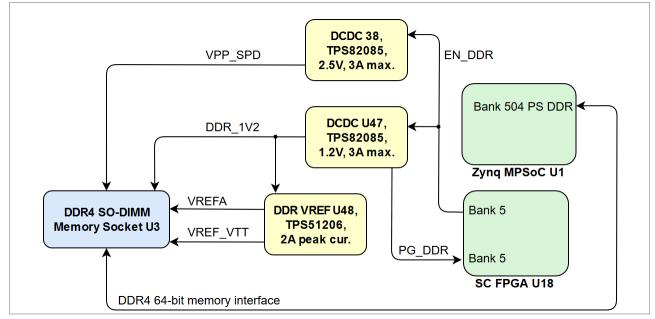

### **DDR4 SODIMM Socket**

On the TEC0850 board, there is a DDR4 memory interface U3 with a 64-bit data bus width available for SO-DIMM modules connected to the Zynq UltraScale+ DDRC hard memory controller.

#### DDR4 SDRAM SODIMM socket

Following table gives an overview of the memory interface I/O signals of the DDR4 SDRAM SO-DIMM Socket U3:

| DDR4 SDRAM I/O Signal | Signal Schematic Name | Connected to | Notes |

|-----------------------|-----------------------|--------------|-------|

|-----------------------|-----------------------|--------------|-------|

| Address inputs                   | • DDR4-A0 DDR4-A16                                                                                       | PS DDR Bank 504 | -                                                   |

|----------------------------------|----------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------|

| Bank address inputs              | • DDR4-BA0 / DDR4-BA1                                                                                    | _               | -                                                   |

| Bank group inputs                | • DDR4-BG0 / DDR4-BG1                                                                                    |                 | -                                                   |

| Differential clocks              | <ul> <li>DDR4-CLK0_P</li> <li>DDR4-CLK0_N</li> <li>DDR4-CLK1_P</li> <li>DDR4-CLK1_N</li> </ul>           |                 | 2 x DDR4 clock                                      |

| Data input/output                | • DQ0 DQ63                                                                                               | _               | -                                                   |

| Check bit input/output           | • CB0 CB7                                                                                                | _               | -                                                   |

| Data strobe (differential)       | <ul> <li>DDR4-DQS0_P</li> <li>DDR4-DQS0_N</li> <li></li> <li>DDR4-DQS8_P</li> <li>DDR4-DQS8_N</li> </ul> |                 | -                                                   |

| Data mask and data bus inversion | • DDR4-DM0 DDR4-DM8                                                                                      |                 | -                                                   |

| Serial address inputs            | • DDR4-SA0 DDR4-SA2                                                                                      |                 | address range configuration on I <sup>2</sup> C bus |

| Control Signals                  | DDR4-CS_N0 / DDR4-CS_N1                                                                                  | _               | chip select signal                                  |

|                                  | DDR4-ODT0 / DDR4-ODT1                                                                                    |                 | On-die termination enable                           |

|                                  | • DDR4-RESET                                                                                             |                 | nRESET                                              |

|                                  | • DDR4-PAR                                                                                               |                 | Command and address parity input                    |

|                                  | DDR4-CKE0 / DDR4-CKE1                                                                                    | _               | Clock Enable                                        |

|                                  | • DDR4-ALERT                                                                                             |                 | CRC error flag                                      |

|                                  | • DDR4-ACT                                                                                               |                 | Activation command input                            |

|                                  | DDR4-EVENT                                                                                               |                 | Temperature event                                   |

| I <sup>2</sup> C |                       | not connected | - |

|------------------|-----------------------|---------------|---|

|                  | DDR4-SCL     DDR4-SDA |               |   |

|                  |                       |               |   |

DDR4 SDRAM SO-DIMM socket U3

### **Circular Push Pull Connector**

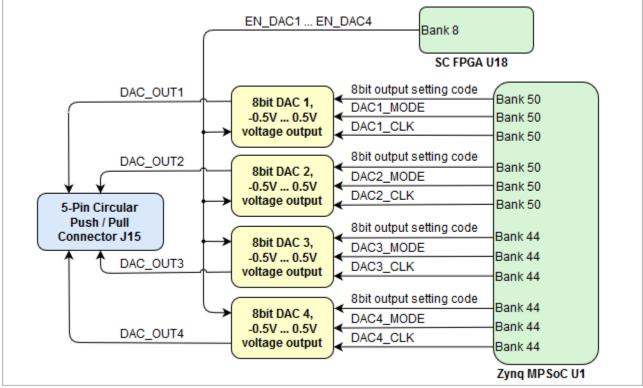

The TEC0850 board provides 4x DAC analog voltage output on the 5-pin circular push/pull connector J15. Each of the DAC units consists of one Texas Instruments THS5641AIPW digital to analog converter, TI THS4631D operational amplifier and two LDOs, by which the DAC unit can be switched on and off.

The TI THS4631D digital to analog converter wired to the operational amplifier circuitry creating the DAC unit with a voltage output range from -0.5V ... 0.5 V. See TI THS5641 datasheet and schematic how to control the DAC unit and to set the analog output voltages on connector J15.

4x 8bit DAC units

### **26-Pin IDC Header**

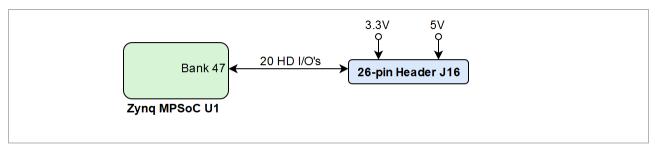

There is a 26-pin IDC header (2x13, 1.27mm grid size) J16 available on the TEC0850 board which exposes the 20 FPGA HD I/O's of PL bank 47 to the user. The PL bank 47 has 3.3V VCCO bank voltage, on the header J16 there also the voltage levels 3.3V and 5V available. The I/O's can be accessed with a corresponding IDC connector.

Zynq MPSoC PL I/O's IDC pin-header

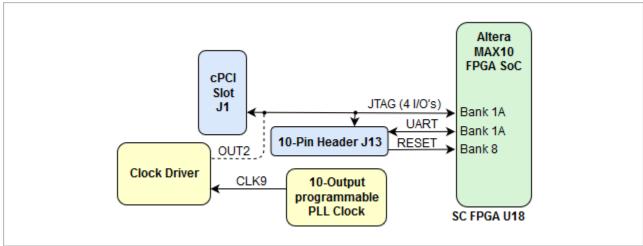

### **10-Pin Header**

On the TEC0850 there is a 10-pin SMT header (2x5, 2.54mm grid size) J13 present which provides access to the JTAG and UART interface of Altera MAX10 System Controller FPGA. The header J13 has a compatible pin assignment to the TEI0004 JTAG programmer for Altera FPGAs, the voltage levels 3.3V is on the header available as a reference I/O-voltage for JTAG and UART.

The 4 JTAG pins of the header J13 are also connected to the cPCI connector J1 and can be used as user GPIO's of the SC FPGA U18 with other functionalities then JTAG.

On the header J13, there is also a optional reference clock signal from PLL clock U14 available, if the necessary resistors and capacitors are fitted on board. The clock can also be used for the SC FPGA U18 and on the cPCI connector J1.

10-pin JTAG/UART header

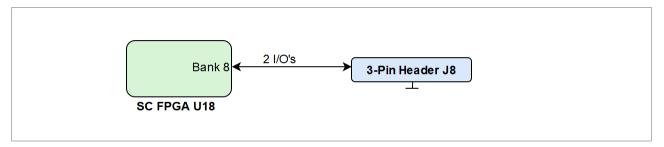

### **3-Pin PicoBlade Header**

2 I/O's of the SC FPGA U18 are exposed to the on-board 3-Pin PicoBlade header J8 available to the user or for future use of upcoming versions of SC FPGA firmware.

3-pin PicoBlade header

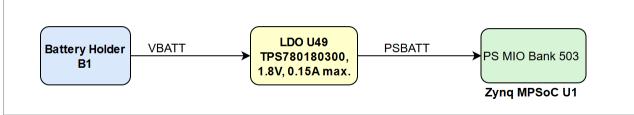

## **Battery Holder**

There is a CR1220 battery holder available to the supply the voltage for the Zynq MPSoC's Battery Power Domain (BBRAM and RTC). The battery voltage VBATT should be in the range of 2.2V to 5.5V, use the 3.0V CR1220 battery.

Backup-Battery Holder

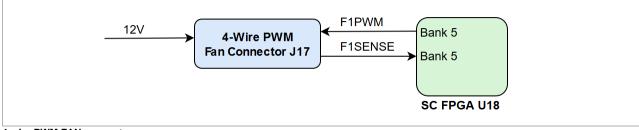

## **4-Wire PWM FAN Connectors**

The TEC0850 offers one 4-wire PWM FAN connector FPGA cooling fan controlled by SC FPGA U18:

4-wire PWM FAN connector

# **Onboard Peripherals**

## Zynq UltraScale XCZU15EG MPSoC

The TEC0850 board is populated with the Zynq UltraScale+ XCZU15EG-1FFVB1156E MPSoC.

The PS MIO pins are routed to the onboard peripherals as follows:

| PS MIO | Function | Connected to     |

|--------|----------|------------------|

| 0      | QSPI*    | U24-B2, CLK      |

| 1      | QSPI*    | U24-D2, DO/IO1   |

| 2      | QSPI*    | U24-C4, WP/IO2   |

| 3      | QSPI*    | U24-D4, HOLD/IO3 |

| 4      | QSPI*    | U24-D3, DI/IO0   |

| 5     | QSPI*                   | U24-C2, CS                                                |

|-------|-------------------------|-----------------------------------------------------------|

| 6     | -                       | not connected                                             |

| 7     | QSPI*                   | U25-C2, CS                                                |

| 8     | QSPI*                   | U25-D3, DI/IO0                                            |

| 9     | QSPI*                   | U25-D2, DO/IO1                                            |

| 10    | QSPI*                   | U17-C4, WP/IO2                                            |

| 11    | QSPI*                   | U25-D4, HOLD/IO3                                          |

| 12    | QSPI*                   | U25-B2, CLK                                               |

| 13 15 | -                       | not connected                                             |

| 16    | USB2 PHY Reset          | USB2 PHY U11, pin27                                       |

| 17    | USB2 PHY Reset          | USB2 PHY U13, pin27 (optional, PHY not fitted by default) |

| 18 19 | -                       | not connected                                             |

| 2021  | PS MIO I <sup>2</sup> C | I <sup>2</sup> C peripherals                              |

| 22 25 | user MIO                | SC FPGA U18, bank 2                                       |

| 26 38 | RGMII                   | GbE PHY U20                                               |

| 39 44 | -                       | not connected                                             |

| 45 51 | SD IO                   | MicroSD Card socket J11                                   |

| 52 63 | USB2 ULPI               | USB2 PHY U11                                              |

| 64 75 | USB2 ULPI               | USB2 PHY U13 (optional, PHY not fitted by default)        |

| 76 77 | ETH MDC / MDIO          | GbE PHY U20                                               |

|       |                         |                                                           |

\* Flash is used as QSPI dual parallel **Default MIO Configuration**

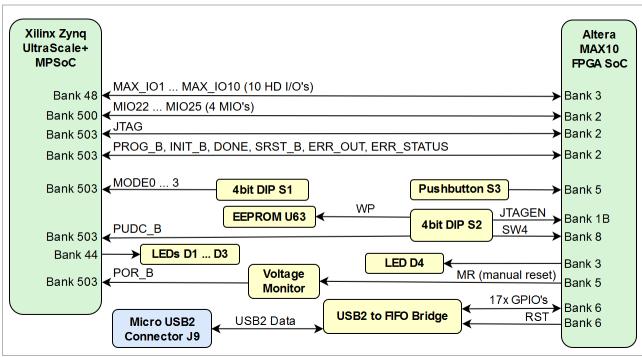

### **MAX10 System Controller FPGA**

The TEC0850 board is equipped with one System Controller FPGA (Intel MAX10 10M08SAU169C8G) with the schematic designators U18. The SC FPGA is the central system management unit where essential control signals are logically linked by the implemented logic in FPGA firmware, which generates output signals to control the system, the onboard peripherals, and the interfaces. Interfaces like JTAG and UART between the FTDI FT2232H chip and to the Zynq MPSoC are by-passed, forwarded and controlled by the System Controller FPGA.

Other tasks of the System Controller FPGA are the monitoring of the power-on sequence and to display the programming state of the FPGA module. The functionalities and configuration of the pins depending on the SC FPGA's firmware. The documentation of the firmware of SC FPGA U18 contains detailed information on this matter.

The System Controller FPGA is connected to the Zynq Ultrascale+ MPSoC through MIO and PL pins. The signals of these pins are forwarded by the SC FPGA to control some of the onboard peripherals.

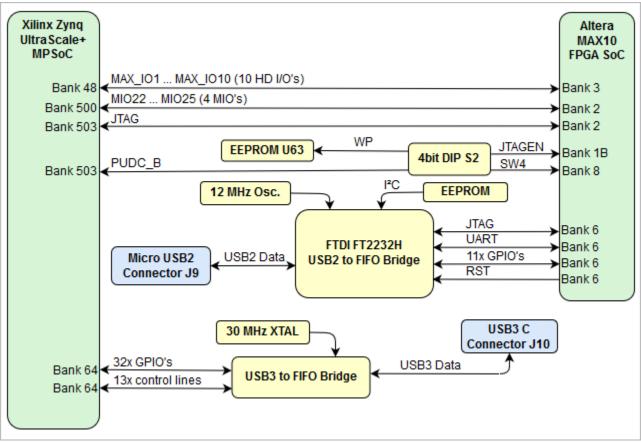

Following block diagram visualizes the connection of the SC FPGA with the Zynq Ultrascale+ MPSoC via 4 PS MIO pins (MIO22 ... 25), PS Config control signals and 10 singled ended PL HD bank 48 I/O pins (MAX\_IO1 ... MAX\_IO10):

TEC0850 MAX10 System Controller FPGA

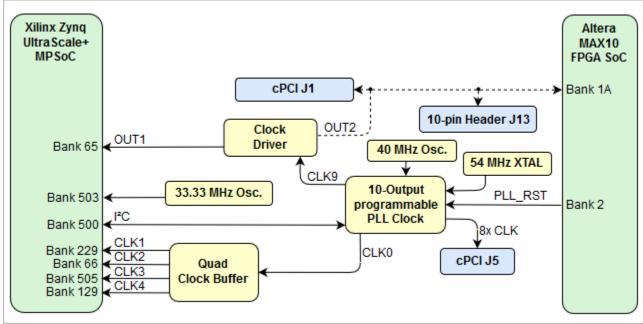

### **Programmable Clock Generator**

There is a Si5345A U14, Silicon Labs I<sup>2</sup>C programmable 10-output PLL clock generator on-board to generate various reference clocks for the Zynq MPSoC MGT banks and onboard peripherals.

10-output I<sup>2</sup>C programmable clock generator

| Si5345A U14 Pin | Signal Schematic Name | Connected to                     | Signal Direction | Note                                           |

|-----------------|-----------------------|----------------------------------|------------------|------------------------------------------------|

| INO             | • IN0_P               | 40.000 MHz Oscillator U75        | Input            | external reference<br>clock input              |

|                 | • IN0_N               | GND                              |                  |                                                |

| IN1             | -                     | not connected                    | Input            | not used                                       |

|                 | -                     | not connected                    |                  |                                                |

| N2              | -                     | not connected                    | Input            | not used                                       |

|                 | -                     | not connected                    |                  |                                                |

| IN3             | -                     | not connected                    | Input            | not used                                       |

|                 | -                     | not connected                    |                  |                                                |

| Ουτο            | CLK0_P                | Quad clock buffer<br>Si53340 U16 | Output           | reference clock input to<br>Quad clock buffer  |

|                 | CLK0_N                |                                  |                  |                                                |

| OUT1            | PE1_CLK_N             | cPCI J5, pin B5                  | Output           | reference clock output<br>to cPCI connector J5 |

|                 | PE1_CLK_P             | cPCI J5, pin A5                  |                  |                                                |

| OUT2            | PE5_CLK_N             | cPCI J5, pin C6                  | Output           |                                                |

|                 | PE5_CLK_P             | cPCI J5, pin B6                  |                  |                                                |

| OUT3            | PE2_CLK_N             | cPCI J5, pin E5                  | Output           |                                                |

|                 | PE2_CLK_P             | cPCI J5, pin D5                  |                  |                                                |

| OUT4            | PE3_CLK_N             | cPCI J5, pin H5                  | Output           |                                                |

|                 | PE3_CLK_P             | cPCI J5, pin G5                  |                  |                                                |

| OUT5            | • PE4_CLK_N           | cPCI J5, pin K5                  | Output           |                                                |

|                 | PE4_CLK_P             | cPCI J5, pin J5                  |                  |                                                |

Following table shows onboard Silicon Labs I<sup>2</sup>C programmable Si5345A U17 10-output programmable PLL reference clock generator inputs and outputs:

| OUT6              | • PE6_CLK_N            | cPCI J5, pin F6                       | Output |                                                |  |

|-------------------|------------------------|---------------------------------------|--------|------------------------------------------------|--|

|                   | PE6_CLK_P              | cPCI J5, pin E6                       |        |                                                |  |

| OUT7              | • PE8_CLK_N            | cPCI J5, pin L6                       | Output | -                                              |  |

|                   | PE8_CLK_P              | cPCI J5, pin K6                       |        |                                                |  |

| OUT8              | • PE7_CLK_N            | cPCI J5, pin I6                       | Output | _                                              |  |

|                   | PE7_CLK_P              | cPCI J5, pin H6                       |        |                                                |  |

| OUT9              | • CLK9_P               | Clock Driver LTC6975 U73              | Output | reference clock input to dual clock driver U73 |  |

|                   | CLK9_N                 |                                       |        |                                                |  |

| XA/XB             | • XAXB_P               | 54.000 MHz quartz<br>oscillator Y3    | Input  | Differential quartz oscillator<br>clock input  |  |

|                   | • XAXB_N               |                                       |        |                                                |  |

| SCLK,<br>SDA/SDIO | • I2C_SCL<br>• I2C_SDA | <ul><li>MIO20</li><li>MIO21</li></ul> | BiDir  | I <sup>2</sup> C address 0x69                  |  |

### SI5345 Clock Outputs

The clock outputs OUT1 and OUT9 are distributed via clock buffer U16 and clock driver U14 to several PL and MGT banks:

| Si53340 U16 Pin | Signal Schematic Name | Connected to               | Signal Direction | Note                                  |

|-----------------|-----------------------|----------------------------|------------------|---------------------------------------|

| Q0              | • CLK1_P<br>• CLK1_N  | U1, pin G8<br>U1, pin G7   | Output           | GTH bank 229 reference clock input    |

| Q1              | • CLK2_P<br>• CLK2_N  | U1, pin Y8<br>U1, pin Y7   | Output           | PL HP bank 66 reference clock input   |

| Q2              | • CLK3_P<br>• CLK3_N  | U1, pin U27<br>U1, pin U28 | Output           | PS GTR Bank 505 reference clock input |

| Q3              | • CLK4_P<br>• CLK4_N  | U1, pin L27<br>U1, pin L28 | Output           | GTH bank 129 reference clock input    |

| LTC6957 U73 Pin |                       |                            |                  |                                       |

| OUT1 | • CK_PLL_P<br>• CK_PLL_N | U1, pin AG5<br>U1, pin AG4            | Output | PL HP bank 65 reference clock input                                                                                                                                      |

|------|--------------------------|---------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT2 | • CK_P<br>• CK_N         | Signal 'SATA_SL'<br>Signal 'SATA_SCL' | Output | optional reference clock input to cPCI connector J1,<br>if decoupling capacitors and resistors<br>are fitted (see schematic),<br>also shared with SC FPGA and header J13 |

Clock driver and buffer outputs

The clock generator U14 is programmable via the onboard I<sup>2</sup>C bus connected to MIO 20...21 pins. The I<sup>2</sup>C address is shown in the table below.

| I2C address | Chip       | Description                     |

|-------------|------------|---------------------------------|

| 0x69        | U14 Si5345 | Clock generator and distributor |

SI5345 I2C address

### Oscillators

The TEC0850 board is equipped several onboard oscillators to provide the Zynq Ultrascale+ MPSoC's PS and PL banks and the onboard peripherals with reference clock-signals:

| Clock Source                     | Signal Schematic Name | Frequency     | Clock Input Destination                       |

|----------------------------------|-----------------------|---------------|-----------------------------------------------|

| SiTime SiT8008BI oscillator, U22 | • PS_CLK              | 33.333333 MHz | Zynq MPSoC U1 PS Config Bank 503, pin U24     |

| SiTime SiT8008AI oscillator, U12 | • USB0_CLK            | 52.000000 MHz | USB2 transceiver PHY U11, pin 26              |

| SiTime SiT8008AI oscillator, U16 | • OSCI                | 12.000000 MHz | FTDI FT2232H U4, pin 3                        |

| Kyocera CX3225SB30000, Y1        | -                     | 30.000 MHz    | FTDI FT601Q U9, pin 21/22                     |

| CM-2012-2pad, Y2                 | -                     | 32.768000 kHz | Zynq MPSoC U1 PS Config Bank 503, pin V21/V22 |

| Kyocera CX3225SB26000, Y3        | • XAXB_P<br>• XAXB_N  | 54.000 MHz    | 10-output PLL clock generator U14, pin 8/9    |

| SiTime SiT8008BI oscillator, U21 | • ETH_CLKIN           | 25.000000 MHz | Gigabit Ethernet PHY U20, pin 34              |

| ASVTX-12-A oscillator, U75       | • IN0_P               | 40.000 MHz    | 10-output PLL clock generator U14, pin 63     |

#### TEC0850 on-board oscillators

### **FTDIs**

The TEC0850 board is equipped with 2 FTDI chips FT2232H (U4) and FT601Q (U9). Both chips are USB to Multipurpose UART/FIFO bridges which converts signals from USB2 or USB3 to a variety of standard serial and parallel interfaces.

TEC0850 on-board FTDI chips

#### FT2232H

The TEC0850 board is equipped with the FTDI FT2232H USB2 to JTAG/UART adapter controller connected to micro-USB2 connector J9 to provide JTAG and UART access to the Xilinx UltraScale+ Zynq SoC or Intel MAX10 (switchable over DIP). There is also a 256-byte configuration EEPROM U6 wired to the FT2232H chip via Microwire bus which holds pre-programmed license code to support Xilinx programming tools. Refer to the FTDI datasheet to get information about the capacity of the FT2232H chip.

Do not access the FT2232H EEPROM using FTDI programming tools, doing so will erase normally invisible user EEPROM content and invalidate stored Xilinx JTAG license. Without this license, the onboard JTAG will not be accessible anymore with any Xilinx tools. Software tools from the FTDI website do not warn or ask for confirmation before erasing user EEPROM content.

Channel A of the FTDI IC is configured as JTAG interface (MPSSE) connected to the SC FPGA U18, the JTAG signals are forwarded to the JTAG interface of the Zynq MPSoC on PS config bank 503.

Channel B can be used as UART Interface routed to SC FPGA U18, 11 I/O's of Channel B is routed to are usable for example as GPIOs and other standard interfaces.

| FT2232H U3 Pin | Signal Schematic Name | Connected to                | Notes          |

|----------------|-----------------------|-----------------------------|----------------|

| Pin 12, ADBUS0 | ADBUS0                | SC FPGA U18 bank 6, pin G9  | JTAG interface |

| Pin 13, ADBUS1 | ADBUS1                | SC FPGA U18 bank 6, pin F10 |                |

| Pin 14, ADBUS2 | ADBUS2                | SC FPGA U18 bank 6, pin E10 |                |

| Pin 15, ADBUS3         | ADBUS3   | SC FPGA U18 bank 6, pin D9  |                   |

|------------------------|----------|-----------------------------|-------------------|

| Pin 32, BDBUS0         | BDBUS0   | SC FPGA U18 bank 6, pin B11 | UART and          |

| Pin 33, BDBUS1         | BDBUS1   | SC FPGA U18 bank 6, pin A12 | user configurable |

| Pin 34, BDBUS2         | BDBUS2   | SC FPGA U18 bank 6, pin B12 | GPIO's            |

| Pin 35, BDBUS3         | BDBUS3   | SC FPGA U18 bank 6, pin C11 |                   |

| Pin 37, BDBUS4         | BDBUS4   | SC FPGA U18 bank 6, pin B13 |                   |

| Pin 38, BDBUS5         | BDBUS5   | SC FPGA U18 bank 6, pin C12 |                   |

| Pin 39, BDBUS6         | BDBUS6   | SC FPGA U18 bank 6, pin C13 |                   |

| Pin 40, BDBUS7         | BDBUS7   | SC FPGA U18 bank 6, pin D11 |                   |

| Pin 42, BCBUS0         | BCBUS0   | SC FPGA U18 bank 6, pin D12 |                   |

| Pin 46, BCBUS1         | BCBUS1   | SC FPGA U18 bank 6, pin E13 |                   |

| Pin 47, BCBUS2         | BCBUS2   | SC FPGA U18 bank 6, pin E12 |                   |

| Pin 48, BCBUS3         | BCBUS3   | SC FPGA U18 bank 6, pin F13 |                   |

| Pin 49, BCBUS4         | BCBUS4   | SC FPGA U18 bank 6, pin F12 |                   |

| Pin 11, nRESET         | FTDI_RST | SC FPGA U18 bank 6, pin E9  | control signals   |

| ET2222H interface conn | actions  |                             |                   |

FT2232H interface connections

### FT601Q

The TEC0850 board is equipped with the FTDI FT601Q USB3 to 32bit-FIFO adapter controller connected to USB-C connector J10 to provide access to the Zynq MPSoC PL HP I/O's of bank 64. Also, 13 control signals of the FTDI FT601Q are connected to the HP bank 64.

| FT601Q U9 Pin  | Signal Schematic Name | Connected to            | Notes       |

|----------------|-----------------------|-------------------------|-------------|

| Pin 40, DATA0  | DATA0                 | PL HP bank 64, pin AK1  | user GPIO's |

| Pin 41, DATA1  | DATA1                 | PL HP bank 64, pin AJ10 |             |

| Pin 42, DATA2  | DATA2                 | PL HP bank 64, pin AJ9  |             |

| Pin 43, DATA3  | DATA3                 | PL HP bank 64, pin AK7  |             |

| Pin 44, DATA4  | DATA4                 | PL HP bank 64, pin AK5  |             |

| Pin 45, DATA5  | DATA5                 | PL HP bank 64, pin AM1  |             |

| Pin 46, DATA6  | DATA6                 | PL HP bank 64, pin AL2  |             |

| Pin 47, DATA7  | DATA7                 | PL HP bank 64, pin AK4  |             |

| Pin 50, DATA8  | DATA8                 | PL HP bank 64, pin AN1  |             |

| Pin 51, DATA9  | DATA9                 | PL HP bank 64, pin AL3  |             |

| Pin 52, DATA10 | DATA10                | PL HP bank 64, pin AK8  |             |

| Pin 53, DATA11 | DATA11                | PL HP bank 64, pin AN2  |             |

| Pin 54, DATA12 | DATA12                | PL HP bank 64, pin AP2  |             |

| Pin 55, DATA13 | DATA13                | PL HP bank 64, pin AL7  |             |

| Pin 56, DATA14 | DATA14                | PL HP bank 64, pin AL5  |             |

| Pin 57, DATA15 | DATA15                | PL HP bank 64, pin AM4  |             |

| Pin 60, DATA16 | DATA16                | PL HP bank 64, pin AN4  |             |

| Pin 61, DATA17 | DATA17                | PL HP bank 64, pin AM5  |             |

| Pin 62, DATA18 | DATA18                | PL HP bank 64, pin AM6  |             |

| Pin 63, DATA19  | DATA19       | PL HP bank 64, pin AN3  |                 |

|-----------------|--------------|-------------------------|-----------------|

| Pin 64, DATA20  | DATA20       | PL HP bank 64, pin AP3  |                 |

| Pin 65, DATA21  | DATA21       | PL HP bank 64, pin AP4  |                 |

| Pin 66, DATA22  | DATA22       | PL HP bank 64, pin AP5  |                 |

| Pin 67, DATA23  | DATA23       | PL HP bank 64, pin AN6  |                 |

| Pin 69, DATA24  | DATA24       | PL HP bank 64, pin AN7  |                 |

| Pin 70, DATA25  | DATA25       | PL HP bank 64, pin AP6  |                 |

| Pin 71, DATA26  | DATA26       | PL HP bank 64, pin AP7  |                 |

| Pin 72, DATA27  | DATA27       | PL HP bank 64, pin AP11 |                 |

| Pin 73, DATA28  | DATA28       | PL HP bank 64, pin AP10 |                 |

| Pin 74, DATA29  | DATA29       | PL HP bank 64, pin AP9  |                 |

| Pin 75, DATA30  | DATA30       | PL HP bank 64, pin AN9  |                 |

| Pin 76, DATA31  | DATA31       | PL HP bank 64, pin AP8  |                 |

| Pin 58, CLK     | FIFO_CLK     | PL HP bank 64, pin AL6  | control signals |

| Pin 4, BE0      | BE_0         | PL HP bank 64, pin AM10 |                 |

| Pin 5, BE1      | BE_1         | PL HP bank 64, pin AK10 |                 |

| Pin 6, BE2      | BE_2         | PL HP bank 64, pin AM11 |                 |

| Pin 7, BE3      | BE_3         | PL HP bank 64, pin AL11 |                 |

| Pin 13, nOE     | OE_N         | PL HP bank 64, pin AL8  |                 |

| Pin 12, nRD     | RD_N         | PL HP bank 64, pin AK9  |                 |

| Pin 11, nWR     | WR_N         | PL HP bank 64, pin AM9  |                 |

| Pin 8, nTXE     | TXE_N        | PL HP bank 64, pin AK12 |                 |

| Pin 9, nRXN     | RXF_N        | PL HP bank 64, pin AJ12 |                 |

| Pin 10, nSIWU   | SIWU_N       | PL HP bank 64, pin AL10 |                 |

| Pin 15, nRESET  | FTDI_RESET_N | PL HP bank 64, pin AM8  |                 |

| Pin 16, nWAKEUP | WAKEUP_N     | PL HP bank 64, pin AN8  |                 |

|                 |              |                         |                 |

FT601Q interface connections

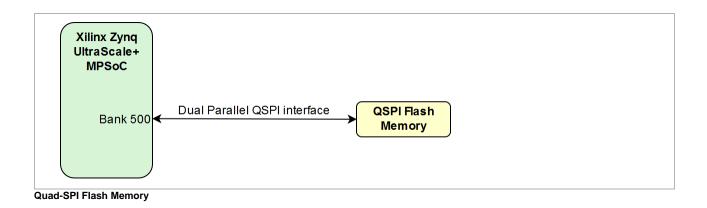

### **Quad-SPI Flash Memory**

On-board QSPI flash memory U24 and U25 on the TEC0850 board is provided by Micron Serial NOR Flash Memory N25Q256A with 256 Mbit (32 MByte) storage capacity each, 64 MByte total QSPI Flash memory. The QSPI Flash memory ICs are connected to the PS MIO bank (Dual QSPI MIO0 ... MIO12) of the Zynq Ultrascale+ MPSoC, enabling dual parallel booting from QSPI Flash memory. This nonvolatile memory is used to store an initial FPGA configuration. Besides FPGA configuration, remaining free flash memory can be used for user application and data storage. All four SPI data lines are connected to the Zynq MPSoC allowing x1, x2 or x4 data bus widths. Maximum data rate depends on the selected bus width and clock frequency used.

| IC               | Memory Density      | MIO | Signal Schematic Name | Flash Memory Pin |

|------------------|---------------------|-----|-----------------------|------------------|

| QSPI Flash U24,  | 256 Mbit (32 MByte) | 0   | MIO0                  | B2               |

| N25Q256A11E1240E |                     | 1   | MIO1                  | D2               |

|                  |                     | 2   | MIO2                  | C4               |

|                  |                     | 3   | MIO3                  | D4               |

|                  | 4                   | 4   | MIO4                  | D3               |

|                  |                     | 5   | MIO5                  | C2               |

| QSPI Flash U25,  | 256 Mbit (32 MByte) | 7   | MIO7                  | C2               |

| N25Q256A11E1240  |                     | 8   | MIO8                  | D3               |

|                  |                     | 9   | MIO9                  | D2               |

|                  |                     | 10  | MIO10                 | C4               |

|                  |                     | 11  | MIO11                 | D4               |

|                  |                     | 12  | MIO12                 | B2               |

Quad-SPI Flash memory interface connections

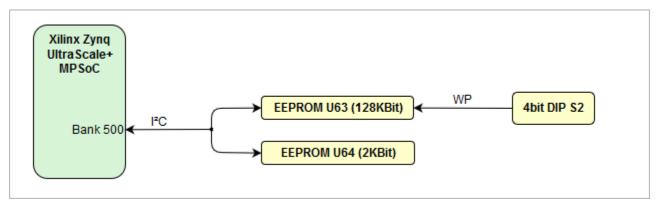

### **EEPROMs**

The TEC0850 board contains several EEPROMs for configuration and general user purposes. The EEPROMs are provided by Microchip, the I<sup>2</sup>C interfaces are connected to Zynq MPSoC bank 502 MIO 20...21 pins:

#### **On-board configuration EEPROMs**

The EEPROMs U63 and U64 are programmable via the onboard I<sup>2</sup>C bus connected to MIO 20...21 pins. The I<sup>2</sup>C address is shown in the table below.

| I2C address | Chip                 | Description                                                                    |

|-------------|----------------------|--------------------------------------------------------------------------------|

| 0x50        | U63 24AA128T-I/ST    | 128K Serial EEPROM                                                             |

| 0x53        | U64 24AA025E48T-I/OT | 2K Serial EEPROM with EUI-48 <sup>™</sup> or EUI-64 <sup>™</sup> Node Identity |

EEPROMs I<sup>2</sup>C Addresses

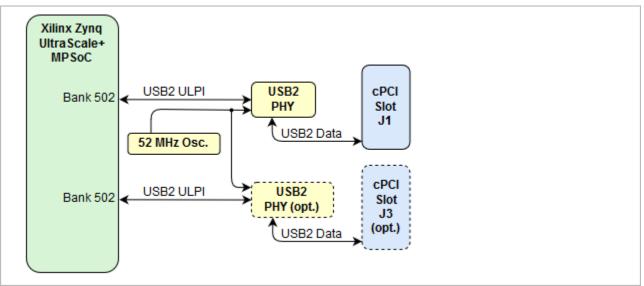

### **USB2 PHY**

USB2 PHY U11 is provided by USB3320 from Microchip. The ULPI interface is connected to the Zynq Ultrascale+ PS USB0. I/O voltage is fixed at 1.8V and PHY reference clock input is supplied from the on-board 52.000000 MHz oscillator U12. There is also the option to equip the TEC0850 board with a second USB2 PHY U13 connected to the optional cPCI backplane connector J3. Both, the optional USB2 PHY U13 and cPCI connector J3 are not fitted by default.

### TEC0850 cPCI USB2 interface

| USB2 PHY U11 Pin | Connected to               | Notes                                                                              |

|------------------|----------------------------|------------------------------------------------------------------------------------|

| ULPI             | PS bank MIO52 MIO63        | Zynq Ultrascale+ USB0 MIO pins are connected to the PHY                            |

| REFCLK           | -                          | 52MHz from onboard oscillator U12                                                  |

| REFSEL[02]       | -                          | All pins set to GND selects the external reference clock frequency (52.000000 MHz) |

| RESETB           | Zynq MPSoC MIO16, pin AM16 | Low active USB2 PHY Reset                                                          |

| DP, DM           | cPCI connector J1          | USB2 data lane                                                                     |

| CPEN             | -                          | External USB power switch active-high enable signal                                |

| VBUS             | 5V                         | Connected to onboard 5V voltage level via a series of resistors, see schematic     |

| ID               | 3.3V                       | USB2 OTG A-Device (host)                                                           |

| optional USB2 PHY U13 Pin | Connected to               | Notes                                                                              |

|---------------------------|----------------------------|------------------------------------------------------------------------------------|

| ULPI                      | PS bank MIO64 MIO75        | Zynq Ultrascale+ USB1 MIO pins are connected to the PHY                            |

| REFCLK                    | -                          | 52MHz from onboard oscillator U12                                                  |

| REFSEL[02]                | -                          | All pins set to GND selects the external reference clock frequency (52.000000 MHz) |

| RESETB                    | Zynq MPSoC MIO17, pin AP16 | Low active USB2 PHY Reset                                                          |

| DP, DM                    | optional cPCI connector J3 | USB2 data lane                                                                     |

| CPEN                      | -                          | External USB power switch active-high enable signal                                |

| VBUS                      | 5V                         | Connected to onboard 5V voltage level via a series of resistors, see schematic     |

| ID                        | 3.3V                       | USB2 OTG A-Device (host)                                                           |

USB2 ULPI interface description

## **Gigabit Ethernet PHY**

Onboard Gigabit Ethernet PHY U20 is provided with Marvell Alaska 88E1512, which use MDIO address 1. The Ethernet PHY RGMII interface is connected to the Zynq Ultrascale+ Ethernet0 PS GEM3. I/O voltage is fixed at 1.8V for HSTL signaling. The reference clock input of the PHY is supplied from the onboard 25.000000 MHz oscillator U21.

TEC0850 GbE interface with RJ-45 MegJack

### **8bit DACs**

The TEC0850 Board has 4 8-bit parallel Texas Instruments THS5641AIPW digital to analog converter (DAC) with up to 100 MSPS update rate connected to TI THS4631D operational amplifiers. See Schematic circuitry and TI THS5641 data sheet for proper operation of the on-board DAC units.

| DAC unit | Signal Schematic Name | Connected to                                                       | Functionality                               |

|----------|-----------------------|--------------------------------------------------------------------|---------------------------------------------|

| DAC1     | DAC1_D0               | PL HD bank 50, pin D11                                             | Digital input bits D[7:0]                   |

| U28      | DAC1_D1               | PL HD bank 50, pin D10                                             |                                             |

|          | DAC1_D2               | PL HD bank 50, pin G11                                             | D7 is the most significant data bit (MSB),  |

|          | DAC1_D3               | PL HD bank 50, pin J11 D0 is the least significant data bit (LSB). | D0 is the least significant data bit (LSB). |

|          | DAC1_D4               | PL HD bank 50, pin G10                                             |                                             |

|          | DAC1_D5               | PL HD bank 50, pin H10                                             |                                             |

|          | DAC1_D6               | PL HD bank 50, pin J10                                             |                                             |

|          | DAC1_D7               | PL HD bank 50, pin E10                                             |                                             |

|      | DAC1_CLK  | PL HD bank 50, pin F12     | External clock input, input data latched on rising edge of the clock.                     |  |

|------|-----------|----------------------------|-------------------------------------------------------------------------------------------|--|

|      | DAC1_MODE | PL HD bank 50, pin F10     | Input code format (binary, twos complement)                                               |  |

|      | EN_DAC1   | SC FPGA U18 bank 8, pinE6  | generate 3.3V voltages<br>LDO U35, U34                                                    |  |

| DAC2 | DAC2_D0   | PL HD bank 50, pin G15     | Digital input bits D[7:0]                                                                 |  |

| U31  | DAC2_D1   | PL HD bank 50, pin H14     |                                                                                           |  |

|      | DAC2_D2   | PL HD bank 50, pin J14     | D7 is the most significant data bit (MSB),                                                |  |

|      | DAC2_D3   | PL HD bank 50, pin G14     | D0 is the least significant data bit (LSB).                                               |  |

|      | DAC2_D4   | PL HD bank 50, pin G13     |                                                                                           |  |

|      | DAC2_D5   | PL HD bank 50, pin H13     |                                                                                           |  |

|      | DAC2_D6   | PL HD bank 50, pin H12     |                                                                                           |  |

|      | DAC2_D7   | PL HD bank 50, pin J12     |                                                                                           |  |

|      | DAC2_CLK  | PL HD bank 50, pin F12     | External clock input, input data latched on rising edge of the clock.                     |  |

|      | DAC2_MODE | PL HD bank 50, pin F11     | Input code format (binary, twos complement)                                               |  |

|      | EN_DAC2   | SC FPGA U18 bank 8, pin E8 | generate 3.3V voltages<br>LDO U32, U60                                                    |  |

| DAC3 | DAC3_D0   | PL HD bank 44, pin AG14    | Digital input bits D[7:0]                                                                 |  |

| U29  | DAC3_D1   | PL HD bank 44, pin AE13    |                                                                                           |  |

|      | DAC3_D2   | PL HD bank 44, pin AG13    | D7 is the most significant data bit (MSB),<br>D0 is the least significant data bit (LSB). |  |

|      | DAC3_D3   | PL HD bank 44, pin AJ15    |                                                                                           |  |

|      | DAC3_D4   | PL HD bank 44, pin AJ14    |                                                                                           |  |

|      | DAC3_D5   | PL HD bank 44, pin AH14    |                                                                                           |  |

|      | DAC3_D6   | PL HD bank 44, pin AL13    |                                                                                           |  |

|      | DAC3_D7   | PL HD bank 44, pin AM13    |                                                                                           |  |

|      | DAC3_CLK  | PL HD bank 44, pin AK15    | External clock input, input data latched on rising edge of the clock.                     |  |

|      | DAC3_MODE | PL HD bank 44, pin AK14    | Input code format (binary, twos complement)                                               |  |

|      | EN_DAC3   | SC FPGA U18 bank 8, pin B6 | generate 3.3V voltages<br>LDO U66, U68                                                    |  |

| DAC4 | DAC4_D0   | PL HD bank 44, pin AP14    | Digital input bits D[7:0]                                                                 |  |

| U33  | DAC4_D1   | PL HD bank 44, pin AN14    |                                                                                           |  |

|      | DAC4_D2   | PL HD bank 44, pin AM14    | D7 is the most significant data bit (MSB),                                                |  |

|      | DAC4_D3   | PL HD bank 44, pin AN13    | D0 is the least significant data bit (LSB).                                               |  |

|      | DAC4_D4   | PL HD bank 44, pin AP12    |                                                                                           |  |

|      | DAC4_D5   | PL HD bank 44, pin AN12    |                                                                                           |  |

|      | DAC4_D6   | PL HD bank 44, pin AF13    |                                                                                           |  |

|      | DAC4_D7   | PL HD bank 44, pin AH13    |                                                                                           |  |

|      | DAC4_CLK  | PL HD bank 44, pin AK13    | External clock input, input data latched on rising edge of the clock.                     |  |

|      | DAC4_MODE | PL HD bank 44, pin AK13    | Input code format (binary, twos complement)                                               |  |

|      | EN_DAC4   | SC FPGA U18 bank 8, pin A6 | generate 3.3V voltages<br>LDO U70, U72                                                    |  |

DAC units interface description

### **DIP-Switches**

There are two 4-bit DIP-witches S3 and S4 present on the TEC0850 board to configure options and set parameters. The following section describes the functionalities of the particular switches.

The table below describes the functionalities of the switches of DIP-switches S1 and S2 at their every position:

| DIP-<br>switch S1 | Signal Schematic<br>Name | Connected to                              | Functionality                                                                    | Notes                                                      | Notes      |               |              |            |

|-------------------|--------------------------|-------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------|------------|---------------|--------------|------------|

| S1-1              | JTAGEN                   | SC FPGA U18, bank 1B, pin E5              | Positions:<br>OFF: SC FPGA's JTAG<br>enabled<br>ON: Zynq MPSoC's JTAG<br>enabled | to switch the JTAG interface between SC FPGA an Zynq MPSoC |            |               |              |            |

| S1-2              | WP                       | EEPROM U63, pin 7                         | Positions:<br>OFF: Write Protect is enabled<br>ON: Write Protect is disabled     | -                                                          |            |               |              |            |

| S1-3              | PUDC_B                   | Zynq MPSOC PS Config Bank 503, pin AD15   | Positions:<br>ON: PUDC_B is Low<br>OFF: PUDC_B is HIGH                           | Internal pul<br>are enabled<br>until the co                | d at ON-   | oosition, m   | eans I/O's a | are 3-stat |

| S1-4              | SW4                      | SC FPGA U18, bank 8, pin A5               | GA U18, bank 8, pin A5 SC Switch (Reserved for future use)                       |                                                            | ogic       |               |              |            |

| DIP-<br>switch S2 | Signal Schematic<br>Name | Connected to                              | Functionality                                                                    | Notes                                                      |            |               |              |            |

| S2-1              | MODE3                    | Zynq MPSOC PS Config Bank 503,<br>pin R23 | set 4-bit code for boot mode selection                                           | See Zynq L<br>Manual                                       |            |               |              | Reference  |

| S2-2              | MODE2                    | Zynq MPSOC PS Config Bank 503, pin T23    | _                                                                                | page 236 fo                                                | or full do | ot modes d    | lescription  |            |

| S2-3              | MODE1                    | Zynq MPSOC PS Config Bank 503,<br>pin R22 | _                                                                                | Set DIP-sw                                                 | itches as  | s bit patterr | n of S2      |            |

| S2-4              | MODE0                    | Zynq MPSOC PS Config Bank 503, pin T22    |                                                                                  | BOOT<br>Mode                                               | 1          | 2             | 3            | 4          |