## **TE0710 CPLD**

#### Table of contents Overview

Firmware for SCB1CFLD with designator **U4**. CPLD Device in Chain: LCMX02-256HC

1.2 Firmware Revision and supported PCB Revision

## \* 2 Product Specification \*\*Feature 24th Maskyn \*\* 2.2 Functional Description \*\* JTAG routing 2.2.1 JTAG \*\* Reset 2.2.2 Reset

- Reset

- - 2.2.7 I2C Interface

## Firmware 1 Revision and Legal Natices ported PCB Revision o 3.2 Document Ghange History See Document Ghange Historyes

- 3.4 Data Privacy

# o 3.4 Data Privacy o 3.5 Document Warranty o 3.6 Limitation of Liability Product 3 Document Warranty o 3.8 Technology Licenses o 3.9 Environmental Protection

## Port Description PoHS and WEEE

| Name     | Direction | Pin | Pullup/down | Bank Power | Description                                                                                                      |

|----------|-----------|-----|-------------|------------|------------------------------------------------------------------------------------------------------------------|

| DONE     | in        | 13  | UP          | LVCMOS33   | FPGA DONE signal                                                                                                 |

| EN1      | in        | 16  | UP          | LVCMOS33   | B2B Enable Pin - low active                                                                                      |

| F_TCK    | out       | 28  | -           | LVCMOS33   | JTAG FPGA                                                                                                        |

| F_TDI    | out       | 27  | -           | LVCMOS33   | JTAG FPGA                                                                                                        |

| F_TDO    | in        | 23  | -           | LVCMOS33   | JTAG FPGA                                                                                                        |

| F_TMS    | out       | 25  | -           | LVCMOS33   | JTAG FPGA                                                                                                        |

| JTAGSEL  | in        | 26  | NONE        | LVCMOS33   | Enable JTAG<br>access to CPLD<br>for Firmware<br>update (zero:<br>JTAG routed to<br>module, one:<br>CPLD access) |

| BOOTMODE | in        | 11  | UP          | LVCMOS33   | B2B Boot Mode Pin                                                                                                |

| NOSEQ    | in        | 12  | UP          | LVCMOS33   | B2B NOSEQ Pin                                                                                                    |

| PG_ALL   | in        | 10  | UP          | LVCMOS33   | Power good - low<br>active, from power<br>monitor U23                                                            |

| PGOOD    | out       | 14  | UP          | LVCMOS33   | B2B PGOOD                                                                                                        |

| PROG_B   | out       | 17  | UP          | LVCMOS33   | FPGA PROG_B<br>Reset                                                                                             |

| SC_nRST    | in  | 8  | UP   | LVCMOS33 | B2B Reset - low active                                               |

|------------|-----|----|------|----------|----------------------------------------------------------------------|

| SYSLED1    | out | 9  | NONE | LVCMOS33 | Green LED D2                                                         |

| SYSLED2    | out | 5  | NONE | LVCMOS33 | Red LED D1                                                           |

| TCK        | in  | 30 | NONE | LVCMOS33 | JTAG B2B                                                             |

| TDI        | in  | 32 | DOWN | LVCMOS33 | JTAG B2B                                                             |

| TDO        | out | 1  | NONE | LVCMOS33 | JTAG B2B                                                             |

| TMS        | in  | 29 | DOWN | LVCMOS33 | JTAG B2B                                                             |

| ULI_2      | out | 20 | UP   | LVCMOS15 | FPGA Bank 35 Pin<br>J5 - I2C CLOCK<br>Pin to FPGA                    |

| ULI_CPLD   | out | 4  | NONE | LVCMOS33 | J1 (Ultra Small<br>Surface Mount<br>Coax)                            |

| ULI_SYSTEM | in  | 21 | UP   | LVCMOS15 | FPGA Bank 35 Pin<br>G3 - I2C DATA<br>Pin to FPGA or<br>input for UFL |

## **Functional Description**

#### **JTAG**

JTAG signals routed directly through the CPLD to FPGA. Access between CPLD and FPGA can be multiplexed via JTA GEN (logical one for CPLD, logical zero for FPGA) on JM1-89.

#### Reset

PROG\_B is triggered by SC\_nRST or PG\_ALL or EN1 after power on delay.

#### **Power**

PGOOD is '0' when PG\_ALL or EN1 is '0', else high impedance.

#### **USER IO**

Various signals are connected to an I2C register.

I2C GPIO\_input register Bit 15 downto Bit 9 contain SC\_nRST, BOOTMODE, PGOOD, EN1, DONE, PG\_ALL and NOS EQ.

Their state can be read from FPGA side over I2C.

$\emph{ULI\_SYSTEM}$  serves as the I2C data pin but is also connected to  $\emph{ULI\_CPLD}$ .

#### **USER IO**

MODE\_SC1 is connected to a I2C Register bit. GPIO\_input(18). Its state can be read from FPGA side over I2C.

$\emph{UIO}$  is connected to  $\emph{UFL}$  but also serves as the I2C data pin.

### LED

RED LED D1 (SYSLED2) shows a certain blinking pattern in case one of the status signals is active, otherwise it can be controlled via I2C from FPGA side or is simply OFF.

| Blink sequence | Priority | Condition                 | Description                                                    |

|----------------|----------|---------------------------|----------------------------------------------------------------|

|                | highest  | SC_nRST= LOW (low active) | external reset from carrier is pressed                         |

| *******0       |          |                           | blink sequence not used                                        |

| *****00        |          |                           | blink sequence not used                                        |

| *****000       |          | PG_ALL is zero            | One of the power rails of the internal Voltages DCDCs is down  |

| ****0000       |          | EN1 is zero               | B2B enable Pin is active (low active), coming from the carrier |

| ***00000       |          |                           | blink sequence not used                                        |

| **00000        |          |                           | blink sequence not used                                        |

| *0000000         |        | DONE = '0'                                                                                                  | FPGA not programmed. No design on QSPI Flash?                      |

|------------------|--------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| continuously ON  | lowest | software controlled<br>command via I2C<br>Interface.<br>LED = GPIO_output<br>(1) when<br>GPIO_output(0) = 0 | Set bit GPIO_output(0) LOW to control the LED with GPIO_output(1). |

| continuously OFF |        |                                                                                                             | If none of the above condition is met                              |

GREEN LED D2 (SYSLED1) software controlled command via I2C Interface or is simply OFF.

| Blink<br>sequence   | Condition                                                                                   | Description                                                        |

|---------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| continuously<br>ON  | software controlled command via I2C Interface. LED = GPIO_output(3) when GPIO_output(2) = 0 | Set bit GPIO_output(2) LOW to control the LED with GPIO_output(3). |

| continuously<br>OFF |                                                                                             | If none of the above condition is met                              |

#### **I2C Interface**

This subsystem provides 2 x 32-bit (segmented in eight 8-bit) of general purpose parallel input and output (I/O) expansion for the I2C bus protocol. Address of this I2C device is 0x20. This module contains eight 8-bit registers for reading and writing (GPIO\_input[7:0] to GPIO\_input[31:24] and GPIO\_output[7:0] to GPIO\_output[31:24]) separately with address 0x00 to 0x03. These registers can be accessed with I2C commands on a standalone application or, more simply, from petalinux running on the Microblaze. Refer to TE0710 reference design (test board).

```

root&petalinux:-# i2cdetect -1

i2c-0 i2c xiic-i2c 40800000.i2c 12c

adapter

root&petalinux:-# i2cget -y 0 0x20 0x00

0x03

root&petalinux:-# i2cget -y 0 0x20 0x01

0xfe

root&petalinux:-# i2cget -y 0 0x20 0x02

0x01

root&petalinux:-# i2cget -y 0 0x20 0x02

0x01

root&petalinux:-# i2cget -y 0 0x20 0x03

root&petalinux:-# i2cget -y 0 0x20 0x03

root&petalinux:-# i2cset -y 0 0x20 0x00

```

Four registers can be read and four can be written.

| GPIO_input(7 downto 0)      | readab<br>le  | 0x00 | contains the CPLD Firmware Revision (not the PCB revision)                                               |

|-----------------------------|---------------|------|----------------------------------------------------------------------------------------------------------|

| GPIO_input(15 downto 8)     | readab<br>le  | 0x01 | SC_nRST, BOOTMODE, PGOOD, EN1, DONE, PG_ALL, NOSEQ, '0'                                                  |

| GPIO_input(23<br>downto 16) | readab<br>le  | 0x02 | contains: NOSEQ state in bit 16.                                                                         |

| GPIO_input(31<br>downto 24) | readab<br>le  | 0x03 | empty                                                                                                    |

| GPIO_output(7 downto 0)     | writea<br>ble | 0x00 | Bit 1 to 3 are mapped to SYSLED1 and SYSLED2. Write '1' to Bit 1 and Bit 3 to turn on the LED D1 and D2. |

| GPIO_output(15 downto 8)    | writea<br>ble | 0x01 | not mapped                                                                                               |

| GPIO_output(23 downto 16)   | writea<br>ble | 0x02 | Bit 16 is mapped to NOSEQ if no reset occurs                                                             |

| GPIO_output(31 downto 24)   | writea<br>ble | 0x03 | not mapped                                                                                               |

## Appx. A: Change History and Legal Notices

## **Revision Changes**

changes Firmware REV02(old version) to REV03:

- Signals are renamed according to the schematic.

- NOSEQ pin is added.

- LED function changed. New blinking pattern for critical signal states

- I2C to GPIO slave added

- SC\_nRST, BOOTMODE, PGOOD, EN1, DONE, PG\_ALL, NOSEQ signals can be read from I2C

- CPLD\_REVISION as generic parameter added

- NOSEQ defined as INOUT

- ULI\_SYSTEM and ULI\_2 pins defined as I2C pins. Added PullUps for I2C. ULI\_SYSTEM is still also connected to ULI\_CPLD

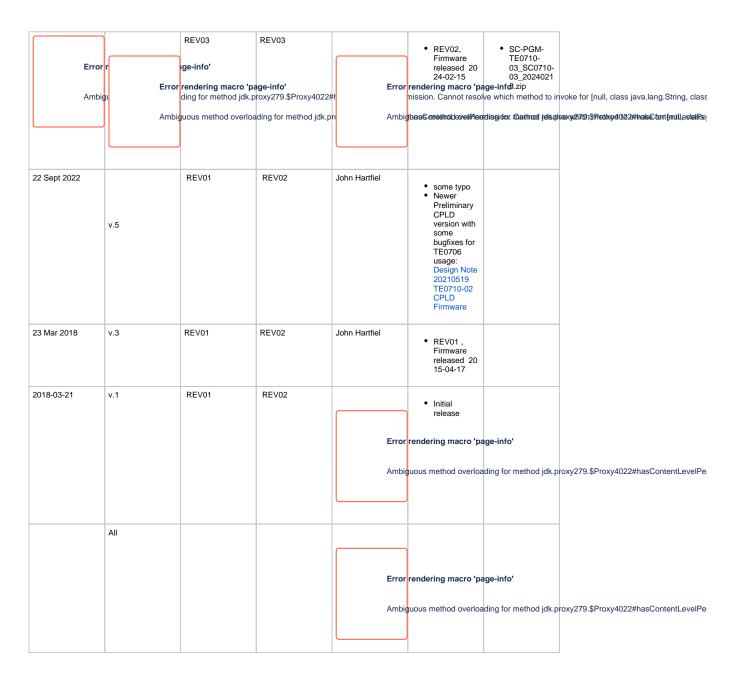

## **Document Change History**

To get content of older revision got to "Change History" of this page and select older document revision number.

## **Legal Notices**

## **Data Privacy**

Please also note our data protection declaration at https://www.trenz-electronic.de/en/Data-protection-Privacy

## **Document Warranty**

The material contained in this document is provided "as is" and is subject to being changed at any time without notice. Trenz Electronic does not warrant the accuracy and completeness of the materials in this document. Further, to the maximum extent permitted by applicable law, Trenz Electronic disclaims all warranties, either express or implied, with regard to this document and any information contained herein, including but not limited to the implied warranties of merchantability, fitness for a particular purpose or non infringement of intellectual property. Trenz Electronic shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein.

#### **Limitation of Liability**

In no event will Trenz Electronic, its suppliers, or other third parties mentioned in this document be liable for any damages whatsoever (including, without limitation, those resulting from lost profits, lost data or business interruption) arising out of the use, inability to use, or the results of use of this document, any documents linked to this document, or the materials or information contained at any or all such documents. If your use of the materials or information from this document results in the need for servicing, repair or correction of equipment or data, you assume all costs thereof.

#### **Copyright Notice**

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Trenz Electronic.

#### **Technology Licenses**

The hardware / firmware / software described in this document are furnished under a license and may be used /modified / copied only in accordance with the terms of such license.

#### **Environmental Protection**

To confront directly with the responsibility toward the environment, the global community and eventually also oneself. Such a resolution should be integral part not only of everybody's life. Also enterprises shall be conscious of their social responsibility and contribute to the preservation of our common living space. That is why Trenz Electronic invests in the protection of our Environment.

### **REACH, RoHS and WEEE**

#### **REACH**

Trenz Electronic is a manufacturer and a distributor of electronic products. It is therefore a so called downstream user in the sense of REACH. The products we supply to you are solely non-chemical products (goods). Moreover and under normal and reasonably foreseeable circumstances of application, the goods supplied to you shall not release any substance. For that, Trenz Electronic is obliged to neither register nor to provide safety data sheet. According to present knowledge and to best of our knowledge, no SVHC (Substances of Very High Concern) on the Candidate List are contained in our products. Furthermore, we will immediately and unsolicited inform our customers in compliance with REACH - Article 33 if any substance present in our goods (above a concentration of 0,1 % weight by weight) will be classified as SVHC by the European Chemicals Agency (ECHA).

#### **RoHS**

Trenz Electronic GmbH herewith declares that all its products are developed, manufactured and distributed RoHS compliant.

#### WEEE

Information for users within the European Union in accordance with Directive 2002/96/EC of the European Parliament and of the Council of 27 January 2003 on waste electrical and electronic equipment (WEEE).

Users of electrical and electronic equipment in private households are required not to dispose of waste electrical and electronic equipment as unsorted municipal waste and to collect such waste electrical and electronic equipment separately. By the 13 August 2005, Member States shall have ensured that systems are set up allowing final holders and distributors to return waste electrical and electronic equipment at least free of charge. Member States shall ensure the availability and accessibility of the necessary collection facilities. Separate collection is the precondition to ensure specific treatment and recycling of waste electrical and electronic equipment and is necessary to achieve the chosen level of protection of human health and the environment in the European Union. Consumers have to actively contribute to the success of such collection and the return of waste electrical and electronic equipment. Presence of hazardous substances in electrical and electronic equipment results in potential effects on the environment and human health. The symbol consisting of the crossed-out wheeled bin indicates separate collection for waste electrical and electronic equipment.

Trenz Electronic is registered under WEEE-Reg.-Nr. DE97922676.

#### Error rendering macro 'page-info'

Ambiguous method overloading for method jdk.proxy279.\$Proxy4022#hasContentLevelPermission.

Cannot resolve which method to invoke for [null, class java.lang.String, class com.atlassian.confluence.

pages.Page] due to overlapping prototypes between: [interface com.atlassian.confluence.user.

ConfluenceUser, class java.lang.String, class com.atlassian.confluence.core.ContentEntityObject]

[interface com.atlassian.user.User, class java.lang.String, class com.atlassian.confluence.core.

ContentEntityObject]