| Page properties |

|---|

|

Template Revision 1.0 - on construction Design Name always "TE Series Name" + Design name, for example "TE0720 Test Board" |

| Page properties |

|---|

|

Important General Note: Export PDF to download, if Libero or SoftConsole revision is changed! Designate all graphics and pictures with a number and a description, Use "Scroll Title" macro - Use "Scroll Title" macro for pictures and table labels. Figure number must be set manually at the moment (automatically enumeration is planned by scrollPDF)

- ...

|

Overview

This page describes in detail which software, and their respective versions, was used to generate und use the module demonstration.

Further described is how to flash the Hardware and Software Design contained in the Demo Archieve onto the TEM0001.

A brief usage introduction for each Demo is included.

The Hardware Reference Design uses these Smartfusion 2 SoC, hard Arm® Cortex®-M3 Core, Soft SDRAM Core, Soft SPI Core, COM port, Real Time Clock and the on-board LEDs via a Soft PWM Core.

The Software Designs Hello World, SF2_GNU_SC4_pwm_slow_blink and SF2_GNU_SC4_rtc_time use the Hardware Design features to a different degree. Most notably is Hello World, which utializes all features of the Hardware and is very close to the modules production test.

Refer to UPDATE-LINK/LinkText:_TEM00XY-Resources UPDATE

for the current online version of this manual and other available documentation.

Key Features

| Page properties |

|---|

|

Notes : - Add basic key futures, which can be tested with the design / does the design use

|

| Excerpt |

|---|

- Libero 2021.2 (FPGA IDE)

- SoftConsole 2021.1 (Software IDE)

- UART

- SDR

- eNVM

- User LED access

- Real Time Clock

|

Revision History

| Page properties |

|---|

|

Notes : - add every update file on the download

- add design changes on description

|

| Scroll Title |

|---|

| title-position | top |

|---|

| anchor | Table_DRH |

|---|

| title | Table of Design Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Libero | SoftConsole | Project Built | Authors | Description |

|---|

| 2021-12-09 | 2021.2 | 2021.1 | NAME-OF-ZIP-ARCHIVE .zip | Kilian Jahn | |

|

Release Notes and Know Issues

| Page properties |

|---|

|

Notes :- add known Design issues and general notes for the current revision

- do not delete known issue, add fixed version time stamp if issue fixed

- When known issues became known/will be noted here, remove "Non known so fare.far" and the hidden artibute of the box below.

|

Non known so farefar.

| Page properties |

|---|

|

Notes : When | Scroll Title |

|---|

| title-position | top |

|---|

| anchor | Table_KI |

|---|

| title | Table of Known Issues |

|---|

| | Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Module / Variant | Issues Description | Workaround/Solution | To be fixed version |

|---|

| NAME-of-RefDes-or-Demo |

|

|

|

|

|

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

Requirements

Software

| Page properties |

|---|

|

Notes : - list of software and their versions which was used to generate the desig

|

| Scroll Title |

|---|

| title-position | top |

|---|

| anchor | Table_SW |

|---|

| title | Table of used Software and their Versions |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Software | Version | Note |

|---|

| Windows 10 | 2004 / 19041 |

| | Libero Release | 2021.2 |

| | SoftConsole | 2021.1 | Included in the Libero installation | | Microsemi Flash Pro 5 module driver | 2.10.0.0 | Utilize onboard programmer and USB / COM port connection. Included in the Libero installation | | FTDI Driver for the TEM0002 module | 2.12.28.0 |

| | UART / COM-port terminal |

| Capturing the modules messages |

|

Hardware

| Page properties |

|---|

|

Notes : - list of hardware which was used to generate the design

- ADD-IMPORTANT-Feature-of-the-FPGA, Slices, ...

|

Design supports following modules:

| Scroll Title |

|---|

| title-position | top |

|---|

| anchor | Table_HWM |

|---|

| title | Table of Hardware Modules |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Module Model | Board Part Short Name | PCB Revision Support | DDR | embedded SRAM | embedded Flash | Notes |

|---|

| TEM0001-01A-010C | SMF2000 | REV01 | 4 MB a 16 bit | 64 kB | 256 kB | NA |

|

Additional hardware Requirements:

| Scroll Title |

|---|

| title-position | top |

|---|

| anchor | Table_AHW |

|---|

| title | Table of Additional Hardware |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Additional Hardware | Notes |

|---|

| Demo host computer | Demo was created and tested on windows | | Micro USB to USB Type A Cable | Power supply, JTAG: Programming the board, UART: Communication Interface to the board. |

|

Content

The Trenz Electronic Reference Designs and Demos are usable with the specified Microsemi Libero / SoftConsole version. Usage of a different Microsemi Libero / SoftConsole software versions is not recommended.

Download

| Page properties |

|---|

|

Important ! :

|

The download is a ZIP compressed archive, it needs to be extract before usage.

Recommendation :

The path of the extracted archiev is vital for all IDE's, therefore place the extracted archiev outside the user space, e.g. "c:\Extracted_Archieve" [ Access rights / Path length limit ].

Reference Designs / Demos are available via the following link:

Design Sources

Content of the zip archive "TEM0001-RefDes_V2_0x.12.2021-1923" :

| Scroll Title |

|---|

| title-position | top |

|---|

| anchor | Table_DS |

|---|

| title | Table of Design sources |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Type | Location | Notes |

|---|

| Libero | <zip archive>

/ Libero2021.2_Hardware-Design

| Libero Project containing the modules

Hardware Reference Design | | SoftConsole | <zip archive>

/ SoftConsole2021.1_Workspace_TEM0001

/ helloWorld

/ SF2_GNU_SC4_pwm_slow_blink

/ SF2_GNU_SC4_rtc_time

| SoftConsole Workspace

contains the Software Projects : - Hello World

- Blinks a user led

- A simple clock

| | SoftConsole | <zip archive>

/ SoftConsole2021.1_Workspace_TEM0001

/ microsemi-cortex-m3.cfg | File for software debugging in

SoftConsole via "Open On Chip Debugger"

/ OpenOCD | | FlashPro Express | <zip archive>

/ FlashProExpress2021.2

/ RefDes02

/ RefDes02-HelloWorld

/ RefDes02-Zerocitation

| Programming Files to use in FlashPro Express. Omittes the usage of Libero and SoftConsole for Programming. - Reference Hardware Design for SoC and periphery

- Reference Hardware Design + Software Design Hello World

- Reference Hardware Design for zeroing the eNVM

|

|

| Page properties |

|---|

|

Currently this chapter is not needed for Microsemi projects Chapter - Design Flow The ... to use these Project ... they are This Demo / Reference Design / The Hardware and Software Reference / Demo -Designs Projects are available as a prebuild zip archive. The archive contains at least a Libero Hardware Project and a SoftConsole Workspace folder, they were created and tested in windows environment. This SoftConsole Workspace contains the Software Project ... <Name-of-the-Software-Project> . The board configuration file "NAME-of-the-Board-config-file .cfg" is required for the usage of the Software projects via the IDE SoftConsole. |

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

Launch

| Page properties |

|---|

|

Note: - Programming and Startup procedure

- Notes:

|

Executing a Reference / Demo Design on a module requires the powering of it and a JTAG or UART Connection for Programming and Communication. Often the programming is a two fold process, where the first programming configures the FPGA and the second programming flashes Software code to be executed inside the FPGA / ARM processor.

Connecting

Select a variant!

Variant without explicit power connector:

Connect the modules TYPE USB to your host pc, this enables the powering of the module and a simultaneous JTAG and UART connection .

Variant with explicit power connector:

Connect the modules TYPE USB to your host pc and power the module via its dedicated power connector (e.g. Power Jack 5 V / 2 A + inside), this enables the powering of the module and a simultaneous JTAG and UART connection .

Insert picture to ilustarte the needed connections USB/Ethernet/Power jack/... (AD-TE000XY-... .PDF / schematic picture)

Driver check

When the module is connected via USB cable to your demo host computer, in the Windows Device Manager appear the following three board driver related devices:

In section Ports (COM & LPT):

In section Universal Serial Bus controllers:

- USB FP5 Serial Converter A

- USB FP5 Serial Converter B

The Device Manager is accessible via "Right mouse click context menu" from the Windows Start Menu Button. When these devices are not visible, the driver installation through libero could be faulty.

Programming Hard and Software Designs

Before flashing any design to the module, open a terminal programm (e.g. PuTTY or SmarTTY) to the boards COM port, so that when the module restarts after programming, it's messages can be captured.

Programming Variant "IDE"

The Microsemi Hardware and Software Design Tools, Libero and SoftConsole, incorporate the abillity to edit, debug and program Hardware and Software Designs. This Programming Variant is for you, when you are interessted in this.

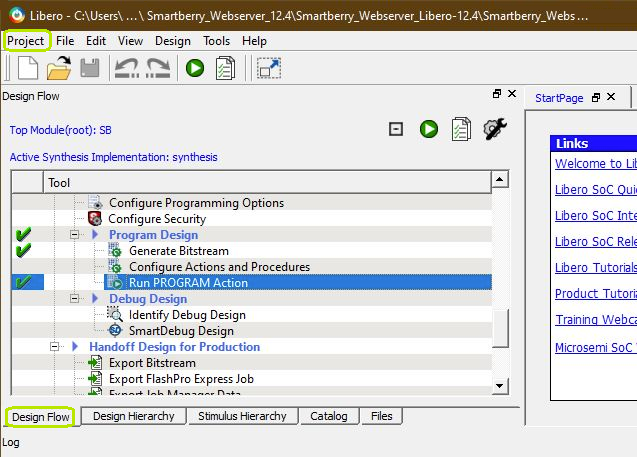

Programming the Hardware design

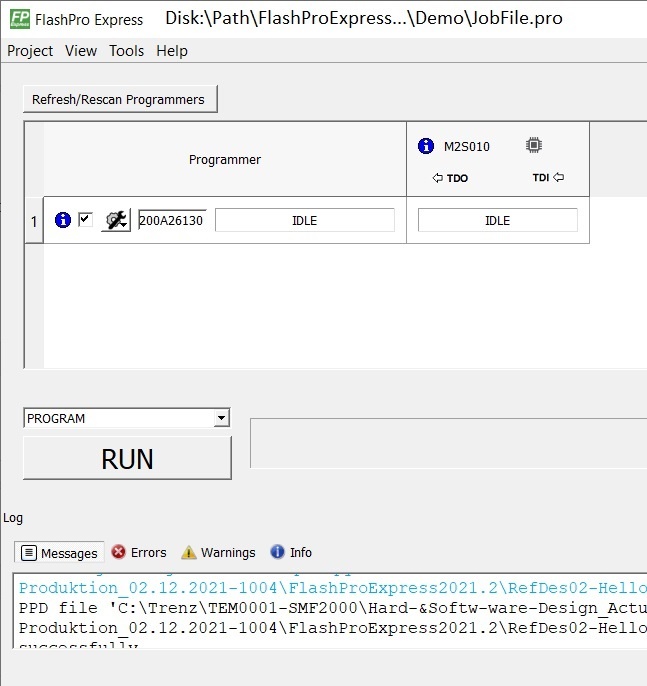

To program the Hardware Reference Design, start FPGA Design "Libero SoC v2021.2".

| Scroll Title |

|---|

| anchor | Figure_1 |

|---|

| title | Libero GUI "Run PRGORAMM ACTION" |

|---|

|

|

The Hardware Reference Design can be opened via "Project > Open Project" in the top right corner of Libero (picture above - upper green rectangle). A file dialogue opens, point the dialogue along the extracted download to the folder containing the Hardware Reference Design.

Disk :\ Path-to-the-Demo-archive \ Extracted ZIP-archive \ Libero-X.y_Referenz-Design\

Double left mouse click onto the project file "Referenz-Design_XY .prjx" to open it. The board is automatically selected and setup to be flashed by Libero.

In the upper left section of Libero, select the tab "Design Flow" (picture above - lover green rectangle) and flash it to the board via "Program Design > and double left mouse click onto "Run PROGRAM Action" (picture above - row with blue background).

Warnings should not affect the functionality of a Reference / Demo -Design.

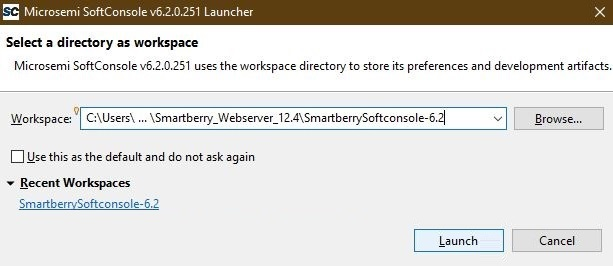

Programming a Software project

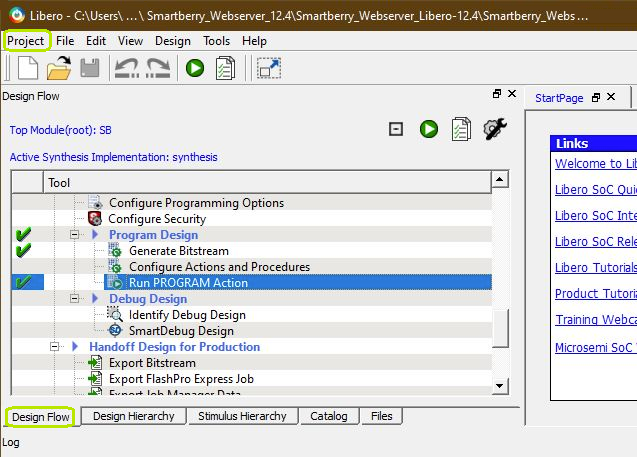

Open SoftConsole and press "Browse..." near the right edge. A file dialogue opens, point the dialogue along the extracted download to the folder containing the SoftConsole Workspace.

Disk :\ Path-to-the-Demo-archive \ Extracted ZIP-archive \ Softconsole-X.y-Workspace \

Confirm your selectioin by pressing "Ok" , the dialogue closes, and open The SoftConsole by pressing "Launch"

| Scroll Title |

|---|

| anchor | Figure_2 |

|---|

| title | SoftConsole "Select the Workspace" |

|---|

|

|

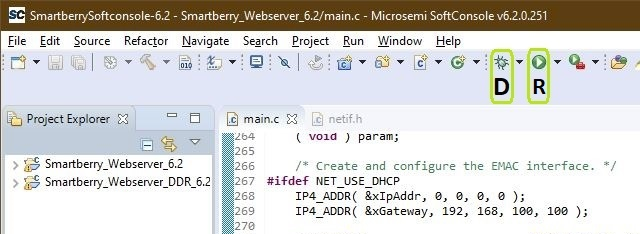

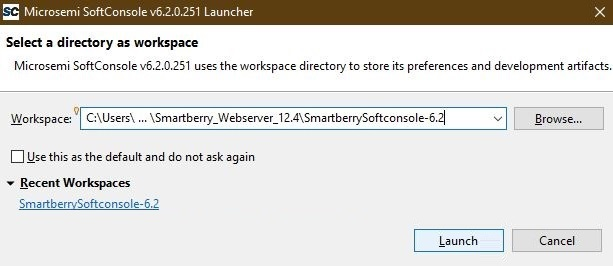

Subsequently the program opens and shows the software project's who are contained inside the workspace to the left, under "Project Explorer".

| Scroll Title |

|---|

| anchor | Figure_3 |

|---|

| title | SoftConsole GUI |

|---|

|

|

To simply run a Project, press the triangle right to the button marked with a "R" in the picture above and select a variant of the demo.

Pressing the triangle next to the button marked with "D" let you select which variant to be executed in debug mode.

Debug controls - Resume - Pause - Stop

| Scroll Title |

|---|

| anchor | Figure_4 |

|---|

| title | SoftConsole "Debug controlls" |

|---|

|

|

Switch between Debug and Run perspective (upper right corner program window)

| Scroll Title |

|---|

| anchor | Figure_5 |

|---|

| title | SoftConsole "Switch GUI layout" |

|---|

|

|

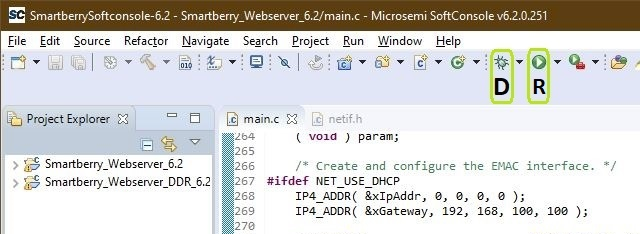

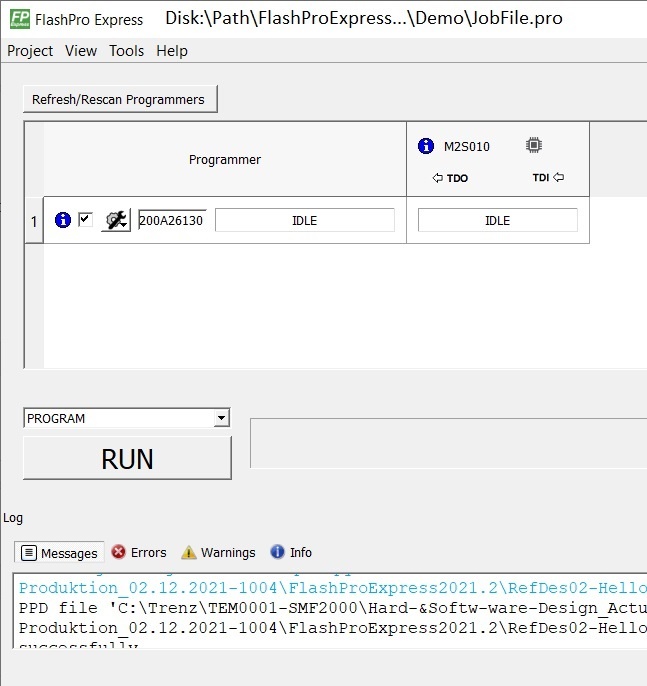

Programming Variant "FlashPro Express"

When you just want to run a SoC Design, this is for you.

To program a Hardware and Software Design simultaneously, open FlashPro Express. Via left click onto Open .... in the section "Job Projects" open a file dialogue. Point to

Disk :\ Path-to-the-Demo-archive \ Extracted ZIP-archive \ FlashProExpressX.y \ Desired Demo \ JobFile . pro

| Scroll Title |

|---|

| anchor | Figure_6 |

|---|

| title | FlashPro Express GUI |

|---|

|

|

To program the Design, press Run.

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

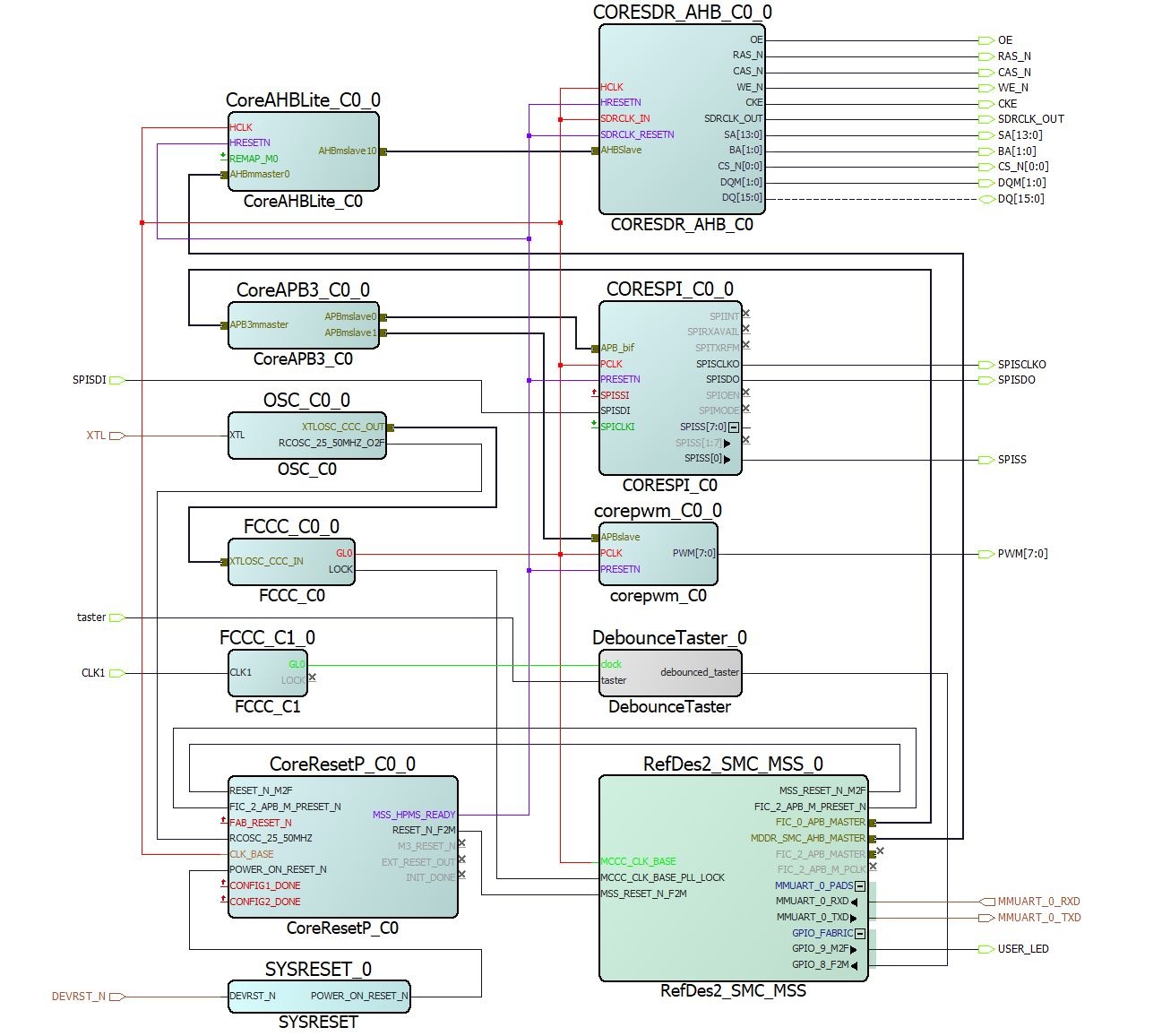

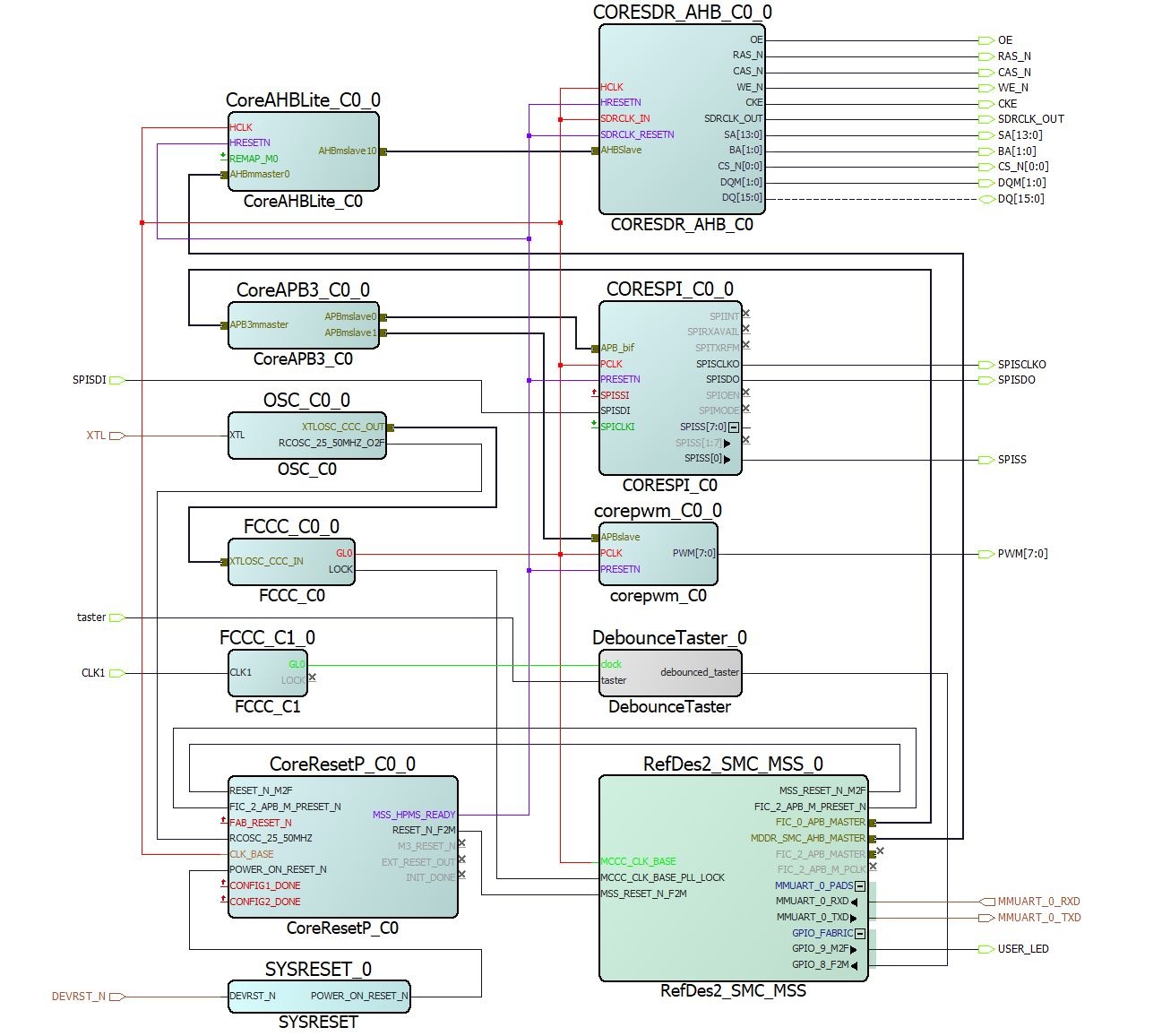

Hardware Reference Design - Libero

Smart Design

| Scroll Title |

|---|

| title-position | top |

|---|

| anchor | Figure_BD |

|---|

| title | Block Design |

|---|

|

|

Constrains

IO constrains

| Code Block |

|---|

| language | ruby |

|---|

| title | SoC_Dedicated.pdc |

|---|

| linenumbers | true |

|---|

| collapse | true |

|---|

|

# Microsemi I/O Physical Design Constraints file

# User I/O Constraints file

# Version: v2021.1 2021.1.0.17

# Family: SmartFusion2 , Die: M2S010 , Package: 400 VF

# Date generated: Fri Aug 13 07:56:00 2021

#

# User Locked I/O Bank Settings

#

#

# Unlocked I/O Bank Settings

# The I/O Bank Settings can be locked by directly editing this file

# or by making changes in the I/O Attribute Editor

#

#

# User Locked I/O settings

#

#

# Dedicated Peripheral I/O Settings

#

set_io CLK1 \

-pinname N16 \

-fixed yes \

-DIRECTION INPUT

#

# Unlocked I/O settings

# The I/Os in this section are unplaced or placed but are not locked

# the other listed attributes have been applied

#

#

#Ports using Dedicated Pins

#

set_io DEVRST_N \

-pinname U17 \

-DIRECTION INPUT

set_io XTL \

-pinname Y18 \

-DIRECTION INPUT

|

| Code Block |

|---|

| language | ruby |

|---|

| title | SDRAM.pdc |

|---|

| linenumbers | true |

|---|

| collapse | true |

|---|

|

# Microsemi I/O Physical Design Constraints file

# User I/O Constraints file

# Version: v11.8 11.8.0.26

# Family: SmartFusion2 , Die: M2S010 , Package: 400 VF

# Date generated: Fri Oct 20 14:01:01 2017

#

# User Locked I/O Bank Settings

#

#

# Unlocked I/O Bank Settings

# The I/O Bank Settings can be locked by directly editing this file

# or by making changes in the I/O Attribute Editor

#

#

# User Locked I/O settings

#

set_io {BA[0]} \

-pinname W10 \

-fixed yes \

-DIRECTION OUTPUT

set_io {BA[1]} \

-pinname V12 \

-fixed yes \

-DIRECTION OUTPUT

set_io CAS_N \

-pinname Y12 \

-fixed yes \

-DIRECTION OUTPUT

set_io CKE \

-pinname Y13 \

-fixed yes \

-DIRECTION OUTPUT

set_io {CS_N[0]} \

-pinname R13 \

-fixed yes \

-DIRECTION OUTPUT

set_io {DQ[0]} \

-pinname F1 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[1]} \

-pinname G1 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[2]} \

-pinname E2 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[3]} \

-pinname G2 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[4]} \

-pinname E3 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[5]} \

-pinname G3 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[6]} \

-pinname F3 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[7]} \

-pinname F4 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[8]} \

-pinname J7 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[9]} \

-pinname G6 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[10]} \

-pinname F6 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[11]} \

-pinname H5 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[12]} \

-pinname H6 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[13]} \

-pinname H4 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[14]} \

-pinname F5 \

-fixed yes \

-DIRECTION INOUT

set_io {DQ[15]} \

-pinname G4 \

-fixed yes \

-DIRECTION INOUT

set_io {DQM[0]} \

-pinname E5 \

-fixed yes \

-DIRECTION OUTPUT

set_io {DQM[1]} \

-pinname F7 \

-fixed yes \

-DIRECTION OUTPUT

set_io RAS_N \

-pinname U13 \

-fixed yes \

-DIRECTION OUTPUT

set_io {SA[0]} \

-pinname U11 \

-fixed yes \

-DIRECTION OUTPUT

set_io {SA[1]} \

-pinname U12 \

-fixed yes \

-DIRECTION OUTPUT

set_io {SA[2]} \

-pinname V11 \

-fixed yes \

-DIRECTION OUTPUT

set_io {SA[3]} \

-pinname Y10 \

-fixed yes \

-DIRECTION OUTPUT

set_io {SA[4]} \

-pinname W15 \

-fixed yes \

-DIRECTION OUTPUT

set_io {SA[5]} \

-pinname U14 \

-fixed yes \

-DIRECTION OUTPUT

set_io {SA[6]} \

-pinname Y15 \

-fixed yes \

-DIRECTION OUTPUT

set_io {SA[7]} \

-pinname W14 \

-fixed yes \

-DIRECTION OUTPUT

set_io {SA[8]} \

-pinname T15 \

-fixed yes \

-DIRECTION OUTPUT

set_io {SA[9]} \

-pinname W13 \

-fixed yes \

-DIRECTION OUTPUT

set_io {SA[10]} \

-pinname T13 \

-fixed yes \

-DIRECTION OUTPUT

set_io {SA[11]} \

-pinname V14 \

-fixed yes \

-DIRECTION OUTPUT

set_io {SA[12]} \

-pinname V15 \

-fixed yes \

-DIRECTION OUTPUT

set_io {SA[13]} \

-pinname Y16 \

-fixed yes \

-DIRECTION OUTPUT

set_io WE_N \

-pinname R12 \

-fixed yes \

-DIRECTION OUTPUT

set_io SDRCLK_OUT \

-pinname T14 \

-fixed yes \

-DIRECTION OUTPUT

|

| Code Block |

|---|

| language | ruby |

|---|

| title | SPI.pdc |

|---|

| linenumbers | true |

|---|

| collapse | true |

|---|

|

# Microsemi I/O Physical Design Constraints file

# User I/O Constraints file

# Version: v2021.1 2021.1.0.17

# Family: SmartFusion2 , Die: M2S010 , Package: 400 VF

# Date generated: Sat Jul 24 11:29:36 2021

#

# User Locked I/O Bank Settings

#

#

# Unlocked I/O Bank Settings

# The I/O Bank Settings can be locked by directly editing this file

# or by making changes in the I/O Attribute Editor

#

#

# User Locked I/O settings

#

set_io SPISCLKO \

-pinname P18 \

-fixed yes \

-DIRECTION OUTPUT

set_io SPISDI \

-pinname K16 \

-fixed yes \

-DIRECTION INPUT

set_io SPISDO \

-pinname P19 \

-fixed yes \

-DIRECTION OUTPUT

set_io SPISS \

-pinname K15 \

-fixed yes \

-DIRECTION OUTPUT

|

| Code Block |

|---|

| language | ruby |

|---|

| title | LEDs_Button.pdc |

|---|

| linenumbers | true |

|---|

| collapse | true |

|---|

|

# SMF2000 Board Pinout, 2018-11-27

# LED1-LED8

set_io {PWM[0]} -pinname E18 -fixed yes -iostd LVCMOS33 -OUT_DRIVE 16

set_io {PWM[1]} -pinname R17 -fixed yes -iostd LVCMOS33 -OUT_DRIVE 16

set_io {PWM[2]} -pinname R18 -fixed yes -iostd LVCMOS33 -OUT_DRIVE 16

set_io {PWM[3]} -pinname T18 -fixed yes -iostd LVCMOS33 -OUT_DRIVE 16

set_io {PWM[4]} -pinname U18 -fixed yes -iostd LVCMOS33 -OUT_DRIVE 16

set_io {PWM[5]} -pinname R16 -fixed yes -iostd LVCMOS33 -OUT_DRIVE 16

set_io {PWM[6]} -pinname E1 -fixed yes -iostd LVCMOS33 -OUT_DRIVE 16

set_io {PWM[7]} -pinname D2 -fixed yes -iostd LVCMOS33 -OUT_DRIVE 16

#USER_LED

set_io {USER_LED} -pinname G17 -fixed yes -iostd LVCMOS33 -DIRECTION OUTPUT

# USER_BTN

set_io taster -pinname B19 -fixed yes -iostd LVCMOS33 -RES_PULL Up |

Clock constrains

| Code Block |

|---|

| language | ruby |

|---|

| title | user_clock_constraints.sdc |

|---|

| linenumbers | true |

|---|

| collapse | true |

|---|

|

create_clock -name {FCCC_C0_0__FCCC_C0_0__GL0_net} -period 10 -waveform {0 5 } [ get_nets { FCCC_C0_0/FCCC_C0_0/GL0_net } ]

create_clock -name {FCCC_C1_0__GL0_net} -period 250 -waveform {0 125 } [ get_nets { FCCC_C1_0/FCCC_C1_0/GL0_net } ]

create_clock -name {XTL} -period 83.3333 -waveform {0 41.6667 } [ get_ports { XTL } ]

create_clock -name {OSC_C0_0__OSC_C0_0__RCOSC_25_50MHZ_O2F} -period 20 -waveform {0 10 } [ get_pins { FCCC_C0_0/FCCC_C0_0/CCC_INST/RCOSC_25_50MHZ } ]

create_clock -name {CLK1} -period 83.3333 -waveform {0 41.6667 } [ get_ports { CLK1 } ] |

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

Software Design - SoftConsole

| Page properties |

|---|

|

Note:

---------------------------------------------------------- General Example: hello_te0820Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output. u-bootU-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin. |

Application

| Page properties |

|---|

|

- Describe the Designs

- How to use

- What to expect

|

Demo Hello World

The demo project ... .

| Scroll Title |

|---|

| anchor | Figure_6 |

|---|

| title | COM-port Terminal Webserver "Welcome / IP -message" |

|---|

|

|

Sub chapter

| Scroll Title |

|---|

| anchor | Figure_7 |

|---|

| title | SoftConsole "main.c - Set IP" |

|---|

|

|

Text ... .

Reference Design - ...

Text ...

| Scroll Title |

|---|

| anchor | Figure_9 |

|---|

| title | COM-port Terminal "Hello World loop" |

|---|

|

|

Demo SF2_GNU_SC4_pwm_slow_blink

The demo project ... .

| Scroll Title |

|---|

| anchor | Figure_6 |

|---|

| title | COM-port Terminal Webserver "Welcome / IP -message" |

|---|

|

|

Sub chapter

| Scroll Title |

|---|

| anchor | Figure_7 |

|---|

| title | SoftConsole "main.c - Set IP" |

|---|

|

|

Text ... .

| Scroll Title |

|---|

| anchor | Figure_9 |

|---|

| title | COM-port Terminal "Hello World loop" |

|---|

|

|

Demo SF2_GNU_SC4_rtc_time

The demo project ... .

| Scroll Title |

|---|

| anchor | Figure_6 |

|---|

| title | COM-port Terminal Webserver "Welcome / IP -message" |

|---|

|

|

Sub chapter

| Scroll Title |

|---|

| anchor | Figure_7 |

|---|

| title | SoftConsole "main.c - Set IP" |

|---|

|

|

Text ... .

| Scroll Ignore |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

Appx. A: Change History and Legal Notices

Document Change History

To get content of older revision got to "Change History" of this page and select older document revision number.

| Page properties |

|---|

|

- Note this list must be only updated, if the document is online on public doc!

- It's semi automatically, so do following

Add new row below first Copy "Page Information Macro(date)" Macro-Preview, Metadata Version number, Author Name and description to the empty row. Important Revision number must be the same as the Wiki document revision number Update Metadata = "Page Information Macro (current-version)" Preview+1 and add Author and change description. --> this point is will be deleted on newer pdf export template - Metadata is only used of compatibility of older exports

|

| Scroll Title |

|---|

| anchor | Table_dch |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | 2*,*,3*,4* |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Document Revision | Authors | Description |

|---|

| Page info |

|---|

| infoType | Modified date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| type | Flat |

|---|

|

| | | -- | all | | Page info |

|---|

| infoType | Modified users |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| -- |

|

Legal Notices

| Include Page |

|---|

| IN:Legal Notices |

|---|

| IN:Legal Notices |

|---|

|