Page History

Template Revision 2.8 - on construction

...

| HTML |

|---|

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

...

| hidden | true |

|---|---|

| id | Comments |

Important General Note:

...

Export PDF to download, if vivado revision is changed!

Designate all graphics and pictures with a number and a description, Use "Scroll Title" macro

...

...

Figure template (note: inner scroll ignore/only only with drawIO object):

...

| anchor | Figure_xyz |

|---|---|

| title | Text |

| Scroll Ignore |

|---|

Create DrawIO object here: Attention if you copy from other page, use |

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

...

Table template:

- Layout macro can be use for landscape of large tables

- Set column width manually(can be used for small tables to fit over whole page) or leave empty (automatically)

...

| anchor | Table_xyz |

|---|---|

| title | Text |

...

| Scroll pdf ignore | ||||

|---|---|---|---|---|

Table of contents

|

Overview

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Zynq PS Design with DDR Less FSBL Example.

Refer to http://trenz.org/te0722-info for the current online version of this manual and other available documentation.

Key Features

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Excerpt |

|---|

|

...

...

...

...

...

...

...

...

...

...

...

- 2019.2 update

...

- split FSBL into 2 templates, one with and one without Sensor+LED access example app

...

- TE Script update

- rework of the FSBLs

- DDR LESS, Device ID, Sensor+LED access

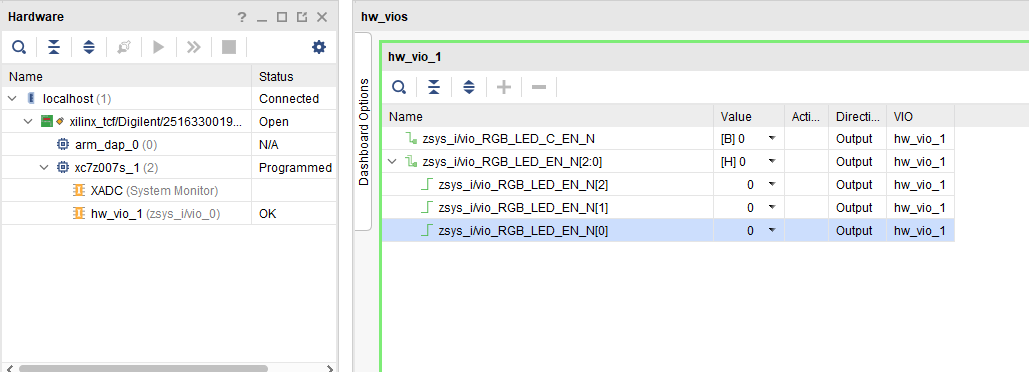

- VIO for RGB access

...

- initial release

...

...

...

...

...

...

...

- Option1:

- In case Flash is empty, use fsbl_flash on programming GUI

- In case Flash is programmed use normal fsbl on programming GUI

- Option2: use in both case fsbl_flash on programming GUI and Vivado LabTools 2018.3

Requirements

Software

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| anchor | Table_SW |

|---|---|

| title | Software |

...

- list of software which was used to generate the design

Basic description of TE Board Part Files is available on TE Board Part Files.

Complete List is available on <design name>/board_files/*_board_files.csv

...

...

...

...

...

...

Design supports following carriers:

...

...

...

...

Additional HW Requirements:

...

| anchor | Table_AHW |

|---|---|

| title | Additional Hardware |

...

for JTAG, UART

...

Content

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

For general structure and of the reference design, see Project Delivery - Xilinx devices

...

...

...

...

Additional Sources

...

...

...

Prebuilt

...

| hidden | true |

|---|---|

| id | Comments |

Notes :

...

...

...

...

...

...

...

...

...

...

...

...

Debian SD-Image

...

*.img

...

Debian Image for SD-Card

...

...

MCS-File

...

...

...

...

File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only)

...

...

...

SREC-File

...

*.srec

...

Converted Software Application for MicroBlaze Processor Systems

...

| anchor | Table_PF |

|---|---|

| title | Prebuilt files (only on ZIP with prebult content) |

...

File

...

File-Extension

...

Description

...

Download

Reference Design is only usable with the specified Vivado/SDK/PetaLinux/SDx version. Do never use different Versions of Xilinx Software for the same Project.

...

| hidden | true |

|---|---|

| id | Comments |

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

Block Design

...

| anchor | Figure_BD |

|---|---|

| title | Block Design |

...

...

...

...

...

...

...

...

Source location: \sw_lib\sw_apps

...

...

Add Files: te_fsbl_hooks.h/.c(for hooks and board)\n\

...

- Display FSBL Banner and Device ID

- Disable Memory initialisation on main.c

zynq_fsbl_app

TE modified 2019.2 FSBL

General:

- Modified Files:main.c, fsbl_hooks.h/.c (search for 'TE Mod' on source code)

Add Files: te_fsbl_hooks.h/.c(for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device ID

- Disable Memory initialisation on main.c

Module Specific:

- Add Files: all TE Files start with te_*

- Example app for LED access over MIO and sensor access over I2C

zynq_fsbl_flash

TE modified 2019.2 FSBL

General:

...

...

...