Page History

...

- Xilinx Zynq UltraScale+ MPSoC 784-pin package (ZU3EG, option for ZU5EV)

- Dual Cortex-A53 64-bit ARM v8 application processing unit (APU)

- Dual Cortex-R5 32-bit ARM v7 real-time processing unit (RPU)

Four high-speed serial I/O (HSSIO) interfaces supporting following protocols:

- PCI Express® interface version 2.1 compliant

- SATA 3.1 specification compliant interface

DisplayPort source-only interface with video resolution up to 4k x 2k

- USB 3.0 specification compliant interface implementing a 5 Gbit/s line rate

- 1 GB/s serial GMII interface

- 132 x HP PL I/Os (3 banks)

- 14 x PS MIOs (6 of the MIOs intended for SD card interface in default configuration)

- 4 x serial PS GTR transceivers

- 32-Bit DDR4, 4 GByte maximum

- Dual parallel SPI boot Flash, 512 MByte maximum

- 4 GByte eMMC (up to 64 GByte)

- GT reference clock input

- PLL for GT clocks (optional external reference)

- Gigabit Ethernet transceiver PHY (Marvell Alaska 88E1512)

- MAC address serial EEPROM with EUI-48™ node identity (Microchip 24AA025E48)

- Hi-speed USB 2.0 ULPI transceiver with full OTG support (Microchip USB3320C)

- Programmable quad clock generator

- Plug-on module with 2 x 100-pin and 1 x 60-pin high-speed hermaphroditic strips

- All power supplies on board

- Size: 50 x 40 mm

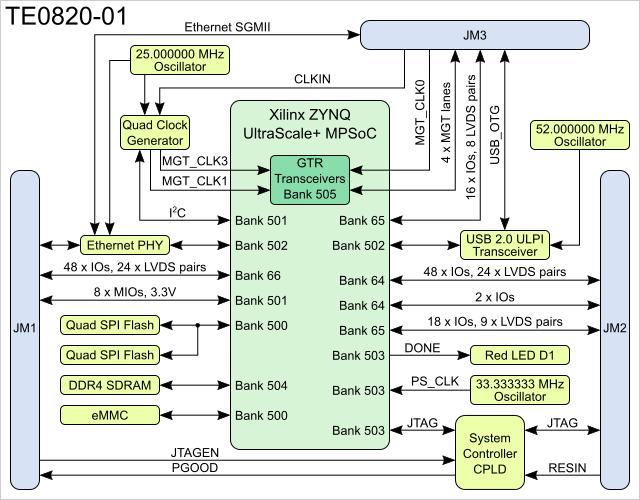

Block Diagram

Figure 1: TE020-02 block diagram.

...

Date | Revision | Contributors | Description | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Jan Kumann | HW revision 02 block diagram added. Power Power distribution diagram added. TRM update to the template revision 1.6 Weight section removed. Few minor corrections. | |||||||||

2017-08-18 | V.7 | John Hartfiel |

| ||||||||

2017-08-07 | V.5 | Jan Kumann | Initial version. | ||||||||

All | Jan Kumann, John Hartfiel |

...

Overview

Content Tools