Page History

| HTML |

|---|

<!-- Template Revision 1.0 Basic Notes - export PDF to download, if vivado revision is changed! - Template is for different design and SDSoC and examples, remove unused or wrong description! --> |

...

| HTML |

|---|

<!-- General Design description --> |

Key Features

| HTML |

|---|

<!--

Add Basic Key Features of the design (should be tested)

--> |

- PetaLinux

- SD

- ETH

- USB

- U2C

- RTC

Revision History

| HTML |

|---|

<!--

- Add changes from design

- Export PDF to download, if vivado revision is changed!

--> |

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2017-09-22 | 2017.2 | te0715-test_board-vivado_2017.2-build_02_20170922131837.zip te0715-test_board_noprebuilt-vivado_2017.2-build_02_20170922131853.zip | John Hartfiel | initial release |

Release Notes and Know Issues

| HTML |

|---|

<!--

- add known Design issues and general Notes for the current revision

--> |

| Issues | Description | Workaround | To be fixed version |

|---|---|---|---|

| No known issues | --- | --- | --- |

Requirements

Software

| HTML |

|---|

<!-- RemovedAdd unusedneeded SW or ADD SW ...external Software --> |

| Software | Software | Version | Note |

|---|---|---|---|

| Vivado | 2017.2 | needed | |

| SDK | 2017.2 | needed | |

| PetaLinux | 2017.2 | needed |

Hardware

| HTML |

|---|

<!--

Hardware Support

--> |

Basic description of TE Board Part Files is available on TE Board Part Files.

...

| Additional Hardware | Notes |

|---|---|

| USB Cable for JTAG/UART | Check Carrier Board and Programmer for correct typ |

| XMOD Programmer | Carrier Board dependent, only if carrier has no own FTDI |

...

- Prepare HW like described on section programming

- Connect UART USB (most cases same as JTAG)

- Power On PCB

Linux

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Linux Console:

- User Name: root

- Password: root

Vivado HW Manager

MGT Reference CLK Counter:

- Open Vivado HW-Manager and add VIO signal to dashboard (*.ltx located on prebuilt folder).

- Set radix from VIO signals to unsigned integer.

MGT CLK is configured to 125MHz by default, FCLK is not configured by default.

...

| HTML |

|---|

<!--

TODO Add Picture

--> |

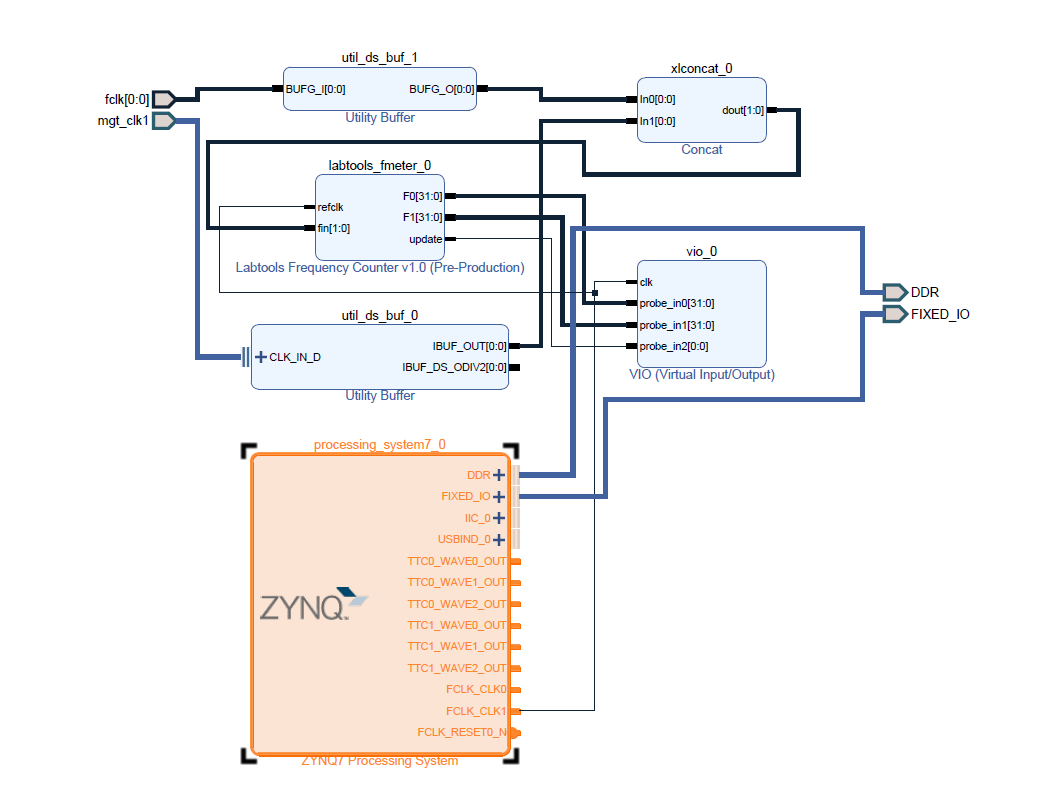

System Design - Vivado

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

...

Description currently not available.

Block Design

Constrains

Basic module constrains

Block Design

...

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property CFGBVS VCCO [current_design]

set_property BITSTREAM.CONFIG.USR_ACCESS TIMESTAMP [current_design] |

| Code Block | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLNONE [current_design] |

Design specific constrain

| Code Block | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

set_property PACKAGE_PIN K2 [get_ports {fclk[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {fclk[0]}]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets fclk_IBUF[0]] |

Software Design - SDK/HSI

| HTML |

|---|

<!-- optional chapter separate sections for different apps --> |

For SDK project creation, follow instructions from:

Description currently not available.

Application

FSBL

Xilinx default FSBL

U-Boot

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin.

Software Design - PetaLinux

| HTML |

|---|

<!-- - optional chapter , if petalinux is used - Add changes from default petalinux project --> |

For PetaLinux installation and project creation, follow instructions from:

Description currently not available.

Config

No changes.

U-Boot

No changes.

Device Tree

| Code Block | ||

|---|---|---|

| ||

/include/ "system-conf.dtsi"

/ {

};

/* default */

/* ETH PHY */

&gem0 {

status = "okay";

ethernet_phy0: ethernet-phy@0 {

compatible = "marvell,88e1510";

device_type = "ethernet-phy";

reg = <0>;

};

};

/* USB PHY */

/{

usb_phy0: usb_phy@0 {

compatible = "ulpi-phy";

//compatible = "usb-nop-xceiv";

#phy-cells = <0>;

reg = <0xe0002000 0x1000>;

view-port = <0x0170>;

drv-vbus;

};

};

&usb0 {

dr_mode = "host";

//dr_mode = "peripheral";

usb-phy = <&usb_phy0>;

};

/* I2C */

// i2c PLL: 0x70, i2c eeprom: 0x50

&i2c1 {

rtc@6F { // Real Time Clock

compatible = "isl12022";

reg = <0x6F>;

};

};

|

...

- RTC_DRV_ISL12022

Rootfs

No changes.

Applications

No additional applications.

Additional Software

| HTML |

|---|

<!--

Add Description for other Software, for example SI CLK Builder ...

--> |

No additional software is needed.

Appx. A: Change History and Legal Notices

...

Overview

Content Tools