Page History

...

| HTML |

|---|

<!-- Add Basic Key Features of the design (should be tested) --> |

- PetaLinux

- SD

- 2x ETHUSB

- I2C

- RTCFMeter

Revision History

| HTML |

|---|

<!-- - Add changes from design - Export PDF to download, if vivado revision is changed! --> |

...

| Issues | Description | Workaround | To be fixed version |

|---|---|---|---|

| UBoot ETH PHY Address | PHY Address is not set correctly for UBootNo known issues | --- | ------ |

Linux Message: "macb ... .ethernet eth...: unable to generate target frequency: 25000000 Hz" | This can be ignored, ETH works. |

Requirements

Software

| HTML |

|---|

<!-- Add needed external Software --> |

| Software | Version | Note |

|---|---|---|

| Vivado | 2017.12 | needed |

| SDK | 2017.12 | needed |

| PetaLinux | 2017.12 | neededSDx |

Hardware

...

| HTML |

|---|

<!-- |

Hardware

| HTML |

|---|

<!--

Hardware Support

--> |

Basic description of TE Board Part Files is available on TE Board Part Files.

...

| Module Model | Board Part Short Name | Notes |

|---|---|---|

| TE0728-03-1Q | 03_1q | Supports PCB REV01,02,03 |

| TE0728-04-1Q | 04_1q |

Design supports following carriers:

| Carrier Model | Notes |

|---|---|

| ---TEB0728 |

Additional HW Requirements:

| Additional Hardware | Notes |

|---|---|

| USB Cable for JTAG/UART | |

| XMOD Programmer |

Content

| HTML |

|---|

<!-- Remove unused content --> |

...

| Type | Location | Notes | |

|---|---|---|---|

| Vivado | <design name>/block_design <design name>/constraints <design name>/ip_lib | Vivado Project will be generated by TE Scripts | |

| SDK/HSI | <design name>/sw_lib | Additional Software Template for SDK/HSI and apps_list.csv with settings for HSI | |

| PetaLinux | <design name>/os/petalinux | PetaLinux template with current configuration | SDSoC

Additional Sources

| Type | Location | Notes | ||

|---|---|---|---|---|

| init.sh | <design name>/ | ..misc/ | SDSoCinit_ | PFMSDSoC Platform will be generated by TE Scripts or as separate download |

Additional Sources

| script | Additional | |

| Type | Location | Notes |

|---|---|---|

| SI5345 | <design name>/misc/Si5338 | SI5345 Project with current PLL Configuration |

| init.sh | <design name>/misc/init_script | Additional Initialization Script for Linux |

...

File | File-Extension | Description | |||

|---|---|---|---|---|---|

| BIF-File | *.bif | File with description to generate Bin-File | |||

| BIN-File | *.bin | Flash Configuration File with Boot-Image (Zynq-FPGAs) | |||

| BIT-File | *.bit | FPGA (PL Part) Configuration File | |||

| Diverse Reports | --- | Report files in different formats | |||

| Hardware-Platform-Specification-FilesDebugProbes-File | *.ltxhdf | Definition File for Vivado/Vivado Labtools Debugging Interface | |||

Debian SD-Image | *.img | Debian Image for SD-Card | |||

| Diverse Reports | --- | Report files in different formats | |||

| Hardware-Platform-Specification-Files | *.hdf | Exported Vivado Hardware Specification for Exported Vivado Hardware Specification for SDK/HSI and PetaLinux | |||

| LabTools Project-File | *.lpr | Vivado Labtools Project File | |||

MCS-File | *.mcs | Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only) | |||

MMI-File | *.mmi | File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only) | |||

| OS-Image | *.ub | Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) | |||

| Software-Application-File | *.elf | Software Application for Zynq or MicroBlaze Processor Systems | SREC-File | *.srec | Converted Software Application for MicroBlaze Processor Systems |

Download

Reference Design is only usable with the specified Vivado/SDK/PetaLinux/SDx version. Do never use different Versions of Xilinx Software for the same Project.

...

Reference Design is available on:

Design Flow

| HTML |

|---|

<!-- Basic Design Steps Add/ Remove project specific --> |

| Note |

|---|

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first lunchfor first lunch. MIO Bank 501 Power is Carrier depends and set to 3.3V. Please check Settings, if you use a own carrier. |

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

...

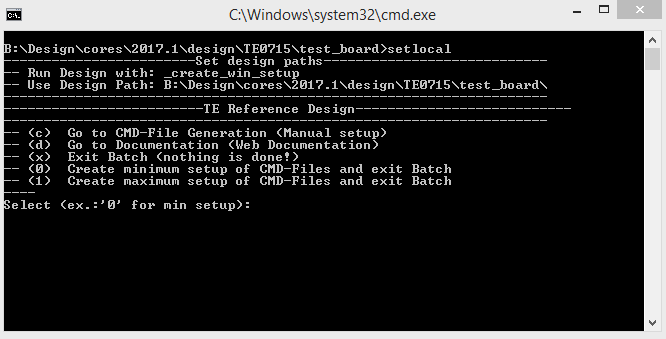

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter for minimum setup

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Create Linux (uboot.elf and image.ub) with exported HDF

- HDF is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

Note: run init_config.sh before you start petalinux config. This will set correct temporary path variable.

- Use TE Template from /os/petalinux

- HDF is exported to "prebuilt\hardware\<short name>"

- Add Linux files (uboot.elf and image.ub) to prebuilt folder

- "prebuilt\os\petalinux\default" or "prebuilt\os\petalinux\<short name>"

Notes: Scripts select "prebuilt\os\petalinux\<short name>", if exist, otherwise "prebuilt\os\petalinux\default"

- "prebuilt\os\petalinux\default" or "prebuilt\os\petalinux\<short name>"

- Generate Programming Files with HSI/SDK

- Run on Vivado TCL: TE::sw_run_hsi

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk

Note: See SDK Projects

- Run on Vivado TCL: TE::sw_run_hsi

SDSoC (only tested on Win OS)

- Generate Platform Project or use prebuilt from download

- ...

Launch

Programming

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

...

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Linux Console:

Note: Wait until Linux boot finished For Linux Login use:- User Name: root

- Password: root

- You can use Linux shell now.

- I2C 0 Bus type: i2cdetect -y -r 0

- ETH0 works with UDHCPC

- ETH1 must be configured manually

- ifconfig eth1 up

- ifconfig eth1 <ip>

Note for Ping test disable ETH0

- RTC check: dmesg | grep rtc

System Design - Vivado

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

...