Page History

...

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2017.4 | John Hartfiel |

| ||

| 2017-11-10 | 2017.2 | te0715-test_board-vivado_2017.2-build_05_20171110134232.zip te0715-test_board_noprebuilt-vivado_2017.2-build_05_20171110134247.zip | John Hartfiel |

|

| 2017-10-19 | 2017.2 | te0715-test_board-vivado_2017.2-build_04_20171019141808.zip te0715-test_board_noprebuilt-vivado_2017.2-build_04_20171019141825.zip | John Hartfiel |

|

| 2017-09-22 | 2017.2 | te0715-test_board-vivado_2017.2-build_02_20170927143412.zip te0715-test_board_noprebuilt-vivado_2017.2-build_02_20170927143427.zip | John Hartfiel |

|

...

| Type | Location | Notes |

|---|---|---|

| SI5338 Project--- | <design_name>/misc/si5338 | --- |

Prebuilt

| HTML |

|---|

<!-- <table width="100%"> <tr> <th>File </th> <th>File-Extension</th> <th>Description </th> </tr> <tr> <td>BIF-File </td> <td>*.bif </td> <td>File with description to generate Bin-File </td> </tr> <tr> <td>BIN-File </td> <td>*.bin </td> <td>Flash Configuration File with Boot-Image (Zynq-FPGAs) </td> </tr> <tr> <td>BIT-File </td> <td>*.bit </td> <td>FPGA Configuration File </td> </tr> <tr> <td>DebugProbes-File </td> <td>*.ltx </td> <td>Definition File for Vivado/Vivado Labtools Debugging Interface </td> </tr> <tr> <td>Debian SD-Image </td> <td>*.img </td> <td>Debian Image for SD-Card </td> </tr> <tr> <td>Diverse Reports </td> <td> --- </td> <td>Report files in different formats </td> </tr> <tr> <td>Hardware-Platform-Specification-Files</td> <td>*.hdf </td> <td>Exported Vivado Hardware Specification for SDK/HSI </td> </tr> <tr> <td>LabTools Project-File </td> <td>*.lpr </td> <td>Vivado Labtools Project File </td> </tr> <tr> <td>MCS-File </td> <td>*.mcs </td> <td>Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only) </td> </tr> <tr> <td>MMI-File </td> <td>*.mmi </td> <td>File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only) </td> </tr> <tr> <td>OS-Image </td> <td>*.ub </td> <td>Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) </td> </tr> <tr> <td>Software-Application-File </td> <td>*.elf </td> <td>Software Application for Zynq or MicroBlaze Processor Systems </td> </tr> <tr> <td>SREC-File </td> <td>*.srec </td> <td>Converted Software Application for MicroBlaze Processor Systems </td> </tr> </table> --> |

...

Reference Design is available on:

Design Flow

| HTML |

|---|

<!-- Basic Design Steps Add/ Remove project specific --> |

...

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

QSPI

Not used on this Example.

SD

...

Optional for Boot.bin on QSPI Flash and image.ub

...

on SD.

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp u-boot

Note: To program with SDK/Vivado GUI, use special FSBL (zynq_fsbl_flash) on setup

SD

- Copy image.ub and Boot.bin on SD-Card.

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Set Boot Mode to SD-Boot.

- Depends on Carrier, see carrier TRM.

- Insert SD-Card in SD-Slot.

...

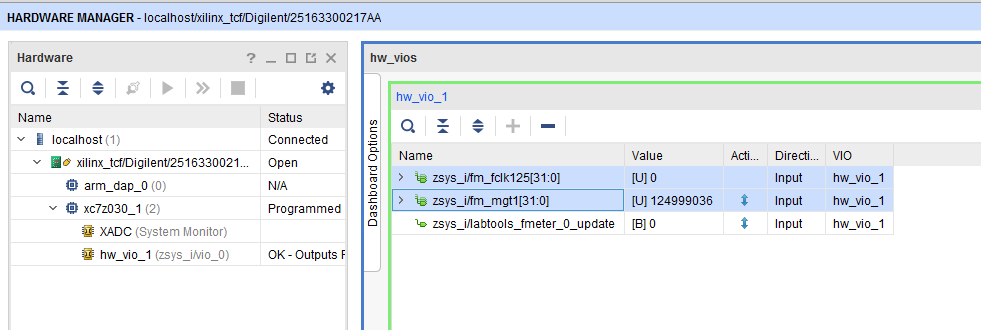

MGT CLK is configured to 125MHz by default, FCLK is not configured by default (optional possible see FSBL description).

System Design - Vivado

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

...

For SDK project creation, follow instructions from:

Application

...

zynq_fsbl

TE modified 2017.2 4 FSBL

Changes:

- Si5338 Configuration see fsbl_hooks.c

add define RECONFIGURE_SI5338 to enable PLL programming with given register_map.h setup - Add register_map.h, si5338.c, si5338.h

zynq_fsbl_flash

TE modified 2017.4 FSBL

Changes:

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

U-Boot

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin.

...

| Date | Document Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

| Release 2017.3 4 - working in process | ||||||||||||||||||||||

| 2017-11-10 | v.22 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-19 | v.21 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-19 | v.20 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-06 | v.18 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-02 | v.14 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-09-28 | v.13 | John Hartfiel | Release 2017.2 | ||||||||||||||||||||||

| 2017-09-11 | v.1 |

| Initial release | ||||||||||||||||||||||

| All |

|

...

Overview

Content Tools