Page History

...

| HTML |

|---|

<!-- Add Basic Key Features of the design (should be tested) --> |

| Excerpt |

|---|

|

Revision History

| HTML |

|---|

<!-- - Add changes from design - Export PDF to download, if vivado revision is changed! --> |

...

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2018-01-18 | 2017.4 | John Hartfiel |

| |

| 2017-11-16 | 2017.2 | TE0803-test_board-vivado_2017.2-build_05_20171116152716.zip TE0803-test_board_noprebuilt-vivado_2017.2-build_05_20171116154619.zip | John Hartfiel |

|

2017-11-14 | 2017.2 | TE0803-test_board-vivado_2017.2-build_05_20171114090712.zip TE0803-test_board_noprebuilt-vivado_2017.2-build_05_20171114090725.zip | John Hartfiel |

|

...

| Software | Version | Note |

|---|---|---|

| Vivado | 2017.24 | needed |

| SDK | 2017.24 | needed |

Hardware

| HTML |

|---|

<!-- Hardware Support --> |

...

| Module Model | Board Part Short Name | PCB Revision Support | DDR | QSPI Flash | Others | Notes | |||

|---|---|---|---|---|---|---|---|---|---|

| TE0803-ES1 | es1es1 | REV01 | 2GB | 64 | |||||

| TE0803-01-02EG-1E | 2eg2eg | REV01 | TE0808-2ES2 | 2es2 | 2GB | 64REV01 | |||

| TE0803-01-02CG-1E / *EA | 2cg | REV01 | 2GB | 64/ different QSPI Flash size | |||||

| TE0803-01-03EG-1E / *EA | 3eg | REV01 | 2GB | 64/ different QSPI Flash size | |||||

| TE0803-01-03CG-1E / *EA | 3cg | REV01 | / different QSPI Flash size |

Note: Design contains also Board Part Files for TE0803+TEBF0808 configuration, this boart part files are not used for this reference design. * Only different Flash size.

Design supports following carriers:

...

| 2GB | 64 | |||||

| TE0803-01-02EG-1EA | 2eg | REV01 | 2GB | 128 | ||

| TE0803-01-02CG-1EA | 2cg | REV01 | 2GB | 128 | ||

| TE0803-01-03EG-1EA | 3eg | REV01 | 2GB | 128 | ||

| TE0803-01-03CG-1EA | 3cg | REV01 | 2GB | 128 |

Note: Design contains also Board Part Files for TE0803+TEBF0808 configuration, this boart part files are not used for this reference design. * Only different Flash size.

Design supports following carriers:

| Carrier Model | Notes |

|---|---|

| Custom PCB | use simple Board Part files, if MIO connected is different to TEBF0808 |

| TEBF0808 | Used as reference carrier. |

| TEBT0808 | Change UART0 to UART1 (MIO68...69) and regenerate design |

Additional HW Requirements:

| Additional Hardware | Notes |

|---|

Content

| HTML |

|---|

<!--

Remove unused content

--> |

For general structure and of the reference design, see Project Delivery

Design Sources

| Type | Location |

|---|

Additional HW Requirements:

...

Content

| HTML |

|---|

<!--

Remove unused content

--> |

For general structure and of the reference design, see Project Delivery

Design Sources

| Type | Location | Notes |

|---|---|---|

| Vivado | <design name>/block_design <design name>/constraints <design name>/ip_lib | Vivado Project will be generated by TE Scripts |

| SDK/HSI | <design name>/sw_lib | Additional Software Template for SDK/HSI and apps_list.csv with settings for HSI |

...

Reference Design is available on:

Design Flow

| HTML |

|---|

<!-- Basic Design Steps Add/ Remove project specific --> |

...

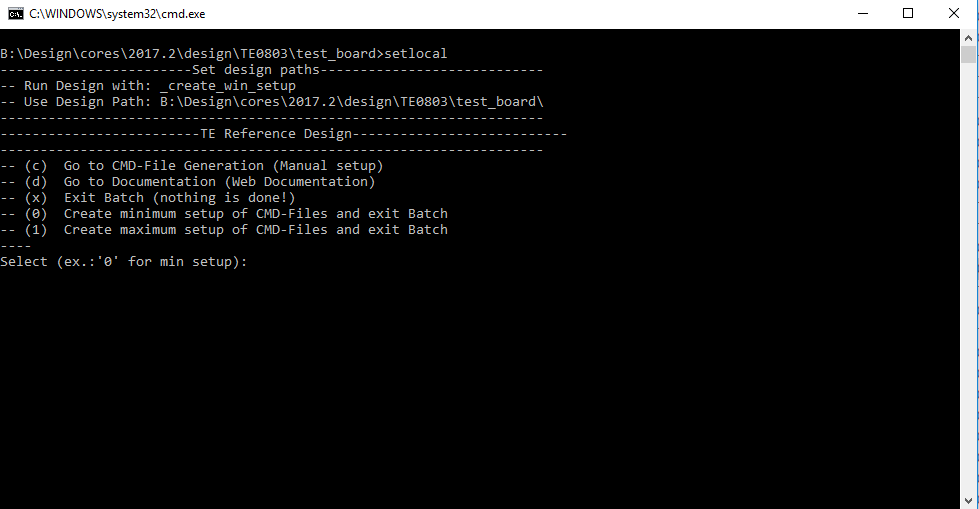

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter for minimum setup

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

Important: Use Board Part Files, which did not contains ends with *_tebf0808

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Generate Programming Files with HSI/SDK

- Run on Vivado TCL: TE::sw_run_hsi

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk

Note: See SDK Projects

- Run on Vivado TCL: TE::sw_run_hsi

...

| HTML |

|---|

<!-- Example: Connect JTAG and power on PCB (if not done) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd" or open with "vivado_open_project_guimode.cmd", if generated. Type on Vivado Console: TE::pr_program_flash_mcsfile -swapp u-boot Note: Alternative use SDK or setup Flash on Vivado manually Reboot (if not done automatically) --> |

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp hello_te0808

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup - Select JTAG as Boot Mode (see Carrier Description and ZynqMP TRM)

- Connect JTAG to Host PC

- Power On

- Open Vivado Hardware Manager with Auto Connect

- Right Click to FPGA Device XCU... and select Add Configuration Memory Device

- Select correct Flash Typ (see schematics or FPGAFLASHTYP on test_board/board_files/TE0808_board_files.csv)

- Open Program Configuration Memory Device

- Configuration file: test_board/prebuilt/boot_image/<short dir>/hello_te0803/Boot.bin

- Zynq FSBL: test_board/prebuilt/software/<short dir>/zynqmp_fsbl.elf Program Device Flash

Use SDK instead of Vivado is also possible, see: SDK Projects#Xilinx%22HelloWorld%22onZynqMP

SD

This does not work, because SD controller is not selected on PS.

JTAG

Load configuration and Application with SDK Debugger into device, see:

...

| Type | Note |

|---|---|

| DDR | |

| QSPI | MIO |

| UART0 | MIO, please select other one, if you have connected uart to second controller or other MIO |

| SWDT0..1 | |

| TTC0..3 |

Constrains

Basic module constrains

...

For SDK project creation, follow instructions from:

Application

...

zynqmp_fsbl

Xilinx default FSBL

zynqmp_fsbl_flash

TE modified 2017.4 FSBL

Changes:

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

Hello TE0803

Hello TE0803 is a Xilinx Hello World example as endless loop instead of one console output.

...

| Date | Document Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||

| 2017-11-16 | v.4 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-11-14 | v.3 | John Hartfiel |

| ||||||||||||||||||||||

| All |

|

...