Page History

...

| Excerpt |

|---|

|

...

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2018-01-31 | 2017.4 | te0803-SK0803_zusys_SDSoC-vivado_2017.1-build_05_20170911131522working in process | John Hartfiel | initial release |

...

| Software | Version | Note |

|---|---|---|

| Vivado | 2017.4 | needed |

| SDK | 2017.4 | needed |

| PetaLinux | 2017.4 | needed |

| SDx | 2017.4 | needed |

| SI5345 Clock Builder | --- | optional |

Hardware

| HTML |

|---|

<!-- Hardware Support --> |

...

Additional HW Requirements:

| Additional Hardware | Notes | ||

|---|---|---|---|

| USB Cable | Connect to USB2 or better USB3 Hub for proper power supply over USB |

Content

| HTML |

|---|

<!-- Remove unused content --> |

...

| Type | Location | Notes |

|---|---|---|

| Vivado | <design name>/block_design <design name>/constraints <design name>/ip_lib | Vivado Project will be generated by TE Scripts |

| SDK/HSI | <design name>/sw_lib | Additional Software Template for SDK/HSI and apps_list.csv with settings for HSI |

| PetaLinux | <design name>/os/petalinux | PetaLinux template with current configuration |

| SDSoC | <design name>/../SDSoC_PFM | SDSoC Platform will be generated by TE Scripts or as separate download |

Additional Sources

Additional Sources

| Type | Location | Notes |

|---|---|---|

| Type | Location | Notes |

| SI5345 | <design name>/misc/Si5338 | SI5345 Project with current PLL Configuration |

| init.sh | <design name>/misc/init_script | Additional Initialization Script for Linux|

Prebuilt

| HTML |

|---|

<!-- <table width="100%"> <tr> <th>File </th> <th>File-Extension</th> <th>Description </th> </tr> <tr> <td>BIF-File </td> <td>*.bif </td> <td>File with description to generate Bin-File </td> </tr> <tr> <td>BIN-File </td> <td>*.bin </td> <td>Flash Configuration File with Boot-Image (Zynq-FPGAs) </td> </tr> <tr> <td>BIT-File </td> <td>*.bit </td> <td>FPGA Configuration File </td> </tr> <tr> <td>DebugProbes-File </td> <td>*.ltx </td> <td>Definition File for Vivado/Vivado Labtools Debugging Interface </td> </tr> <tr> <td>Debian SD-Image </td> <td>*.img </td> <td>Debian Image for SD-Card </td> </tr> <tr> <td>Diverse Reports </td> <td> --- </td> <td>Report files in different formats </td> </tr> <tr> <td>Hardware-Platform-Specification-Files</td> <td>*.hdf </td> <td>Exported Vivado Hardware Specification for SDK/HSI </td> </tr> <tr> <td>LabTools Project-File </td> <td>*.lpr </td> <td>Vivado Labtools Project File </td> </tr> <tr> <td>MCS-File </td> <td>*.mcs </td> <td>Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only) </td> </tr> <tr> <td>MMI-File </td> <td>*.mmi </td> <td>File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only) </td> </tr> <tr> <td>OS-Image </td> <td>*.ub </td> <td>Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) </td> </tr> <tr> <td>Software-Application-File </td> <td>*.elf </td> <td>Software Application for Zynq or MicroBlaze Processor Systems </td> </tr> <tr> <td>SREC-File </td> <td>*.srec </td> <td>Converted Software Application for MicroBlaze Processor Systems </td> </tr> </table> --> |

...

File | File-Extension | Description | ||

|---|---|---|---|---|

| BIF-File | *.bif | File with description to generate Bin-File | ||

| BIN-File | *.bin | Flash Configuration File with Boot-Image (Zynq-FPGAs) | ||

| BIT-File | *.bit | FPGA (PL Part) Configuration File | ||

| Diverse Reports | --- | Report files in different formats | ||

| Hardware-Platform-Specification-FilesDebugProbes-File | *.ltx | Definition File for Vivado/Vivado Labtools Debugging Interface | ||

Debian SD-Image | *.img | Debian Image for SD-Card | ||

| Diverse Reports | --- | Report files in different formats | ||

| hdf | Exported | Hardware-Platform-Specification-Files | *.hdf | Exported Vivado Hardware Specification for SDK/HSI and PetaLinux |

| LabTools Project-File | *.lpr | Vivado Labtools Project File | ||

| MCSOS-FileImage | *.mcsub | Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only) | ||

MMI-File | *.mmi | File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only) | ||

| OS-Image | *.ub | Image with Linux Kernel (On Petalinux optional with Devicetree and RAMImage with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) | ||

| Software-Application-File | *.elf | Software Application for Zynq or MicroBlaze Processor SystemsSREC-File | *.srec | Converted Software Application for MicroBlaze Processor Systems |

Download

Reference Design is only usable with the specified Vivado/SDK/PetaLinux/SDx version. Do never use different Versions of Xilinx Software for the same Project.

...

Reference Design is available on:

Design Flow

| HTML |

|---|

<!-- Basic Design Steps Add/ Remove project specific --> |

...

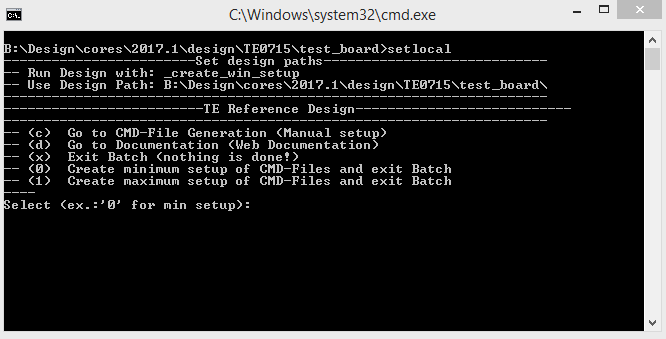

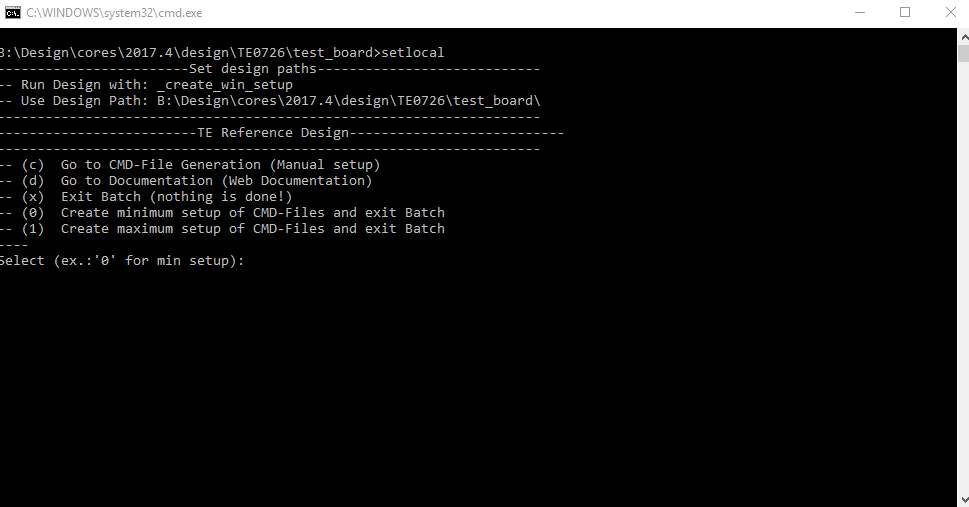

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter for minimum setup

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Create Linux (uboot.elf and image.ub) with exported HDF

- HDF is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

Note: run init_config.sh before you start petalinux config. This will set correct temporary path variable.

- Use TE Template from /os/petalinux

- HDF is exported to "prebuilt\hardware\<short name>"

- Add Linux files (uboot.elf and image.ub) to prebuilt folder

- "prebuilt\os\petalinux\default" or "prebuilt\os\petalinux\<short name>"

Notes: Scripts select "prebuilt\os\petalinux\<short name>", if exist, otherwise "prebuilt\os\petalinux\default"

- "prebuilt\os\petalinux\default" or "prebuilt\os\petalinux\<short name>"

- Generate Programming Files with HSI/SDK

- Run on Vivado TCL: TE::sw_run_hsi

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk

Note: See SDK Projects

- Run on Vivado TCL: TE::sw_run_hsi

SDSoC (only tested on Win OS)

- Generate Platform Project or use prebuilt from download

- ...

Launch

Programming

| HTML |

|---|

<!--

Description of Block Design, Constrains...

BD Pictures from Export...

--> |

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

QSPI

Optional for Boot.bin on QSPI Flash and image.ub on SD.

| Note |

|---|

Since Vivado 2017.4 FSBL is needed to program QSPI. (2017.2 works without FSBL). Xilinx mini-uboot starts with this FSBL configuration but needs QSPI FB CLK enabled on PS. On TE0726, this MIO is used for UART, so special design is need to generate this FSBL. This reference design contains a prebuilt FSBL for QSPI programming (zynqmp_fsbl_flash), so there is normally no need to regenerate this special FSBL. In case of generate this by yourself following steps are needed

|

Launch

Programming

| HTML |

|---|

<!--

Description of Block Design, Constrains...

BD Pictures from Export...

--> |

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

QSPI

- Connect JTAG and power on carrier with Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp u-boot

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup - Copy image.ub on SD-Card

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Insert SD-Card

SD

- Copy image.ub and Boot.bin on SD-Card.

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Set Boot Mode to SD-Boot.

- Depends on Carrier, see carrier TRM.

- Insert SD-Card in SD-Slot.

Xilinx Zynq devices in CLG225 package do not support SD Card boot directly from ROM bootloader. Use QSPI for primary boot and SD for secondary boot (uboot)

JTAGJTAG

Not used on this Example.

...

- Prepare HW like described on section 46043159 Programming

- Connect UART USB (most cases same as JTAG)

- Select Insert SD Card as Boot Mode

Note: See TRM of the Carrier, which is used.with image.ub - Power On PCB

Note: 1. Zynq Boot ROM loads FSBL from SD QSPI into OCM, 2. FSBL loads U-boot from SD QSPI into DDR, 3. U-boot load Linux from SD into DDR

...

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Linux Console:

Note: Wait until Linux boot finished For Linux Login use:- User Name: root

- Password: root

Vivado HW Manager

SI5338_CLK0 Counter:

...

- You can use Linux shell now.

- I2C 1 Bus type: i2cdetect -y -r 1

- RTC check: dmesg | grep rtc

- ETH0 works with udhcpc

- USB: insert USB device

System Design - Vivado

| HTML |

|---|

System Design - Vivado

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

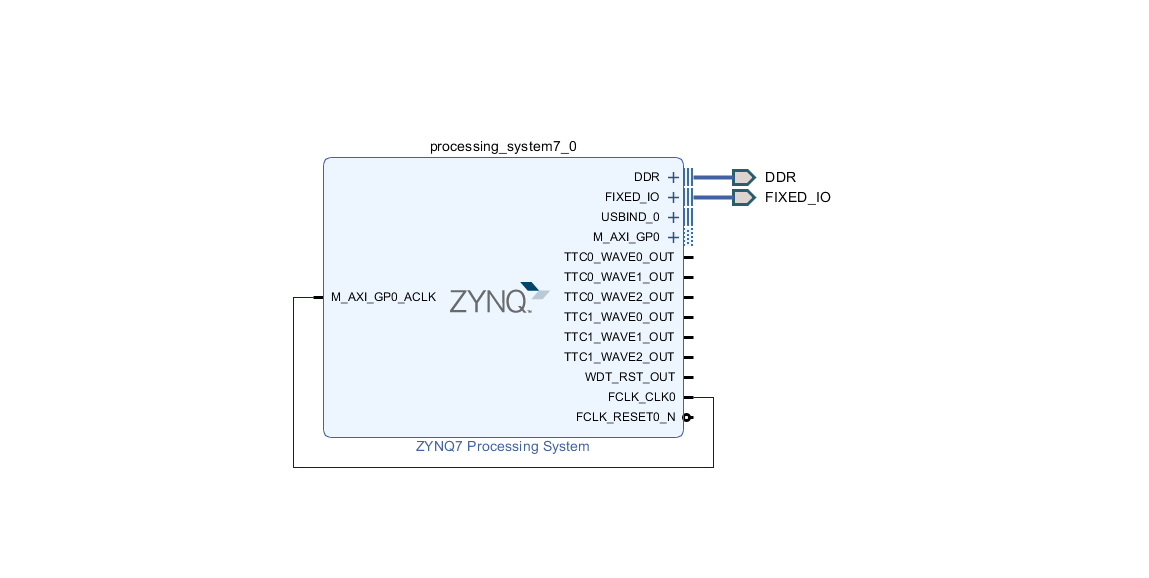

Block Design

PS Interfaces

| Type | Note |

|---|---|

| DDR | --- |

| QSPI | MIO |

| USB0 | MIO, ETH over USB |

| SD1 | MIO |

| UART1 | MIO |

| I2C1 | MIO |

| GPIO | MIO |

| USB RST | MIO |

| TTC0..1 | MIO |

| WDT | MIO |

Constrains

Basic module constrains

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property BITSTREAM.# # Common BITGEN related settings for TE0726 # set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design] set_property CONFIG_VOLTAGE 3.3 [current_design] set_property CFGBVS VCCO [current_design] set_property BITSTREAM.CONFIG.USR_ACCESSUNUSEDPIN TIMESTAMPPULLUP [current_design] |

Design specific constrain

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property PACKAGE_PIN K2 [get_ports {fclk[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {fclk[0]}]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets fclk_IBUF[0]] |

Software Design - SDK/HSI

Software Design - SDK/HSI

| HTML |

|---|

<!--

optional chapter

separate sections for different apps

|

| HTML |

<!--

optional chapter

separate sections for different apps

--> |

For SDK project creation, follow instructions from:

...

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin.

Hello TE0726

Hello World App in endless loop.

Software Design Software Design - PetaLinux

| HTML |

|---|

<!-- optional chapter Add "No changes." or "Activate: and add List" --> |

...

| Code Block | ||

|---|---|---|

| ||

/include/ "system-conf.dtsi"

/ {

};

|

Kernel

No changes.

Rootfs

No changes.

Applications

startup

Script App to load init.sh from SD Card if available.

See: \os\petalinux\project-spec\meta-user\recipes-apps\startup\files

Additional Software

| HTML |

|---|

<!--

Add Description for other Software, for example SI CLK Builder ...

--> |

No additional software is needed.

SI5338

Download ClockBuilder Desktop for SI5338

- Install and start ClockBuilder

- Select SI5338

- Options → Open register map file

Note: File location <design name>/misc/Si5338/RegisterMap.txt - Modify settings

- Options → save C code header files

- Replace Header files from FSBL template with generated file

SDSoC Design

| HTML |

|---|

<!--

optional chapter for SDSoC only

-remove sections, if not supported

--> |

Description currently not available.

SDSoC Platform

SDSoC Demo Examples

SDSoC platform includes 21 demo projects demonstrating optimization techniques for Standalone and Linux targets with HW acceleration or in SW for fast compilation and debug. These projects have been downloaded and installed into the SDSoC platform from https://github.com/Xilinx/SDSoC_Examples

- array_partition

- burst_rw

- custom_data_type

- data_access_random

- dependence_inter

- direct_connect

- dma_sg

- dma_simple

- full_array_2d

- hello_vadd

- lmem_2rw

- loop_fusion

- loop_perfect

- loop_pipeline

- loop_reorder

- row_array_2d

- shift_register

- systolic_array

- sys_port

- wide_memory_rw

- window_array_2d

There are 3 larger Linux demo projects demonstrating video processing with data I/O from file to file. Source code of these projects have been installed into this platform from the Xilinx SDSoC 2016.4 release:

- file_io_manr_sobel

- file_io_optical

- file_io_sbm

These larger Linux demo projects demonstrate video processing with data I/O from file to file. Source code of these projects have been installed into this platform from demos present in the Xilinx SDSoC 2016.4 release.

Compilation steps in the SDSoC 2017.1 is identical to above described examples. File I/O demos support only the Linux target.

These three files use as an input larger video files. These files have to be present on the SD card as an input. Algorithms write output file to the SD card. These files can be visualized by YUV Player Deluxe and other players. To reduce size of the project, the video data files are not included.

Video input files can be found in the Xilinx SDSoC 2016.4 distribution:

- <xilinx install path>\SDx\2016.4\samples\file_io_manr_sobel\input.yuv

- <xilinx install path>\SDx\2016.4\samples\file_io_optical\route85_1920x1080.yuv

- <xilinx install path>\SDx\2016.4\samples\file_io_sbm\desk_1280x720.yuv

Array partition

This example shows how to use array partitioning to improve performance of a hardware function.

Key Concepts:

- Hardware Function Optimization

- Array Partitioning

Keywords:

- #pragma HLS ARRAY_PARTITION

- complete

Burst rw

This is a simple vector increment example which demonstrates usage of AXI4-master interface for burst read and write.

Key Concepts:

- Burst Access

Custom data type

This is a simple example of RGB to HSV conversion to demonstrate Custom Data Type usage in hardware accelerator. Xilinx HLS compiler supports custom data type to operate within the hardware function and also it acts as a memory interface between PL to DDR.

Key Concepts:

- Custom Data Type

Keywords:

- struct

- packed

- aligned

Data access random

This is a simple example of matrix multiplication (Row x Col) to demonstrate random data access pattern.

Key Concepts:

- Data Access Random

Keywords:

- #pragma HLS PIPELINE

- #pragma SDS access_pattern(a:RANDOM, b:RANDOM)

- #pragma SDS data copy

Dependence inter

This is a simple example to demonstrate inter dependence attribute using vertical convolution example. Using inter dependence attribute user can provide additional dependency details to compiler which allow compiler to perform unrolling/pipelining to get better performance.

Key Concepts:

- Inter Dependence

Keywords:

- DEPENDENCE

- inter

Direct connect

This is a simple example of matrix multiplication with matrix addition (Out = (A x B) + C) to demonstrate direct connection which helps to achieve increasing in system parallelism and concurrency.

Key Concepts:

- Direct Connection

- Multiple Accelerators

Keywords:

- #pragma SDS data access_pattern(in1:SEQUENTIAL, in2:SEQUENTIAL, out:SEQUENTIAL)

Dma sg

This example demonstrates how to use Scatter-Gather DMAs for data transfer to/from hardware accelerator.

Key Concepts:

- Scatter Gather DMA

Keywords:

- #pragma SDS access_parttern(a:SEQUENTIAL)

- #pragma SDS data_mover(a:AXIDMA_SG)

- #pragma SDS data copy

Dma simple

This example demonstrates how to insert Simple DMAs for data transfer between User program and hardware accelerator.

Key Concepts:

- Simple DMA

Keywords:

- #pragma SDS access_parttern(a:SEQUENTIAL)

- #pragma SDS data_mover(a:AXIDMA_SIMPLE)

- #pragma SDS data copy

Full array 2d

This is a simple example of accessing full data from 2D array.

Key Concepts:

- 2D data array access

Hello vadd

----------

This is a basic hello world kind of example which demonstrates how to achieve vector addition using hardware function.

Key Concepts:

- - Loop Pipelining

Keywords:

- - #pragma HLS PIPELINE

Lmem 2rw

This is a simple example of vector addition to demonstrate how to utilize both ports of Local Memory.

Key Concepts:

- Hardware Function Optimization

- 2port BRAM Utilization

- Two read/write Local Memory

Keywords:

- #pragma HLS UNROLL FACTOR=2

Loop fusion

This example will demonstrate how to fuse two loops into one to improve the performance of a C/C++ hardware function.

Key Concepts:

- Hardware Function Optimization

- Loop Fusion

- Loop Pipelining

Keywords:

- #pragma HLS PIPELINE

Loop perfect

This nearest neighbor example is to demonstrate how to achieve better performance using perfect loop.

Key Concepts:

- Loop perfect

Keywords:

- #pragma HLS PIPELINE

- #pragma HLS ARRAY_PARTITION

Loop pipeline

This example demonstrates how loop pipelining can be used to improve the performance of a hardware function.

Key Concepts:

- Loop Pipelining

Keywords:

- #pragma HLS PIPELINE

Loop reorder

This is a simple example of matrix multiplication (Row x Col) to demonstrate how to achieve better pipeline II factor by loop reordering.

Key Concepts:

- Hardware Function Optimization

- Loop Reorder to Improve II

Keywords:

- #pragma HLS PIPELINE

- #pragma HLS ARRAY_PARTITION

Row array 2d

This is a simple example of accessing each row of data from 2D array.

Key Concepts:

- Row of 2D data array access

Keywords:

- hls::stream

Shift register

This example demonstrates how to shift values in each clock cycle.

Key Concepts:

- Hardware Function Optimization

- Shift Register

- FIR

Keywords:

- #pragma HLS ARRAY_PARTITION

Systolic array

This is a simple example of matrix multiplication (Row x Col) to help developers learn systolic array based algorithm design. Note : Systolic array based algorithm design is well suited for FPGA.

Key Concepts:

- Systolic Array

Keywords:

- #pragma HLS PIPELINE

- #pragma HLS ARRAY_PARTITION

Sys port

This is a simple example which demonstrates sys_port usage.

Key Concepts:

- sys_port

- memory interface

- memory non-caching

Keywords:

- #pragma SDS data sys_port

- #pragms HLS PIPELINE

- sds_alloc_non_cacheable

Wide memory rw

This is a simple example of vector addition to demonstrate Wide Memory Access using structure data type of 128bit wide. Based on input argument type, sds++ compiler will figure out the memory interface datawidth of hardware accelerator.

Key Concepts:

- wide memory access

- burst read and write

- custom datatype

Keywords:

- struct

Window array 2d

This is a simple example of accessing window of data from 2D array.

Key Concepts:

- Window of 2D data array access

Keywords:

- #pragma HLS DATAFLOW

- #pragma HLS PIPELINE

- #pragma HLS stream

File IO Video Processing

Linux video processing application that reads input video from a file and writes out the output video to a file. Video processing includes Motion Adaptive Noise Reduction (MANR) followed by a Sobel filter for edge detection. You can run it by supplying a 1080p YUV422 file as input with limiting number of frames to a maximum of 20 frames.

Key Concepts:

- Video processing from file to file

- Direct connection of HW accelerated blocks

Select the "File IO Video Processing" template an compile for Linux target as project te22. Copy result to root of SD card. Copy also the input file input.yuv (82 944 000 bytes) to the root of the SD card. Login and cd to /media Run demo from terminal or from display+keyboard by comman ./te22.elf ./input.yuv 20 3 ./output.yuv

The output.yuv file contains 20 frames of 1080p vido in YUV422 format with computed edges. Copy output.yuv file to PC and visualise it in yuvplayer (size 1920x1080 colour YUV422).

File IO Dense Optical Flow

Linux video processing application that reads input video from a file and writes out the output video to a file. Video processing performs LK Dense Optical Flow over two Full HD frames video file. You can run it by supplying a 1080p YUV422 file route85_1920x1080.yuv as input.

Key Concept:s

- Video processing from file to file

- Direct connection of HW accelerated blocks

- Top down methodology with detailed description in Xilinx UG1235 (v2017.1) June 20. 2017.

Select the "File IO Dense Optical Flow" template an compile for Linux target as project te23. Copy result to root of SD card. Copy also the input file route85_1920x1080.yuv (8 294 400 bytes) to the root of the SD card. Login and cd to /media Run demo from terminal or from display+keyboard by command ./te23.elf

The OptFlow_1920x1080.yuv file is generated and stored on the SD card. It contains one 1080p frame in YUV422 format with computed dense optical flow vectors. Copy OptFlow_1920x1080.yuv file to PC and visualise it in yuvplayer (size 1920x1080 colour YUV422).

File IO Stereo Block Matching

Linux video processing application that reads input video from a file and writes out the output video to a file. Video processing performs Stereo Block Matching to calculate depth in a single sample stereo video file desk_1280x720.yuv in YUV422 format as input and single frame Disparity_640x720.yuv in YUV422 format as output, indicating the depth of objects.

Key Concepts:

- Video processing from file to file

- Bottom Up methodology with detailed description in Xilinx UG1235 (v2017.1) June 20. 2017.

Select the "File IO Stereo Block Matching" template an compile for Linux target as project te24. Copy result to root of SD card. Copy also the input file desk_1280x720.yuv (1 843 200 bytes) to the root of the SD card. Login and cd to /media Run demo from terminal or from display+keyboard by command ./te24.elf

/* USB PHY */

/{

usb_phy0: usb_phy@0 {

compatible = "ulpi-phy";

#phy-cells = <0>;

reg = <0xe0002000 0x1000>;

view-port = <0x0170>;

drv-vbus;

};

};

&usb0 {

dr_mode = "host";

//dr_mode = "peripheral";

usb-phy = <&usb_phy0>;

};

/* I2C1 */

&i2c1 {

#address-cells = <1>;

#size-cells = <0>;

i2cmux0: i2cmux@70 {

compatible = "nxp,pca9544";

#address-cells = <1>;

#size-cells = <0>;

reg = <0x70>;

i2c1@0 {

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

id_eeprom@50 {

compatible = "atmel,24c32";

reg = <0x50>;

};

};

i2c1@1 { // Display Interface Connector

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

};

i2c1@2 { // HDMI Interface Connector

#address-cells = <1>;

#size-cells = <0>;

reg = <2>;

};

i2c1@3 { // Camera Interface Connector

#address-cells = <1>;

#size-cells = <0>;

reg = <3>;

};

};

};

|

Kernel

Activate:

- CONFIG_XILINX_GMII2RGMII

- CONFIG_USB_USBNET

- CONFIG_USB_NET_SMSC95XX

- CONFIG_USBIP_CORE

- RTC_DRV_ISL12022

Rootfs

Activate:

- i2c-tools

Applications

startup

Script App to load init.sh from SD Card if available.

See: \os\petalinux\project-spec\meta-user\recipes-apps\startup\files

Additional Software

| HTML |

|---|

<!--

Add Description for other Software, for example SI CLK Builder ...

--> |

No additional software is neededThe Disparity_640x720.yuv file is generated and stored on the SD card. It contains one 640x720 frame in YUV422 format indicating the depth of objects. Copy Disparity_640x720.yuv file to PC and visualise it in yuvplayer (size 640x720 colour YUV422) The input file desk_1280x720.yuv can be visualised by yuvplayer (size 1280x720 colour YUV422). It contains side by side two colour frames from a stereo camera.

Appx. A: Change History and Legal Notices

...

| Date | Document Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

| Work in progress | ||||||||||||||||||||||

| 2018- | 10-19v.21 | John Hartfiel | Work in progress | 2017-09-1101-31 | v.1 |

| Initial release | ||||||||||||||||||

| All |

|

...