Page History

...

Example show, how to reconfigure SI5338 with MCS and monitor CLK. Additional Microblaze MicroBlaze is add for Hello TE0741 example.

...

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2018-04-16 | 2017.4 | TE0741-test_board-vivado_2017.4-build_07_20180416142156.zip TE0741-test_board_noprebuilt-vivado_2017.4-build_07_20180416142217.zip | John Hartfiel |

|

...

Not used on this Example.

JTAG

Not used on this Example.

Usage

- Connect JTAG and power on PCB

- Open Vivado HW Manager

- Program FPGA with Bitfile from "prebuilt\hardware\<short dir>"

Usage

- Prepare HW like described on section Programming

- Connect UART USB

- Prepare HW like described on section Programming

- Connect UART USB (most cases same as JTAG)

- Power on PCB

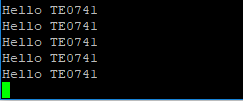

Note: FPGA Loads Bitfile from Flash,MCS Firmware configure SI5338 and starts Microblaze, Hello TE0741 from Bitfile Firmware Example will be run on UART console.

Do not reboot, if Bitfile programming over JTAG is used as programming method.

UART

Open Serial Console (e.g. putty)

- Speed: 9600

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

Todo Picture

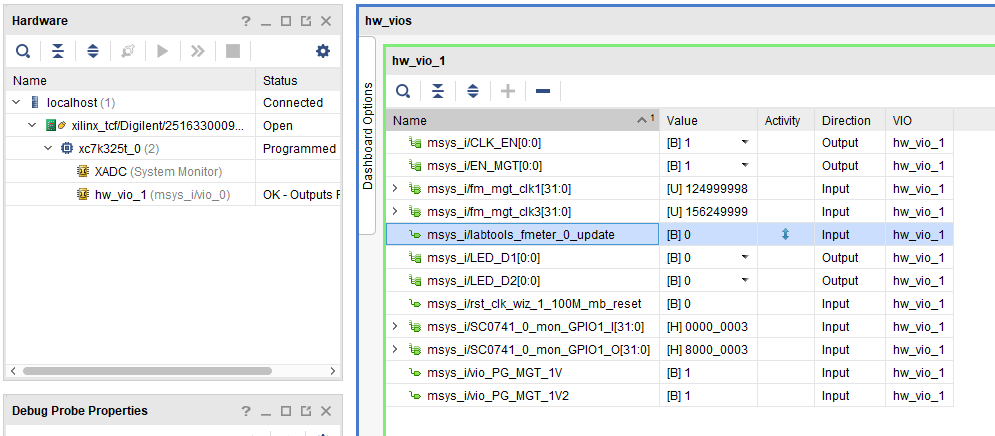

Vivado HW Manager:

- Open Vivado HW-Manager and add VIO signal to dashboard (*.ltx located on prebuilt folder).

- Set radix from VIO signals (MGT...) to unsigned integer.

Note: Frequency Counter is inaccurate and displayed unit is Hz - MGT REFREFCL1~125MHz, MIGGT_50MHZ~50MHz., CLK1B ~50MHz, CLK0~100MHz

- Additional Infos: System reset from MCS and GIO outputs

- REFCLK3~156,25MHz (default off, configured with MCS Firmware)

- LED_D1/D2 control

- SI5338 25MHz REF CLK Enable

- MGT Power Monitoring+MGT Enable

- Set radix from VIO signals (MGT...) to unsigned integer.

Todo Picture

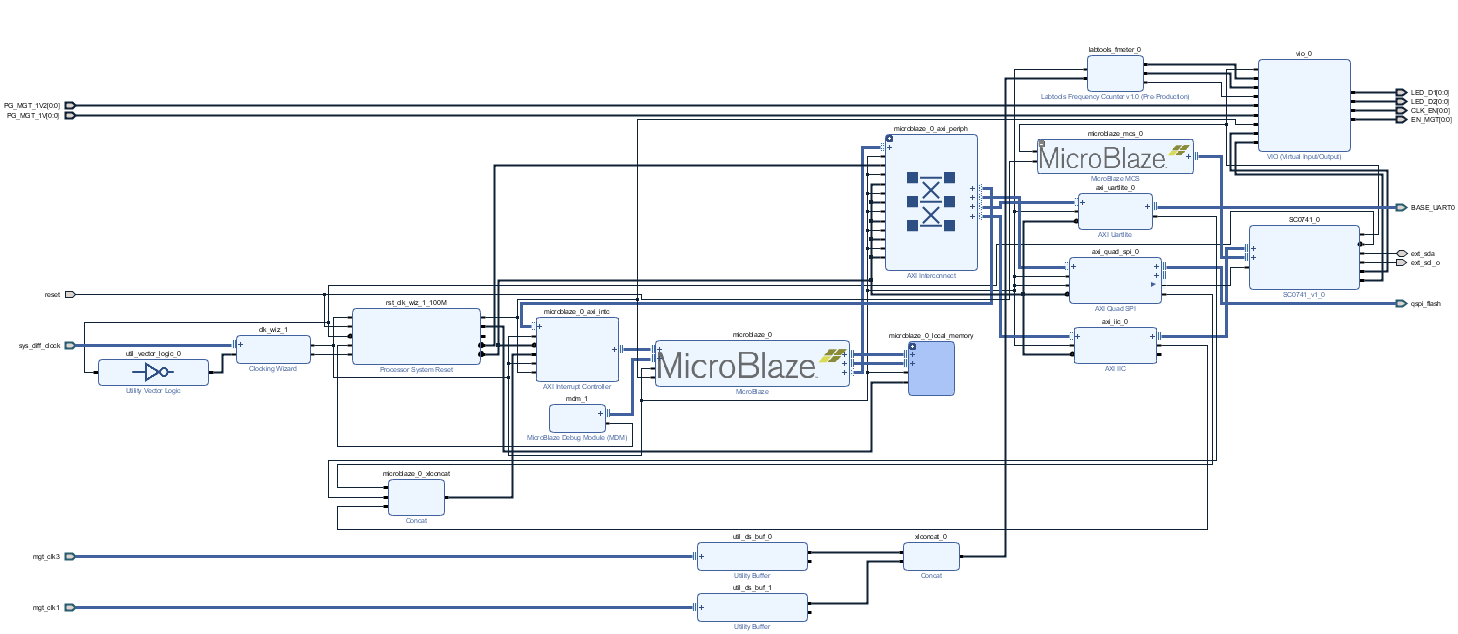

System Design - Vivado

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

Block Design

Todo

Constrains

Basic module constrains

...

| Code Block | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

#LED

set_property PACKAGE_PIN D26 [get_ports {LED_D1[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED_D1[0]}]

set_property PACKAGE_PIN E26 [get_ports {LED_D2[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED_D2[0]}]

#MGT Power

set_property PACKAGE_PIN G25 [get_ports {PG_MGT_1V2[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {PG_MGT_1V2[0]}]

set_property PACKAGE_PIN K23 [get_ports {PG_MGT_1V[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {PG_MGT_1V[0]}]

set_property PACKAGE_PIN H22 [get_ports {EN_MGT[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {EN_MGT[0]}]

#SI5338 CLK

set_property PACKAGE_PIN C26 [get_ports {CLK_EN[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {CLK_EN[0]}]

#I2C PLL SI5338

set_property PACKAGE_PIN A20 [get_ports ext_scl_o]

set_property IOSTANDARD LVCMOS33 [get_ports ext_scl_o]

set_property PACKAGE_PIN B21 [get_ports ext_sda]

set_property IOSTANDARD LVCMOS33 [get_ports ext_sda] |

| Code Block | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

#Fmeter can be ignored, it's only simple measurement

set_false_path -from [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/CLK}] -to [get_pins {msys_i/labtools_fmeter_0/U0/F_reg[*]/D}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/RSTC}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/RSTA}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/RSTB}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/CEALUMODE}]

set_false_path -from [get_pins msys_i/labtools_fmeter_0/U0/toggle_reg/C] -to [get_pins {msys_i/labtools_fmeter_0/U0/FMETER_gen[*].COUNTER_F_inst/bl.DSP48E_2/RSTCTRL}]

set_false_path -from [get_clocks -of_objects [get_pins msys_i/clk_wiz_1/inst/mmcm_adv_inst/CLKOUT0]] -to [get_clocks {msys_i/util_ds_buf_0/U0/IBUF_OUT[0]}]

set_false_path -from [get_clocks -of_objects [get_pins msys_i/clk_wiz_1/inst/mmcm_adv_inst/CLKOUT0]] -to [get_clocks {msys_i/util_ds_buf_1/U0/IBUF_OUT[0]}]

|

...

Overview

Content Tools