Page History

...

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2018-04-26 | 2017.4 | TE0715-test_board-vivado_2017.4-build_07_20180426171530.zip TE0715-test_board_noprebuilt-vivado_2017.4-build_07_20180426171546.zip | John Hartfiel |

|

| 2018-03-27 | 2017.4 | te0715-test_board-vivado_2017.4-build_07_20180327223552.zip te0715-test_board_noprebuilt-vivado_2017.4-build_07_20180327223606.zip | John Hartfiel |

|

| 2018-01-05 | 2017.4 | te0715-test_board-vivado_2017.4-build_01_20180105195436.zip te0715-test_board_noprebuilt-vivado_2017.4-build_01_20180105195452.zip | John Hartfiel |

|

| 2017-11-10 | 2017.2 | te0715-test_board-vivado_2017.2-build_05_20171110134232.zip te0715-test_board_noprebuilt-vivado_2017.2-build_05_20171110134247.zip | John Hartfiel |

|

| 2017-10-19 | 2017.2 | te0715-test_board-vivado_2017.2-build_04_20171019141808.zip te0715-test_board_noprebuilt-vivado_2017.2-build_04_20171019141825.zip | John Hartfiel |

|

| 2017-09-22 | 2017.2 | te0715-test_board-vivado_2017.2-build_02_20170927143412.zip te0715-test_board_noprebuilt-vivado_2017.2-build_02_20170927143427.zip | John Hartfiel |

|

...

| Module Model | Board Short Name | PCB Revision Support | DDR | QSPI Flash | Others | Notes | ||

|---|---|---|---|---|---|---|---|---|

| te0715TE0715-03-15-1c 1C | 03_15_1c | REV01,02,03 | 1GB | 32 | ||||

| te0715TE0715-03-15-1i 1I | 03_15_1i | REV01,02,03 | 1GB | 32 | ||||

| te0715TE0715-03-15-2i 2I | 03_15_2i | REV01,02,03 | 1GB | 32 | ||||

| te0715TE0715-03-30-1c 1C | 03_30_1c | REV01,02,03 | 1GB | 32 | ||||

| te0715TE0715-03-30-1i 1I | 03_30_1i | REV01,02,03 | 1GB | 32 | ||||

| te0715TE0715-03-30-3e 3E | 03_30_3e | REV01,02,03 | 1GB | 32 | ||||

| te0715TE0715-04-15-1c 1C | 04_15_1c | REV04 | 1GB_L | 32 | ||||

| te0715TE0715-04-15-1i 1I | 04_15_1i | REV04 | 1GB_L | 32 | ||||

| te0715TE0715-04-15-2i 2I | 04_15_2i | REV04 | 1GB_L | 32 | ||||

| te0715TE0715-04-30-1c 1C | 04_30_1c | REV04 | 1GB_L | 32 | ||||

| TE0715-04-30-1I | 04_30_1i | REV04 | 1GB_L | 32 | ||||

| TE0715te0715-04-30-1i 3E | 04_30_1i3e | REV04 | 1GB_L | 32 | ||||

| te0715TE0715-04-3012s-3e 04_30_3e1C | 12s | REV04 | 1GB_L | 32 | te0715 | |||

TE0715-04- | 12s30- | 1c12s 1IA | 04_30_1i | REV04 | 1GB_L | 32 | Micron instead of Spansion Flash |

Design supports following carriers:

| Carrier Model | Notes | |

|---|---|---|

| TE0701 | ||

| TE0703 | used as reference carrier | |

| TE0705 | ||

| TE0706 | ||

| TEBA0841 |

Additional HW Requirements:

...

| Note |

|---|

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first lunch. |

...

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

...

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

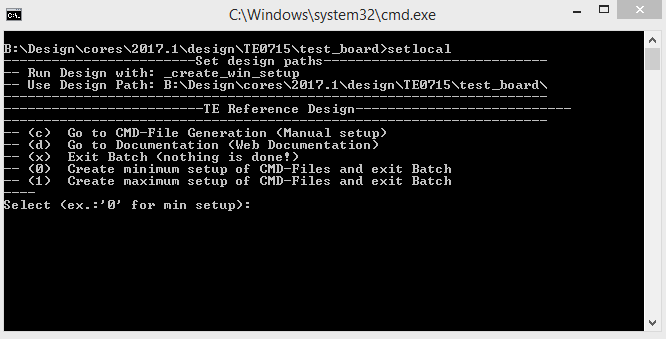

- Run _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter for minimum setup

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Create Linux (uboot.elf and image.ub) with exported HDF

- HDF is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

Note: run init_config.sh before you start petalinux config. This will set correct temporary path variable.

- Use TE Template from /os/petalinux

- HDF is exported to "prebuilt\hardware\<short name>"

- Add Linux files (uboot.elf and image.ub) to prebuilt folder

- "prebuilt\os\petalinux\default" or "prebuilt\os\petalinux\<short name>"

Notes: Scripts select "prebuilt\os\petalinux\<short name>", if exist, otherwise "prebuilt\os\petalinux\default"

- "prebuilt\os\petalinux\default" or "prebuilt\os\petalinux\<short name>"

- Generate Programming Files with HSI/SDK

- Run on Vivado TCL: TE::sw_run_hsi

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk

Note: See SDK Projects

- Run on Vivado TCL: TE::sw_run_hsi

...

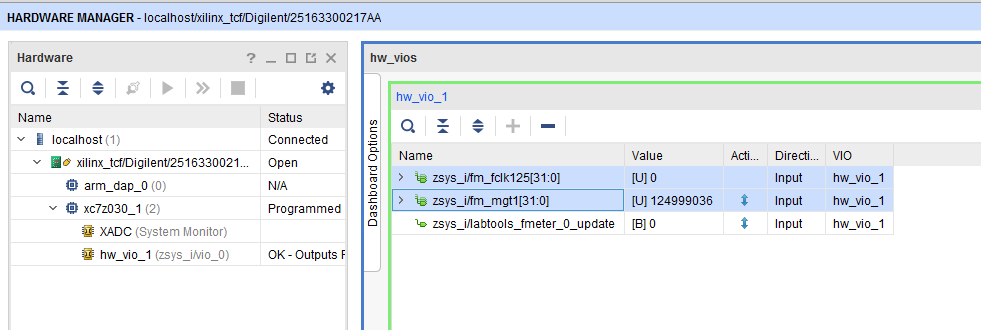

MGT CLK is configured to 125MHz by default, FCLK is not configured by default (optional possible see FSBL description).

System Design - Vivado

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

...

| Type | Note |

|---|---|

| DDR | --- |

| QSPI | MIO |

| I2C0 | EMIO- NC |

| I2C1 | MIO |

| UART0 | MIO |

| GPIO | MIO |

| SD0 | MIO |

| USB0 | MIO |

| ETH0 | MIO |

| TTC | EMIO |

Constrains

Basic module constrains

...

| Code Block | ||

|---|---|---|

| ||

/include/ "system-conf.dtsi"

/ {

};

/* default */

/* ETH PHY */

&gem0 {

status = "okay";

ethernet_phy0: ethernet-phy@0 {

compatible = "marvell,88e1510";

device_type = "ethernet-phy";

reg = <0>;

};

};

/* USB PHY */

/{

usb_phy0: usb_phy@0 {

compatible = "ulpi-phy";

//compatible = "usb-nop-xceiv";

#phy-cells = <0>;

reg = <0xe0002000 0x1000>;

view-port = <0x0170>;

drv-vbus;

};

};

&usb0 {

dr_mode = "host";

//dr_mode = "peripheral";

usb-phy = <&usb_phy0>;

};

/* I2C */

// i2c PLL: 0x70, i2c eeprom: 0x50

&i2c1 {

rtc@6F { // Real Time Clock

compatible = "isl12022";

reg = <0x6F>;

};

};

|

Kernel

Activate:

- RTC_DRV_ISL12022

...

| Date | Document Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||

| v.29 | John Hartfiel |

| |||||||||||||||||||||||

| 2018-02-13 | v.28 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-11-10 | v.22 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-19 | v.21 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-19 | v.20 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-06 | v.18 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-02 | v.14 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-09-28 | v.13 | John Hartfiel | Release 2017.2 | ||||||||||||||||||||||

| 2017-09-11 | v.1 |

| Initial release | ||||||||||||||||||||||

| All |

|

Legal Notices

| Include Page | ||||

|---|---|---|---|---|

|