Page History

...

| Issues | Description | Workaround/Solution | To be fixed version | ||||

|---|---|---|---|---|---|---|---|

| Flash access on Linux | Device tree is not correct on Linux | add compatibility to "compatible “jedec,spi-nor”" | next design update | --- | --- | --- | --- |

Requirements

Software

| HTML |

|---|

<!-- Add needed external Software --> |

...

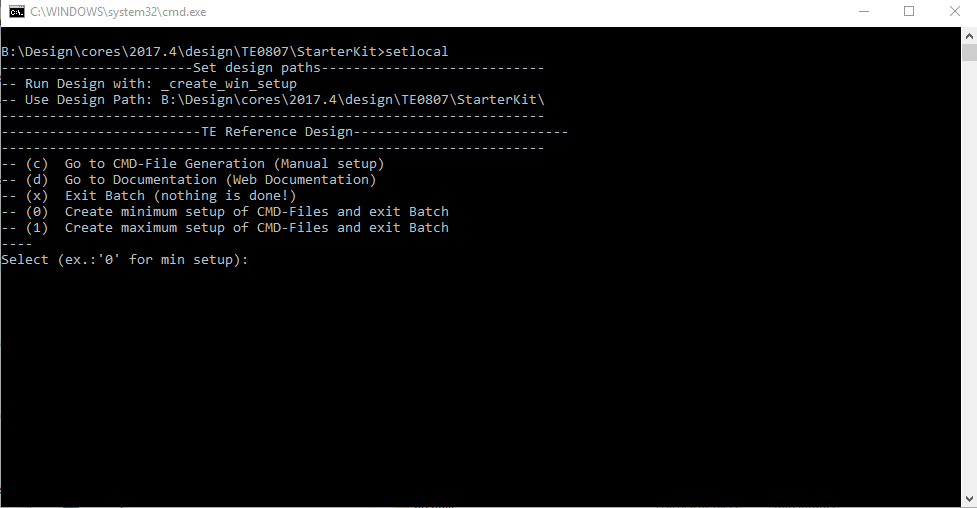

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter for minimum setup

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

Important: Use Board Part Files, which ends with *_tebf0808

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Create Linux (bl31.elf, uboot.elf and image.ub) with exported HDF

- HDF is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

Note: run init_config.sh before you start petalinux config. This will set correct temporary path variable.

- Use TE Template from /os/petalinux

- HDF is exported to "prebuilt\hardware\<short name>"

- Add Linux files (bl31.elf, uboot.elf and image.ub) to prebuilt folder

- "prebuilt\os\petalinux\default" or "prebuilt\os\petalinux\<short name>"

Notes: Scripts select "prebuilt\os\petalinux\<short name>", if exist, otherwise "prebuilt\os\petalinux\default"

- "prebuilt\os\petalinux\default" or "prebuilt\os\petalinux\<short name>"

- Generate Programming Files with HSI/SDK

- Run on Vivado TCL: TE::sw_run_hsi

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk

Note: See SDK Projects

- Run on Vivado TCL: TE::sw_run_hsi

...

| Code Block | ||||

|---|---|---|---|---|

| ||||

#LED_HD SC0 J3:31

set_property PACKAGE_PIN K11 [get_ports {LED_HD[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {LED_HD[0]}]

#LED_XMOD SC17 J3:48

set_property PACKAGE_PIN B12 [get_ports {LED_XMOD2[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {LED_XMOD2[0]}]

#System Controller IP

#J3:32

set_property PACKAGE_PIN J12 [get_ports BASE_sc10_io]

#J3:34

set_property PACKAGE_PIN K13 [get_ports BASE_sc11]

#J3:36

set_property PACKAGE_PIN A13 [get_ports BASE_sc12]

#J3:38

set_property PACKAGE_PIN A14 [get_ports BASE_sc13]

#J3:40

set_property PACKAGE_PIN E12 [get_ports BASE_sc14]

#J3:42

set_property PACKAGE_PIN F12 [get_ports BASE_sc15]

#J3:41

set_property PACKAGE_PIN E14 [get_ports BASE_sc5]

#J3:45

set_property PACKAGE_PIN C12 [get_ports BASE_sc6]

#J3:47

set_property PACKAGE_PIN D12 [get_ports BASE_sc7]

set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc5]

set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc6]

set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc7]

set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc10_io]

set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc11]

set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc12]

set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc13]

set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc14]

set_property IOSTANDARD LVCMOS18 [get_ports BASE_sc15]

# PLL

#J4:74

#set_property PACKAGE_PIN AF15 [get_ports {si570_clk_p[0]}]

#set_property IOSTANDARD LVDS [get_ports {si570_clk_p[0]}]

#set_property IOSTANDARD LVDS [get_ports {si570_clk_n[0]}]

# Audio Codec

#LRCLK J3:49 B47_L9_N

set_property PACKAGE_PIN G14 [get_ports LRCLK ]

#BCLK J3:51 B47_L9_P

set_property PACKAGE_PIN H14 [get_ports BCLK ]

#DAC_SDATA J3:53 B47_L7_N

set_property PACKAGE_PIN C13 [get_ports DAC_SDATA ]

#ADC_SDATA J3:55 B47_L7_P

set_property PACKAGE_PIN D14 [get_ports ADC_SDATA ]

set_property IOSTANDARD LVCMOS18 [get_ports LRCLK ]

set_property IOSTANDARD LVCMOS18 [get_ports BCLK ]

set_property IOSTANDARD LVCMOS18 [get_ports DAC_SDATA ]

set_property IOSTANDARD LVCMOS18 [get_ports ADC_SDATA ]

# CAN

#CAN RX SC19 J3:52 B47_L10_P

#CAN TX SC18 J3:50 B47_L10_N

#CAN S SC16 J3:46 B47_L12_N

set_property PACKAGE_PIN A12 [get_ports CAN_0_S ]

set_property IOSTANDARD LVCMOS18 [get_ports CAN_0_S ]

set_property PACKAGE_PIN C14 [get_ports CAN_0_rx ]

set_property IOSTANDARD LVCMOS18 [get_ports CAN_0_rx ]

set_property PACKAGE_PIN B14 [get_ports CAN_0_tx ]

set_property IOSTANDARD LVCMOS18 [get_ports CAN_0_tx ]

|

...

| Date | Document Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||

| v.9 | John Hartfiel |

| |||||||||||||||||||||||

| 2018-01-29 | v.4 | John Hartfiel |

| ||||||||||||||||||||||

| 2018-01-18 | v.3 | John Hartfiel |

| ||||||||||||||||||||||

| All |

|

Legal Notices

| Include Page | ||||

|---|---|---|---|---|

|

Overview

Content Tools