...

The TEC0850 board is equipped with 3 CompactPCI high-speed backplane connectors which provide serial high-speed interconnects with transmission rates up to 12 Gb/s to the Zynq MPSoCs MGT lanes. On the cPCI connectors are also available single-ended Zynq MPSoC PL HP I/O's, high-speed USB 2.0 interface , and single-ended FPGA I/O pins Zynq MPSoC and 's of the System Controller FPGA.

The connectors support single-ended and differential signaling as to the Zynq MPSoC PL HP banks 65 and 66 as those FPGA I/O's are routed from the FPGA banks as LVDS-pairs to the backplane connector.

The TEC0850 board is designed to be connected to the System Slot of the backplane connector, whereby 4 of the 6 connectors of the System Slot configuration are fitted to the TEC0850 board.

...

| Scroll Title |

|---|

| anchor | Table_default_mio |

|---|

| title | Table 13: Default MIO Configuration |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| PS MIO | Function | Connected to |

|---|

| 0 | QSPI* | U24-B2, CLK |

|---|

| 1 | QSPI* | U24-D2, DO/IO1

|

|---|

| 2 | QSPI* | U24-C4, WP/IO2

|

|---|

| 3 | QSPI* | U24-D4, HOLD/IO3 |

|---|

| 4 | QSPI* | U24-D3, DI/IO0 |

|---|

| 5 | QSPI* | U24-C2, CS |

|---|

| 6 | - | not connected |

|---|

| 7 | QSPI* | U25-C2, CS |

|---|

| 8 | QSPI* | U25-D3, DI/IO0 |

|---|

| 9 | QSPI* | U25-D2, DO/IO1 |

|---|

| 10 | QSPI* | U17-C4, WP/IO2 |

|---|

| 11 | QSPI* | U25-D4, HOLD/IO3 |

|---|

| 12 | QSPI* | U25-B2, CLK |

|---|

| 13 ... 15 | - | not connected |

|---|

| 16 | USB2 PHY Reset | USB2 PHY U11, pin27 |

|---|

| 17 | USB2 PHY Reset | USB2 PHY U13, pin27 (def. not solderedoptional, PHY not fitted by default) |

|---|

| 18 ... 19 | - | not connected |

|---|

| 20 ...21 | PS MIO I²C | I²C peripherals |

|---|

| 22 ... 25 | user MIO | SC FPGA U18, bank 2 |

|---|

| 26 ... 38 | RGMII | GbE PHY U20 |

|---|

| 39 ... 44 | - | not connected |

|---|

| 45 ... 51 | SD IO | MicroSD Card socket J11 |

|---|

| 52 ... 63 | USB2 ULPI | USB2 PHY U11 |

|---|

| 64 ... 75 | USB2 ULPI | USB2 PHY U13 (def. not solderedoptional, PHY not fitted by default) |

|---|

| 76 ... 77 | ETH MDC / MDIO | GbE PHY U20 |

|---|

* Flash is used as QSPI dual parallel |

...

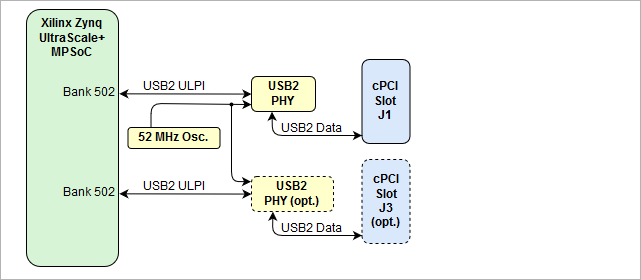

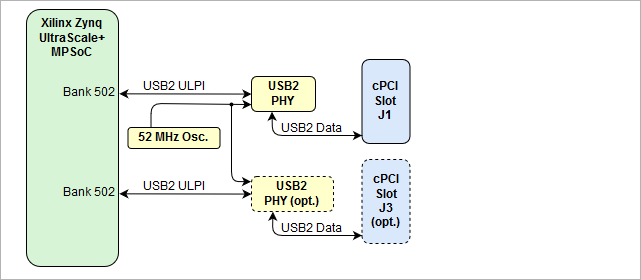

USB2 PHY U11 is provided by USB3320 from Microchip. The ULPI interface is connected to the Zynq Ultrascale+ PS USB0. I/O voltage is fixed at 1.8V and PHY reference clock input is supplied from the on-board 52.000000 MHz oscillator U12. There is also the option to equip the TEC0850 board with a second USB2 PHY U13 connected to the optional cPCI backplane connector J3. Both, the optional USB2 PHY U13 and cPCI connector J3 are not fitted by default.

| Scroll Title |

|---|

| anchor | Figure_usb2_phy |

|---|

| title | Figure 20: TEC0850 cPCI USB2 interface |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 12 |

|---|

| diagramName | TEC0850 USB2 PHY |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

|

|

...

| Scroll Title |

|---|

| anchor | Table_usb2_phy_io |

|---|

| title | Table 22: USB2 ULPI interface description |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| USB2 PHY U11 Pin | Connected to | Notes |

|---|

| ULPI | PS bank MIO52 ... MIO63 | Zynq Ultrascale+ USB0 MIO pins are connected to the PHY | | REFCLK | - | 52MHz from onboard oscillator U12 | | REFSEL[0..2] | - | All pins set to GND selects the external reference clock frequency (52.000000 MHz) | | RESETB | Zynq MPSoC MIO16, pin AM16 | Low active USB2 PHY Reset

| | DP, DM | cPCI connector J1 | USB2 data lane | | CPEN | - | External USB power switch active-high enable signal | | VBUS | 5V | Connected to USB VBUS onboard 5V voltage level via a series of resistors, see schematic | | ID | 3.3V | B-device |

|

Gigabit Ethernet PHY

| optional USB2 PHY U13 Pin | Connected to | Notes |

|---|

| ULPI | PS bank MIO64 ... MIO75 | Zynq Ultrascale+ USB1 MIO pins are connected to the PHY | | REFCLK | - | 52MHz from onboard oscillator U12 | | REFSEL[0..2] | - | All pins set to GND selects the external reference clock frequency (52.000000 MHz) | | RESETB | Zynq MPSoC MIO17, pin AP16 | Low active USB2 PHY Reset | | DP, DM | optional cPCI connector J3 | USB2 data lane | | CPEN | - | External USB power switch active-high enable signal | | VBUS | 5V | Connected to onboard 5V voltage level via a series of resistors, see schematic | | ID | 3.3V | B-device |

|

Gigabit Ethernet PHY

Onboard Gigabit Ethernet PHY U20 is provided Onboard Gigabit Ethernet PHY U20 is provided with Marvell Alaska 88E1512, which use MDIO address 1. The Ethernet PHY RGMII interface is connected to the Zynq Ultrascale+ Ethernet0 PS GEM3. I/O voltage is fixed at 1.8V for HSTL signaling. The reference clock input of the PHY is supplied from the on-board 25.000000 MHz oscillator U21.

...

| Scroll Title |

|---|

| anchor | Table_Document_Change_History |

|---|

| title | Table 34: Document change history |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Constributor | Description |

|---|

| Create | Modified date | | dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| showVersions | false | | Page info |

|---|

| infoType | Current version |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| - added information about the option

of second USB2 PHY (not fitted by default)

|

|---|

2018-09-19 | | | | | 29 Aug | v.93 | Ali Naseri , Oleksandr Kiyenko , John Hartfiel | | | -- | all | | Page info |

|---|

| infoType | Modified users |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| |

|

...

| Include Page |

|---|

| IN:Legal Notices |

|---|

| IN:Legal Notices |

|---|

|

QSPI* John Hartfiel