...

| Scroll pdf ignore |

|---|

Table of Contents |

Overview

The Cyclone10 LP Reference Kit is the world's first development board with a 55kLE Intel Cyclone 10 LP and a variety of interfaces for numerous applications. The board is comprehensively tested and ready for use with end products and can also be ordered in customer-specific variants according to your requirements.

...

Key Features

| Page properties |

|---|

|

Note:

'Key Features' description: Important components and connector or other Features of the module

→ please sort and indicate assembly options |

- Intel Cyclone 10 LP FPGA 10CL055YU484C8G, 55 kLE in 484-pin

- 16 MBit flash memory (optional up to 32 MBit possible)

- Integrated USB Programmer 2

- Connectors

- 256 MBit (optional up to 512 MBit possible) SDRAM

- 128 MBit (optional up to 512 MBit possible) User Quad-SPI Flash memory

- 64 MBit HyperRAM (optional up to 128 MBit possible)

- 2 x MAC address EEPROM

- 2 x Fast Ethernet PHY (10/100 Mbps)

- 8-channel, 12-bit, configurable ADC / DAC with on-chip reference

- Status LEDs, Power LED

- 13 x User LEDs

- 1 x 7-segment display

- 2 x reset buttons

- 5 x user buttons

Block Diagram

| Page properties |

|---|

|

add drawIO object here.

|

...

| Scroll Title |

|---|

| anchor | Figure_OV_BD |

|---|

| title | TEI0009 block diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 5 |

|---|

| diagramName | TEI0009_OV_BD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

|

|

Main Components

| Page properties |

|---|

|

Notes : - Picture of the PCB (top and bottom side) with labels of important components

- Add List below

|

...

- Barrel Jack, J12

- RJ45 socket, J8...9

- VGA Socket, J11

- Push button(Reset), S7

- Grove connector, J5

- Under/Over Voltage Protector, U9

- 7-segment LED, D11

- 1x6 pin header, J4

- 1x8 pin header, J2...3

- User Red LEDs, D2...9

- User Red LEDs, D13...17

- Push buttons, S1- S3...6

- Red LED (CONF_DONE), D10

- PSDRAM PSRAM memory, U3

- SDRAM memory, U10

- Voltage Regulator, U5- U7

- AD/DA Convertor, U2

- Pmod 2x6 SMD host socket, P1...6

- Intel Cyclone 10 LP, U1

- Config Device, U5

- 1x10 pin header, J1

- EEEPROM, U15- U18- U20

- FTDI FT2232H, U14

- Micro USB 2.0 receotacle 90, J10

- Push button (RST_GPIO), S2

- Oscillator, U22

- Ethernet PHY, U17- U19

- SPI Flash memory, U12

Initial Delivery State

| Page properties |

|---|

|

Notes : Only components like EEPROM, QSPI flash and DDR3 can be initialized by default at manufacture. If there is no components which might have initial data ( possible on carrier) you must keep the table empty |

...

| Scroll Title |

|---|

| anchor | Table_OV_IDS |

|---|

| title | Initial delivery state of programmable devices on the module |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Storage device name | Content | Notes |

|---|

SPI Flash |

|

| | EEPROM |

|

| | DDR3 SDRAM |

|

| | FTDI System Controller CPLD |

|

| | PSRAM |

|

| | Config Device |

|

|

|

Configuration Signals

| Page properties |

|---|

|

- Overview of Boot Mode, Reset, Enables.

|

...

| Scroll Title |

|---|

| anchor | Table_OV_RST |

|---|

| title | Reset process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Signal | Connected to | Note |

|---|

RESET | S1 (Push button) | Connected to nCONFIG | | EXT_RST | J3 (1x8 pin header) Bank 2 |

|

|

Signals, Interfaces and Pins

| Page properties |

|---|

|

Notes : - For carrier or stand-alone boards use subsection for every connector type (add designator on description, not on the subsection title), for example:

- For modules which needs carrier use only classes and refer to B2B connector if more than one is used, for example

|

I/Os on Pin Headers and Connectors

FPGA bank number and number of I/O signals connected to the B2B connector:

| Scroll Title |

|---|

| anchor | Table_SIP_B2B |

|---|

| title | General PL I/O to B2B connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| FPGA Bank | Connector | I/O Signal Count | Voltage Level | Notes |

|---|

| Bank 1 | J1 (Pin header) | 8 Single ended | 3.3 V |

| | J2 (Pin header) | 8 Single ended | 3.3 V |

| | J4 (Pin header) | 6 Single ended | 3.3 V |

| | Bank 2 | J3 (Pin header) | 1 Single ended | 3.3 V |

| | P1 (PMod SMD host socket) | 8 Single ended | 3.3 V |

| | P2 (PMod SMD host socket) | 8 Single ended | 3.3 V |

| | J11 (VGA host Socket) | 14 Single ended | 3.3 V |

| | Bank 6 | J5 (Grove connector) | 2 Single ended | 3.3 V |

| | Bank 7 | P5 (PMod SMD host socket) | 8 Single ended | 3.3 V |

| | P6 (PMod SMD host socket) | 8 Single ended | 3.3 V |

| | Bank 8 | P3 (PMod SMD host socket) | 8 Single ended | 3.3 V |

| | P4 (PMod SMD host socket) | 8 Single ended | 3.3 V |

|

|

PMod SMD Host Socket

TEI0009 has 6 PMod 2x6 SMD Host Socket 90° which are connected to Cyclon 10 LP.

| Scroll Title |

|---|

| anchor | Table_SIP_SMD |

|---|

| title | PMod SMD host socket information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Signals | Connected to | Notes |

|---|

| P1 | P1_IO1...8 | Bank 2 |

| | P2 | P2_IO1...8 | Bank 2 |

| | P3 | P3_IO1...8 | Bank 8 |

| | P4 | P4_IO1...8 | Bank 8 |

| | P5 | P5_IO1...8 | Bank 7 |

| | P6 | P6_IO1...8 | Bank 7 |

|

|

UART Interface

UART access to TEI0009 is available on 1x8 pin header J2.

| Scroll Title |

|---|

| anchor | Table_SIP_UART |

|---|

| title | UART interface information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Schematic | Pin Header | Connected to | Voltage Level | Notes |

|---|

| TXD | J2 | Bank 1 | 3.3 V |

| | RXD | J2 | Bank 1 | 3.3 V |

|

|

Micro USB2.0 Connector

U14(FTDI FT2232) can be accessed through Micro USB2.0 B Receptacle 90 (J10).

| Scroll Title |

|---|

| anchor | Table_SIP_USB |

|---|

| title | Micro USB2.0 B Receptacle 90 ° information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Schematic | Connected to | Voltage Level | Notes |

|---|

| USB_VBUS | GND |

|

| | D- | U14 (FTDI FT2232) | 3.3 V |

| | D+ | U14 (FTDI FT2232) | 3.3 V |

|

|

RJ45 Connectors

TEI0009 is equipped with two RJ45 connectors and two Ethernet PHYs. RJ45 connectors J8 and J9 are connected to Ethernet PHYs U17 and U19 respectively. .

| Scroll Title |

|---|

| anchor | Table_SIP_RJ45 |

|---|

| title | RJ45 connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pin | Schematic | ETH1 Pin | ETH2 Pin | Notes |

|---|

| TD+ | ETH_TX_P | U17- TXP | U19- TXP |

| | CT | ETH_CTREF_TCT | - | - | Connected to GND | | TD- | ETH_TX_N | U17- TXM | U19- TXM |

| | RD+ | ETH_RX_P | U17- RXP | U19- RXP |

| | CT | ETH_CTREF_RCT | - | - | Connected to GND | | RD- | ETH_RX_N | U17- RXM | U19- RXM |

| | LED Green | ETH_LED0 | U17- NWAYEN | U19- NWAYEN |

| | LED Yellow | ETH_LED1 | U17- SPEED | U19- SPEED |

|

|

VGA socket Connectors

VGA host socket is connected to Cyclone 10 LP through Bank 2.

| Scroll Title |

|---|

| anchor | Table_SIP_VGA |

|---|

| title | VGA host socket information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Schematic | Corresponding Signals | Connected to | Notes |

|---|

| VGA_RED | VGA_R0...3 | Bank 2 | Red channel | | VGA_GREEN | VGA_G0...3 | Bank 2 | Green channel | | VGA_BLUE | VGA_B0...3 | Bank 2 | Blue channel | | VGA_RGB_HSYNC | VGA_HS | Bank 2 | Horizontal sync | | VGA_RGB_VSYNC | VGA_VS | Bank 2 | Vertical sync |

|

On-board Peripherals

| Page properties |

|---|

|

Notes : - add subsection for every component which is important for design, for example:

- Two 100 Mbit Ethernet Transciever PHY

- USB PHY

- Programmable Clock Generator

- Oscillators

- eMMCs

- RTC

- FTDI

- ...

- DIP-Switches

- Buttons

- LEDs

|

...

| Scroll Title |

|---|

| anchor | Table_OBP |

|---|

| title | On board peripherals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Chip/Interface | Designator | Notes |

|---|

| SPI Flash memory | U12 |

| | SDRAM memory | U10 |

| | PSRAM memory | U3 |

| | 7 Segment | D11 |

| | FTDI FT2232 | U14 |

| | Ethernet PHY | U17, U19 |

| | Configuration Device | U5 |

| | AD/DA Converter | U2 |

| | EEPROM | U15, U18, U20 |

| | User LEDs | D2...D17 |

| | Oscillators | U16, U22 |

|

|

SPI Flash Memory

| Page properties |

|---|

|

Notes : Minimum and Maximum density of quad SPI flash must be mentioned for other assembly options. |

...

| Scroll Title |

|---|

| anchor | Table_OBP_SPI |

|---|

| title | Quad SPI interface MIOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pin | Schematic | Connected to | Notes |

|---|

| CS | F_CS | Bank 7 |

| | CLK | F_CLK | Bank 7 |

| | IO0...3 | F_IO0...3 | Bank 7 |

|

|

SDRAM Memory

| Page properties |

|---|

|

Notes : Minimum and Maximum density of DDR3 SDRAM must be mentioned for other assembly options. (pay attention to supported address length for DDR3) |

...

Part number: W9864G6JT-6-ND

Supply voltage: 3.3 V

- Clock Frequency: 166MHz

Temperature: 0°C ~ 70°C

PSRAM Memory

The TEI0009 is integrated with 64Mbit Pseudo Static Random Access Memory (SDRAM) using a self-refresh DRAM array organized as 8M words by 8 bits. The device supports a HyperBus interface, Very Low Signal Count (Address, Command and data through 8 DQ pins), Hidden Refresh Operation, and Automotive Temperature Operation.

Part number: IS66WVH8M8BLL

Supply voltage: 3.3 V

- Clock Frequency: 100MHz

Temperature: -40°C ~ 85°C

LED 7 Segment 4 Digit

the TEI0009 has a LED 7 Segment 4 Digit which is connected to Bank 6.

| Scroll Title |

|---|

| anchor | Table_OBP_7SEG |

|---|

| title | LED 7 Segment pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pin | Schematic | Connected to | Notes |

|---|

| A/L1 | SEG_CA | Bank 6 |

| | B/L2 | SEG_CB | Bank 6 |

| | C/L3 | SEG_CC | Bank 6 |

| | D | SEG_CD | Bank 6 |

| | E | SEG_CE | Bank 6 |

| | F | SEG_CF | Bank 6 |

| | G | SEG_CG | Bank 6 |

| | DP | SEG_CDP | Bank 6 |

| | A1 | SEG_AN | Bank 6 |

| | A2 | SEG_AN4 | Bank 6 |

| | A3 | SEG_AN3 | Bank 6 |

| | A4 | SEG_AN2 | Bank 6 |

| | L1-L3 | SEG_AN1 | Bank 6 |

|

|

FTDI FT2232H

The FTDI chip U14 converts signals from USB2.0 to a variety of standard serial and parallel interfaces. Refer to the FTDI data sheet to get information about the capacity of the FT2232H chip.

FTDI FT2232H chip is used in MPPSE mode for JTAG, 6 I/O's of Channel B are routed to FPGA bank 8 of the FPGA SoC and are usable for example as GPIOs, UART or other standard interfaces.

...

| Scroll Title |

|---|

| anchor | Table_OBP_FTDI |

|---|

| title | FTDI chip interfaces and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| FTDI Chip Pin | Signal Schematic Name | Connected to | Notes |

|---|

| ADBUS0 | TCK | Bank 1 | JTAG interface | | ADBUS1 | TDI | Bank 1 | | ADBUS2 | TDO | Bank 1 | | ADBUS3 | TMS | Bank 1 | | BDBUS0 | BDBUS0 | Bank 6 |

| | BDBUS1 | BDBUS1 | Bank 6 |

| | BDBUS2 | BDBUS2 | Bank 6 |

| | BDBUS3 | BDBUS3 | Bank 6 |

| | BDBUS4 | BDBUS4 | Bank 6 |

| | BDBUS5 | BDBUS5 | Bank 6 |

| | EECS | EECS | U15 (EEPROM) |

| | EECLK | EECLK | U15 (EEPROM) |

| | EEDATA | EEDATA | U15 (EEPROM) |

| | OSCI | CK12M | U16 (12MHz Oscillator) |

| | DM | D_N | J10 (Micro USB2.0) |

| | DP | D_P | J10 (Micro USB2.0) |

|

|

Ethernet PHY

The TEI0009 is equipped with two Ethernet PHY (U19, U17) which are connected to two RJ45 connectors.

| Scroll Title |

|---|

| anchor | Table_OBP_ETH |

|---|

| title | Ethernet PHY connections and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Ethernet Pin | Signals | ETH 1 | ETH 2 | Note |

|---|

| TXD0...3 | ETH_TXD0...3 | Bank 5 | Bank 5 |

| | TXC | ETH_TXC | Bank 5 | Bank 5 |

| | TXEN | ETH_TXEN | Bank 5 | Bank 5 |

| | RXD0...3 | ETH_RXD0...3 | Bank 5 | Bank 5 |

| | RXC//B-CAST_OFF | ETH_RXC | Bank 5 | Bank 5 |

| | RXER/ISO | ETH_RXER | Bank 5 | Bank 5 |

| | INTRP//NAND_Tree | ETH_INTRP | Bank 5 | Bank 5 |

| | XI | ETH_CLKIN | U22 (Oscillator) | U22 (Oscillator) |

| | MDC | ETH_MDC | Bank 5 | Bank 5 |

| | MDIO | ETH_MDIO | Bank 5 | Bank 5 |

| | COL/CONFIG0 | ETH_COL | Bank 5 | Bank 5 |

| | CRS/CONFIG1 | ETH_CRS | Bank 5 | Bank 5 |

| | RXDV/CONFIG2 | ETH_RXDV | Bank 5 | Bank 5 |

| | LED0/NWAYEN | ETH_LED0 | Bank 5 J8B (RJ45- Green LED) | Bank 5 J9B (RJ45-Green LED) |

| | LED1/SPEED | ETH_LED1 | Bank 5 J8C (RJ45-Yellow LED) | Bank 5 J9B (RJ45-Yellow LED) |

| | nRST | ETH_RST | Bank 5 | Bank 5 |

| | RXM | ETH_RX_N | J8 (RJ45) | J9 (RJ45) |

| | RXP | ETH_RX_P | J8 (RJ45) | J9 (RJ45) |

| | TXM | ETH_TX_N | J8 (RJ45) | J9 (RJ45) |

| | TXP | ETH_TX_P | J8 (RJ45) | J9 (RJ45) |

|

|

EEPROM

TEI0009 has three EEPROM, U15, U18 and U20. U15 containt FTDI FT2232H configuration.

...

| Scroll Title |

|---|

| anchor | Table_OBP_I2C_EEPROM |

|---|

| title | I2C address for EEPROM |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| I2C Address | Designator | Notes |

|---|

| 0x50 | U18 |

| | 0x52 | U20 |

|

|

LEDs

| Scroll Title |

|---|

| anchor | Table_OBP_LED |

|---|

| title | On-board LEDs |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Schematic | Designator | Color | Connected to | Active Level | Note |

|---|

| LED1...8 | D2...9 | Red | Bank 3 | High |

| | LED_PB1 | D13...17 | Red | Bank 7 | High |

| | CONF_DONE | D10 | Red | Bank 6 | Low |

|

|

Clock Sources

| Scroll Title |

|---|

| anchor | Table_OBP_CLK |

|---|

| title | Osillators |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Description | Frequency | Note |

|---|

| U22 | MEMS Oscillator | 25 MHz |

| | U16 | MEMS Oscillator | 12 MHz |

|

|

Power and Power-On Sequence

| Page properties |

|---|

|

In 'Power and Power-on Sequence' section there are three important digrams which must be drawn: - Power on-sequence

- Power distribution

- Voltage monitoring circuit

|

Power Supply

Power supply with minimum current capability of xx A for system startup is recommended.

Power Consumption

| Scroll Title |

|---|

| anchor | Table_PWR_PC |

|---|

| title | Power Consumption |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Power Input Pin | Typical Current |

|---|

| VIN | TBD* |

|

* TBD - To Be Determined

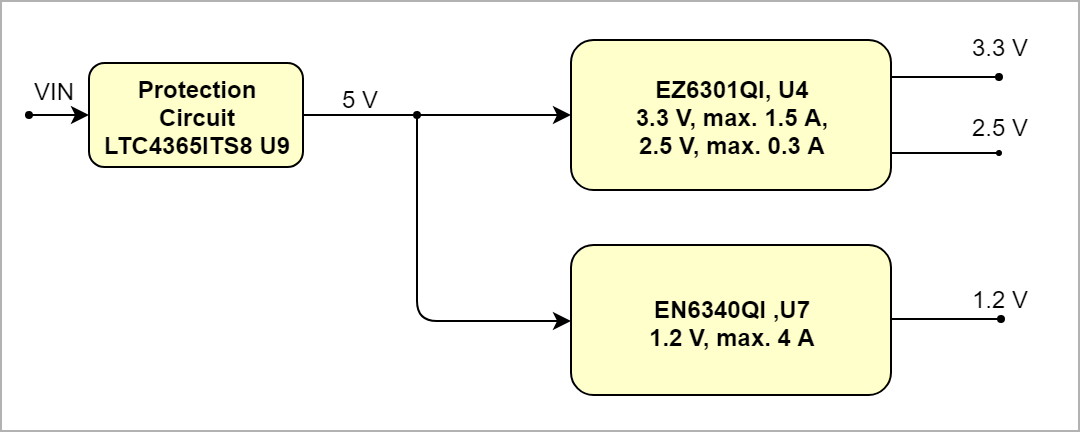

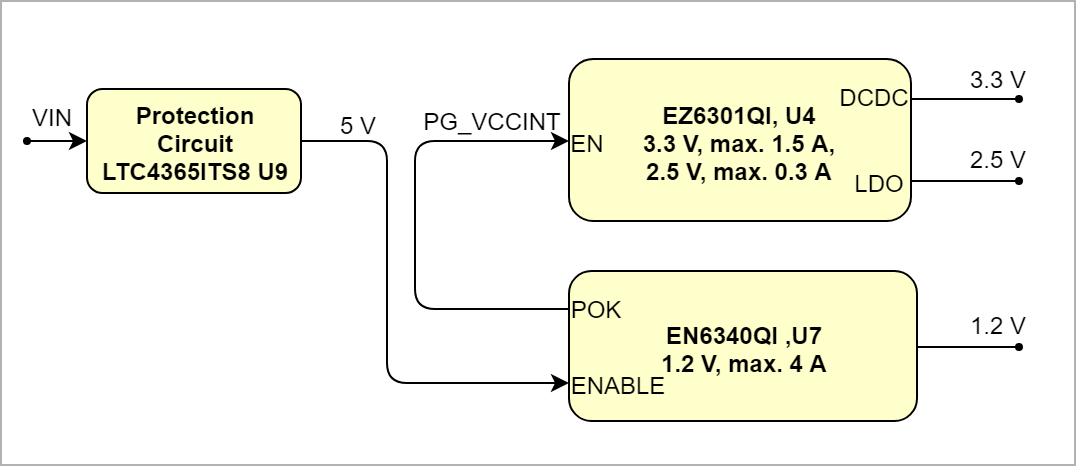

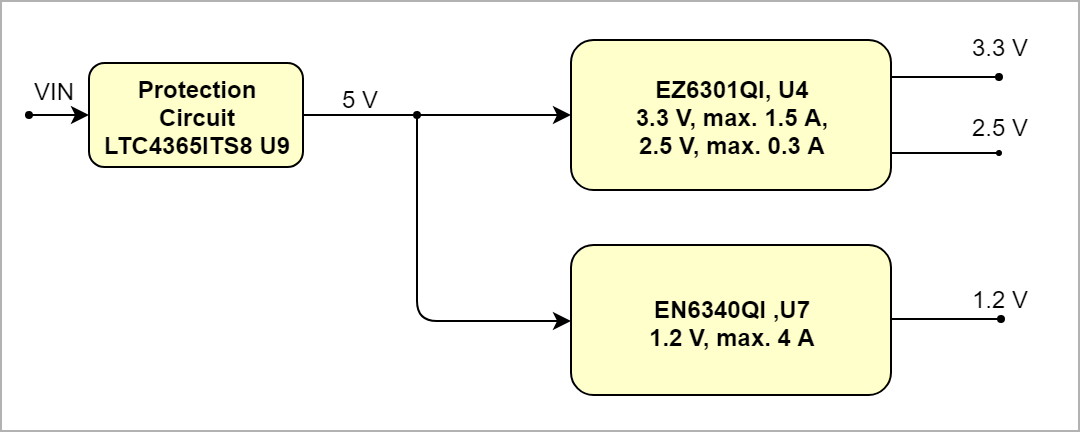

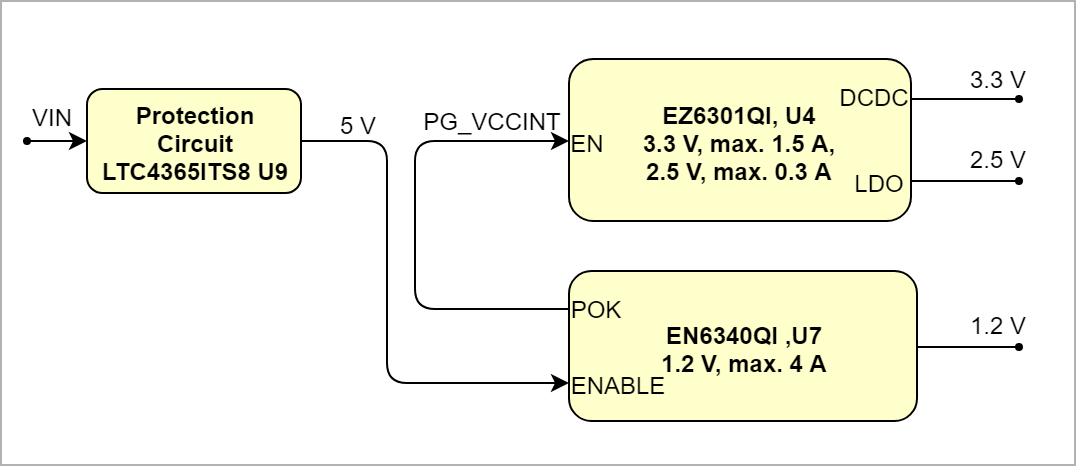

Power Distribution Dependencies

| Scroll Title |

|---|

| anchor | Figure_PWR_PD |

|---|

| title | Power Distribution |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 1 |

|---|

| diagramName | TEI0009_PWR_PD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

|

|

Power-On Sequence

| Scroll Title |

|---|

| anchor | Figure_PWR_PS |

|---|

| title | Power Sequency |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 1 |

|---|

| diagramName | TEI0009_PWR_PS |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

|

|

Voltage Monitor Circuit

| Scroll Title |

|---|

| anchor | Figure_PWR_VMC |

|---|

| title | Voltage Monitor Circuit |

|---|

|

| Scroll Ignore |

|---|

Create DrawIO object here: Attention if you copy from other page, objects are only linked. |

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

|

Power Rails

| Scroll Title |

|---|

| anchor | Table_PWR_PR |

|---|

| title | Module power rails. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Power Rail Name | B2B Connector JM1 Pin | B2B Connector JM2 Pin | B2B Connector JM3 Pin | Direction | Notes |

|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bank Voltages

| Scroll Title |

|---|

| anchor | Table_PWR_BV |

|---|

| title | Zynq SoC bank voltages. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

Technical Specifications

Absolute Maximum Ratings

| Scroll Title |

|---|

| anchor | Table_TS_AMR |

|---|

| title | PS absolute maximum ratings |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Symbols | Description | Min | Max | Unit |

|---|

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

| V |

|

|

|

|

|

|

|

|

|

|

|

Recommended Operating Conditions

Operating temperature range depends also on customer design and cooling solution. Please contact us for options.

| Scroll Title |

|---|

| anchor | Table_TS_ROC |

|---|

| title | Recommended operating conditions. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Parameter | Min | Max | Units | Reference Document |

|---|

|

|

| V | See ???? datasheets. |

|

|

| V | See Xilinx ???? datasheet. |

|

|

| V | See Xilinx ???? datasheet. |

|

|

| V | See Xilinx ???? datasheet. |

|

|

| V | See Xilinx ???? datasheet. |

|

|

| V | See Xilinx ???? datasheet. |

|

|

| V | See Xilinx ???? datasheet. |

|

|

| °C | See Xilinx ???? datasheet. |

|

|

| °C | See Xilinx ???? datasheet. |

|

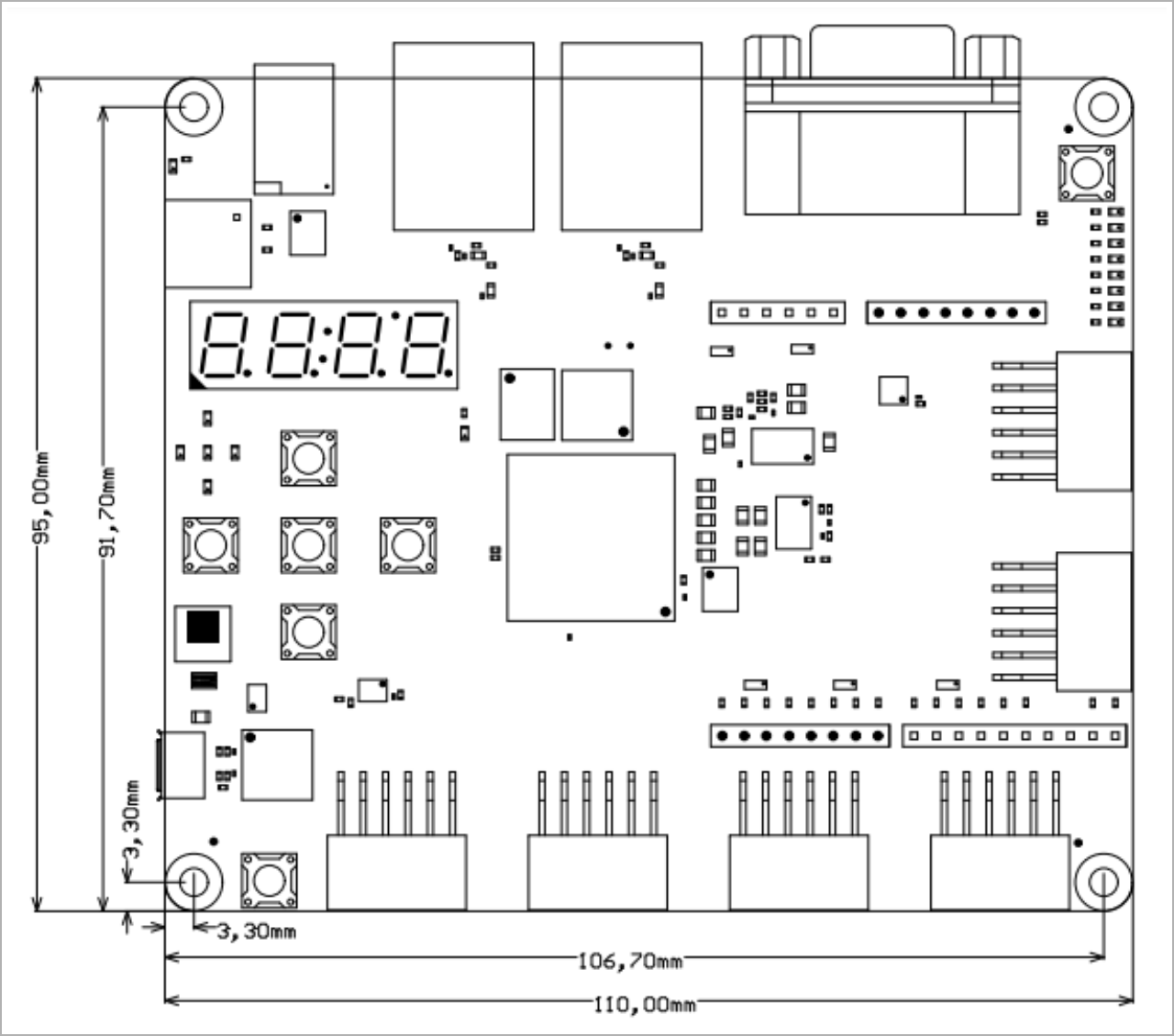

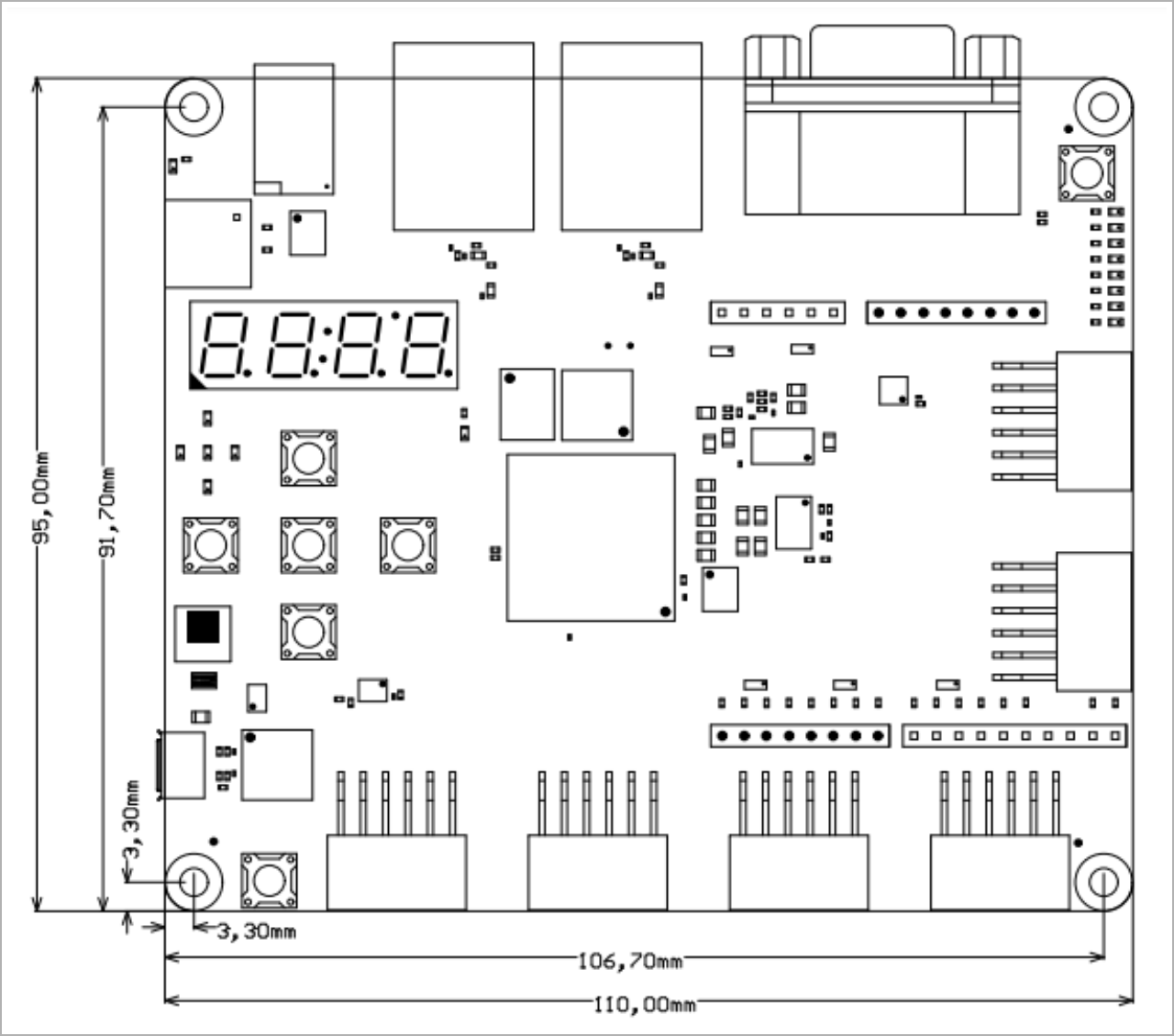

Physical Dimensions

Module size: 95 mm × 110 mm. Please download the assembly diagram for exact numbers.

- PCB thickness: ?? mm.

...

| Scroll Title |

|---|

| anchor | Figure_TS_PD |

|---|

| title | Physical Dimension |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 2 |

|---|

| diagramName | TEI0009_TS_PD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 640 |

|---|

|

|

| Scroll Only |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

|

Currently Offered Variants

| Page properties |

|---|

|

Set correct link to the shop page overview table of the product on English and German. Example for TE0728: ENG Page: https://shop.trenz-electronic.de/en/Products/Trenz-Electronic/TE07XX-Zynq-SoC/TE0728-Zynq-SoC/ DEU Page: https://shop.trenz-electronic.de/de/Produkte/Trenz-Electronic/TE07XX-Zynq-SoC/TE0728-Zynq-SoC/ For Baseboards, where no overview page is available (and revision number is coded in the direct link) use shop search link, e.g. TE0706: ENG Page: https://shop.trenz-electronic.de/en/search?sSearch=TE0706 DEU Page: https://shop.trenz-electronic.de/de/search?sSearch=TE0706 if not available, set. |

...

| Scroll Title |

|---|

| anchor | Table_VCP_SO |

|---|

| title | Trenz Electronic Shop Overview |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

Revision History

Hardware Revision History

...

| Scroll Title |

|---|

| anchor | Figure_RV_HRN |

|---|

| title | Board hardware revision number. |

|---|

|

| Scroll Ignore |

|---|

Create DrawIO object here: Attention if you copy from other page, objects are only linked. |

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

|

Document Change History

| Page properties |

|---|

|

- Note this list must be only updated, if the document is online on public doc!

- It's semi automatically, so do following

Add new row below first Copy "Page Information Macro(date)" Macro-Preview, Metadata Version number, Author Name and description to the empty row. Important Revision number must be the same as the Wiki document revision number Update Metadata = "Page Information Macro (current-version)" Preview+1 and add Author and change description. --> this point is will be deleted on newer pdf export template - Metadata is only used of compatibility of older exports

|

...

| Scroll Title |

|---|

| anchor | Table_RH_DCH |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Contributor | Description |

|---|

| Page info |

|---|

| infoType | Modified date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | -- | all | | Page info |

|---|

| infoType | Modified users |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| |

|

Disclaimer

| Include Page |

|---|

| IN:Legal Notices |

|---|

| IN:Legal Notices |

|---|

|

...