...

The Trenz Electronic CR00140-01 is an module a CRUVI motor driver module. It supports motors with up to 4 phases up to 40V.

Refer to http://trenz.org/tec0850-info for the current online version of this manual and other available documentation.

...

| Page properties |

|---|

|

Note:

'description: Important components and connector or other Features of the module

→ please sort and indicate assembly options Key Features' must be split into 6 main groups for modues: - SoC/FPGA

- Package:

- Speed:

- Temperature:

- RAM/Storage

- On Board

- Interface

- E.g. ETH, USB, B2B, Display port

- Power

- E.g. Input supply voltage

- Dimension

Key Features' must be split into 6 main groups for carrier: - Modules

- TE0808, TE807, TE0803,...

- RAM/Storage

- On Board

- Interface

- E.g. ETH, USB, B2B, Display port

- Power

- E.g. Input supply voltage

- Dimension

|

- Modules/ SoC FPGA

- On Board

- Interface

- Power

- Dimension

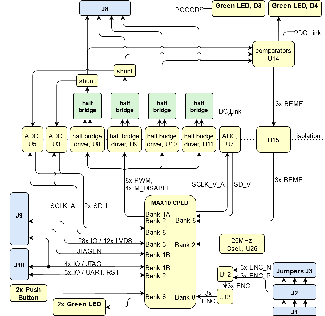

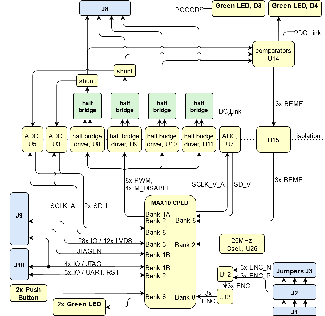

Block Diagram

- 2 phase current measurement

- DC_LINK voltage measurement

- 4x LEDs (2 power indicator, 2 user)

- 2x Pushbutton

- Interface

- 4 phase screw terminal motor connector

- CRUVI for control

- 1x high speed connector

- 1 low speed connector

- 6x1 pin header for single ended sensors

- 5x2 pin header for differential sensors

- Power

- screw terminal for up to 40 V DC motor supply

- Dimension

Block Diagram

| Page properties |

|---|

|

| Page properties |

|---|

|

add drawIO object here.

|

...

| Scroll Title |

|---|

| anchor | Figure_OV_BD |

|---|

| title | TExxxx CR00140 block diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | true |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramName | BD_CR00140 |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| diagramWidth | 650 |

|---|

| revision | 11 |

|---|

|

Create DrawIO object here: Attention if you copy from other page, objects are only linked. |

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed Image Added Image Added |

|

Main Components

| Page properties |

|---|

|

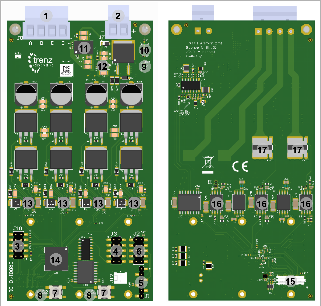

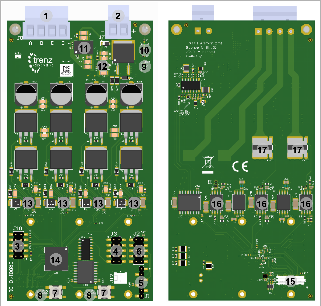

Notes : - Picture of the PCB (top and bottom side) with labels of important components

- Add List below

|

| Scroll Title |

|---|

| Scroll Title |

|---|

| anchor | Figure_OV_MC |

|---|

| title | TExxxx CR00140 main components |

|---|

|

| Scroll Ignore |

|---|

Create DrawIO object here: Attention if you copy from other page, objects are only linked. |

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

|

- ...

- ...

- ...

Initial Delivery State

| Page properties |

|---|

|

Notes : Only components like EEPROM, QSPI flash can be initialized by default at manufacture. If there is no components which might have initial data ( possible on carrier) you must keep the table empty |

...

| anchor | Table_OV_IDS |

|---|

| title | Initial delivery state of programmable devices on the module |

|---|

...

Storage device name

...

Content

...

Notes

...

Quad SPI Flash

...

Configuration Signals

| Page properties |

|---|

|

- Overview of Boot Mode, Reset, Enables.

|

...

| anchor | Table_OV_BP |

|---|

| title | Boot process. |

|---|

...

MODE Signal State

...

| anchor | Table_OV_RST |

|---|

| title | Reset process. |

|---|

...

Signal

...

Signals, Interfaces and Pins

| Page properties |

|---|

|

Notes : - For carrier or stand-alone boards use subsection for every connector type (add designator on description, not on the subsection title), for example:

- For modules which needs carrier use only classes and refer to B2B connector if more than one is used, for example

|

Board to Board (B2B) I/Os

FPGA bank number and number of I/O signals connected to the B2B connector:

...

| anchor | Table_SIP_B2B |

|---|

| title | General PL I/O to B2B connectors information |

|---|

...

JTAG access to the TExxxx SoM through B2B connector JMX.

...

| anchor | Table_SIP_JTG |

|---|

| title | JTAG pins connection |

|---|

...

JTAG Signal

...

B2B Connector

...

MIO Pins

...

you must fill the table below with group of MIOs which are connected to a specific components or peripherals, you do not have to specify pins in B2B, Just mention which B2B is connected to MIOs. The rest is clear in the Schematic.

Example:

| draw.io Diagram |

|---|

| border | true |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramName | MC_CR00140 |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| diagramWidth | 641 |

|---|

| revision | 4 |

|---|

|

|

| Scroll Only |

|---|

Image Added Image Added

|

|

- Motor connector screw terminal, J8

- Power supply screw terminal, J7

- 5x2 pinheader, base for TEI0004 JTAG programmer, J10

- 5x2 pinheader for sensor selection, J3

- 6x1 pinheader for single ended sensors, J1

- 5x2 pinheader for differential sensors, J2

- User push buttons, S1, S2

- User LEDs, D1, D2

- LED DC_Link, D4

- LED Power Good, D3

- DCDC for 15V, U1

- DCDC for 5V, U2

- half bridge drivers, U8, U9, U10, U11

- MAX10 CPLD, U25

- CRUVI high speed connector

- CRUVI low speed connector

- ADCs, U3, U5, U7

- Shunt resistors, R22, R28

Initial Delivery State

...

SPI_CS , SPI_DQ0... SPI_DQ3

SPI_SCK

...

| anchor | Table_OBP_MIOs |

|---|

| title | MIOs pins |

|---|

...

| Page properties |

|---|

|

Notes : - add subsection for every component which is important for design, for example:

- Two 100 Mbit Ethernet Transciever PHY

- USB PHY

- Programmable Clock Generator

- Oscillators

- eMMCs

- RTC

- FTDI

- ...

- DIP-Switches

- Buttons

- LEDs

|

| Page properties |

|---|

|

Notes : In the on-board peripheral table "chip/Interface" must be linked to the corresponding chapter or subsection |

...

| anchor | Table_OBP |

|---|

| title | On board peripherals |

|---|

...

Quad SPI Flash Memory

| Page properties |

|---|

|

Notes :Minimum and Maximum density of quad SPI flash must be mentioned for other assembly options. Only components like EEPROM, QSPI flash can be initialized by default at manufacture. If there is no components which might have initial data ( possible on carrier) you must keep the table empty |

| Scroll Title |

|---|

| anchor | Table_OBPOV_SPIIDS |

|---|

| title | Quad SPI interface MIOs and pinsInitial delivery state of programmable devices on the module |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

| MIO Pin | Schematic | U?? Pin | Notes |

|---|

...

Storage device name | Content | Notes |

|---|

| MAX10 CPLD | default firmware REV01 | See firmware documentation |

|

Signals, Interfaces and Pins

| Page properties |

|---|

|

Notes : - For carrier or stand-alone boards use subsection for every connector type (add designator on description, not on the subsection title), for example:

- For modules which needs carrier use only classes and refer to B2B connector if more than one is used, for example

|

Board to Board (B2B) I/Os

FPGA bank number and number of I/O signals connected to the B2B connector:

| Scroll Title |

|---|

| anchor | Table_OBP_RTC |

|---|

| title | I2C interface MIOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

style | widths | | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

| MIO Pin | Schematic | U? Pin | Notes |

|---|

| Scroll Title |

|---|

| anchor | Table_OBPSIP_I2C_RTCB2B |

|---|

| title | General PL I/O to B2B connectors information | title | I2C Address for RTC |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| CPLD Bank | B2B Connector | I/O Signal Count | Voltage Level |

|---|

MIO Pin | I2C Address | Designator |

...

| anchor | Table_OBP_EEP |

|---|

| title | I2C EEPROM interface MIOs and pins |

|---|

| 3 | J9 | 12 x LVDS / 24 I/Os | VADJ | 6 x RX + 6 x TX | | 3 | J9 | 4 I/Os | VADJ |

| | 8 | J9 | 4 I/Os | 3.3V | Constant 3.3V | | 1B | J9 | 5 I/Os | 3.3V | JTAG, JTAGEN, Constant 3.3V | | 8 | J11 | 8 x I/Os | 3.3V | Constant 3.3V |

|

JTAG Interface

JTAG access to the CPLD of CR00140 is possible via the CRUVI high speed connector J9 or the pinheader J10, which is a base for TEI004 JTAG programmer.

...

| Scroll Title |

|---|

| anchor | Table_OBPSIP_I2C_EEPROMJTG |

|---|

| title | I2C address for EEPROMJTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

| MIO Pin | I2C Address | Designator | Notes |

|---|

LEDs

...

| anchor | Table_OBP_LED |

|---|

| title | On-board LEDs |

|---|

JTAG Signal | B2B Connector | Pin header | Notes |

|---|

| TMS | J9-55 | J10-5 | pull up | | TDI | J9-51 | J10-9 | pull up | | TDO | J9-53 | J10-3 |

| | TCK | J9-59 | J10-1 | pull down | | JTAG_EN | J9-57 | - | pull up |

|

On-board Peripherals

...

| Page properties |

|---|

|

Notes : Minimum and Maximum density of DDR3 SDRAM must be mentioned for other assembly options. (pay attention to supported address length for DDR3) |

The TE???? SoM has ??? GByte volatile DDR3 SDRAM IC for storing user application code and data.

- Part number:

- Supply voltage:

- Speed:

- NOR Flash

- Temperature:

...

- add subsection for every component which is important for design, for example:

- Two 100 Mbit Ethernet Transciever PHY

- USB PHY

- Programmable Clock Generator

- Oscillators

- eMMCs

- RTC

- FTDI

- ...

- DIP-Switches

- Buttons

- LEDs

|

LEDs

| Scroll Title |

|---|

| anchor | Table_OBP_ETHLED |

|---|

| title | Ethernet PHY to Zynq SoC connectionsOn-board LEDs |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Bank| Signal Name | ETH1 | ETH2 | Signal Description | |

CAN Transceiver

...

| anchor | Table_OBP_CAN |

|---|

| title | CAN Tranciever interface MIOs |

|---|

...

| Color | Connected to | Signal name | Active Level | Note |

|---|

| D1 | green | U25-B2 | LED1 | high | User LED, CPLD Firmware dependent, see Firmware description. | | D2 | green | U25-D6 | LED0 | high | User LED, CPLD Firmware dependent, see Firmware description. | | D3 | green | U1-A3, U2-B1 | PGOOD | high | ON when +15.0V_M and +5.0V_M regulator indicated power good. Connected via transistor T1. | | D4 | green | DC_LINK | - | low | ON when DC_LINK above 11.7V. Connected via comparator U14D to DC_LINK |

|

Buttons

...

| Scroll Title |

|---|

| anchor | Table_OBP_CLKLED |

|---|

| title | OsillatorsOn-board LEDs |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Description | Frequency | Note | MHz | MHz | Connected to | Signal name | Active Level | Note |

|---|

| S1 | U25-B10 | BUTTON2 | low | User button, CPLD Firmware dependent, see Firmware description | | S2 | U25-C10 | BUTTON1 | low | User button, CPLD Firmware dependent, see Firmware description | KHz |

|

Power and Power-On Sequence

...