...

| Page properties |

|---|

|

Template Revision 2.4 7 - on construction Design Name always "TE Series Name" + Design name, for example "TE0720 Test Board" |

...

| Scroll Title |

|---|

| anchor | Table_DRH |

|---|

| title | Design Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Vivado | Project Built | Authors | Description |

|---|

| 2020-01-14 | 2019.2 | TE0720-test_board-vivado_2019.2-build_3_20200114090828.zip

TE0720-test_board_noprebuilt-vivado_2019.2-build_3_20200114090837.zip | John Hartfiel | - Vitis script updates (include linux domain and prebuilt linux files for vitis)

- prebuilt binary export on selection guide

| | 2019-12-18 | 2019.2 | TE0720-test_board-vivado_2019.2-build_1_20191218151902.zip

TE0720-test_board_noprebuilt-vivado_2019.2-build_1_20191218152732.zip | John Hartfiel | - 2019.2 update

- Vitis support

| | 2019-03-04 | 2018.3 | TE0720-test_board-vivado_2018.3-build_01_20190304100745.zip

TE0720-test_board_noprebuilt-vivado_2018.3-build_01_20190304100755.zip | John Hartfiel | - update for -1CR version only (256MB DDR3)

| | 2019-02-21 | 2018.3 | TE0720-test_board-vivado_2018.3-build_01_20190221125123.zip

TE0720-test_board_noprebuilt-vivado_2018.3-build_01_20190221125133.zip | John Hartfiel | - TE Script update

- rework of the FSBLs

- some additional Linux features

| | 2018-08-23 | 2018.2 | te0720-test_board-vivado_2018.2-build_03_20180823185142.zip

te0720-test_board_noprebuilt-vivado_2018.2-build_03_20180823185158.zip | John Hartfiel | - DDR setup bugfix for l1if only

| | 2018-08-13 | 2018.2 | te0720-test_board-vivado_2018.2-build_02_20180810162024.zip

te0720-test_board_noprebuilt-vivado_2018.2-build_02_20180810162040.zip | John Hartfiel | - 2018.2 update

- Boart Part Files rework

| | 2018-04-26 | 2017.4 | te0720-test_board-vivado_2017.4-build_07_20180426144351.zip

te0720-test_board_noprebuilt-vivado_2017.4-build_07_20180426144405.zip | John Hartfiel | | | 2018-03-12 | 2017.4 | te0720-test_board_noprebuilt-vivado_2017.4-build_06_20180312152408.zip

te0720-test_board-vivado_2017.4-build_06_20180312152419.zip | John Hartfiel | - add assembly variant

- script update

| | 2018-01-09 | 2017.4 | te0720-test_board_noprebuilt-vivado_2017.4-build_02_20180109121313.zip

te0720-test_board-vivado_2017.4-build_02_20180109121300.zip | John Hartfiel | - no design changes

- set EEPROM MAC with FSBL+u-boot

- FSBL for QSPI Programming

| | 2017-11-27 | 2017.2 | te0720-test_board_noprebuilt-vivado_2017.2-build_05_20171127153028.zip

te0720-test_board-vivado_2017.2-build_05_20171127153006.zip | John Hartfiel | - remove duplicated content

| | 2017-11-20 | 2017.2 | te0720-test_board_noprebuilt-vivado_2017.2-build_05_20171122074701.zip

te0720-test_board-vivado_2017.2-build_05_20171122074646.zip | John Hartfiel | |

|

...

| Scroll Title |

|---|

| anchor | Table_SW |

|---|

| title | Software |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Software | Version | Note |

|---|

| Vitis | 2019.2 | needed, Vivado is included into Vitis installation | | PetaLinux | 2019.2 | needed |

|

...

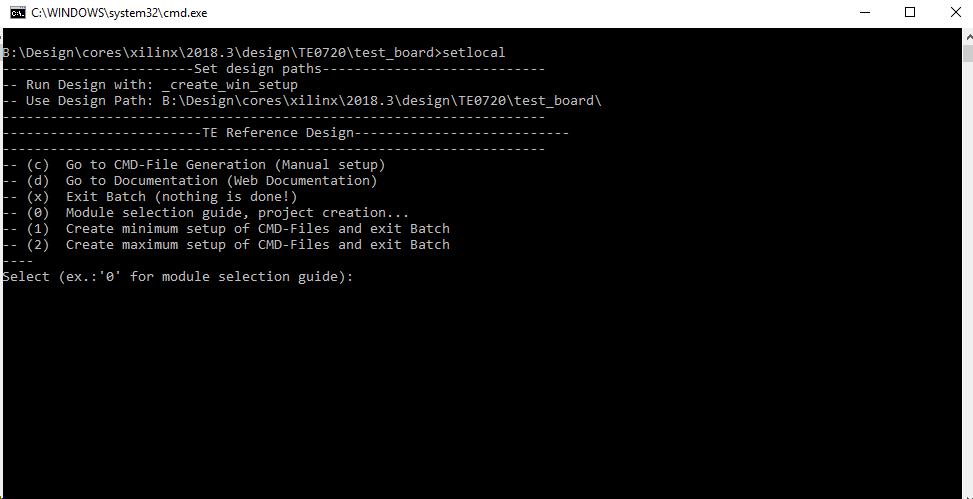

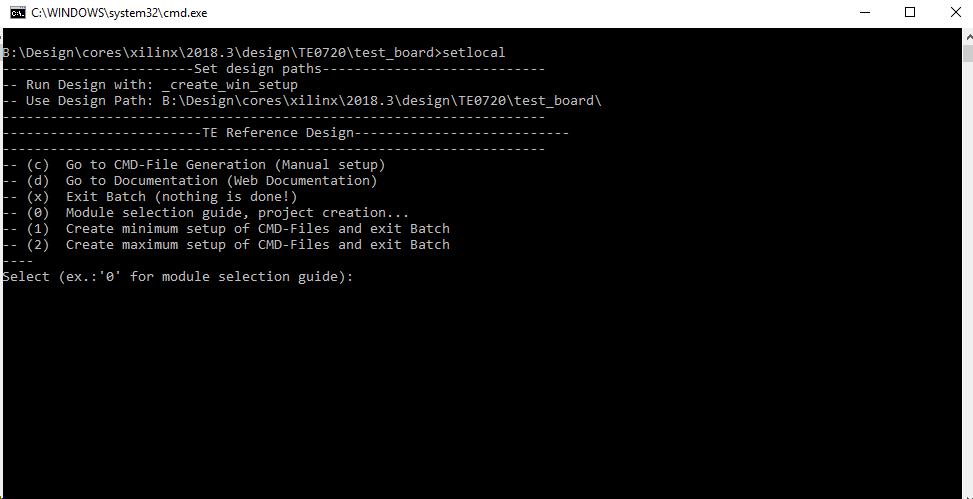

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter to start "Module Selection Guide"

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see also TE Board Part Files

- Create XSA and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Create Linux (uboot.elf and image.ub) with exported XSA

- XSA is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

- Add Linux files (uboot.elf and image.ub) to prebuilt folder

- "prebuilt\os\petalinux\<ddr size>" or "prebuilt\os\petalinux\<short name>"

Notes: Scripts select "prebuilt\os\petalinux\<short name>", if exist, otherwise "prebuilt\os\petalinux\<DDR size>" of the selected device

- Generate Programming Files with Vitis

- Run on Vivado TCL: TE::sw_run_vitis -all

Note: Depending of PC performance this can take several minutes. Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" and open Vitis - (alternative) Start Vitis with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_vitis

Note: TCL scripts generate also platform project, this must be done manuelly in case GUI is used. See Vitis

...

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and DebuggingXilinx Software Programming and Debugging

Get prebuilt boot binaries

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell

- Press 0 and enter to start "Module Selection Guide"

- Select assembly version

- Validate selection

- Select Create and open delivery binary folder

Note: Folder (<project foler>/_binaries_<Artikel Name>) with subfolder (boot_<app name>) for different applications will be generated

QSPI

Optional for Boot.bin on QSPI Flash and image.ub on SD.

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp u-boot

Note: To program with SDK/Vivado GUI, use special FSBL (zynq_fsbl_flash) on setup

optional "TE::pr_program_flash_binfile -swapp hello_te0720" possible - Copy image.ub on SD-Card

- use files from (<project foler>/_binaries_<Articel Name>)/boot_linux from generated binary folder,see: Get prebuilt boot binaries

- or use prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Insert SD-Card

SD

- Copy image.ub and Boot.bin on SD-Card.

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Set Boot Mode to SD-Boot.

- Depends on Carrier, see carrier TRM.

- Insert SD-Card in SD-Slot.

...

| Scroll Title |

|---|

| anchor | Table_dch |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | 2*,*,3*,4* |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Document Revision | Authors | Description |

|---|

| Page info |

|---|

| modified-date |

|---|

| modified-date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

|

| | Page info |

|---|

| current-version |

|---|

| current-version |

|---|

| prefix | v. |

|---|

|

| | Page info |

|---|

| modified-user |

|---|

| modified-user |

|---|

|

| - Vitis script updates (include linux domain and prebuilt linux files for vitis)

- prebuilt binary export on selection guide

| | 2019-12-19 | v.36 | John Hartfiel | | | 2019-12-03 | v.34 | John Hartfiel | | | 2019-10-28 | v.33 | John Hartfiel | - removed remove instructions that are no longer used

| 2019-05-07 | v.31 | John Hartfiel | - Some FSBL notes

- wrong link

| | 2019-03-06 | v.28 | John Hartfiel | - Fixed prebuilt issue for TE0720-03-1CR

| | 2019-03-01 | v.27 | John Hartfiel | - Known issue for TE0720-03-1CR linux design

| | v.26 | John Hartfiel | - 2018.3 release finished (include design reworks)

| | 2018-08-30 | v.25 | John Hartfiel | - update documentation PS configuration

| 2018-08-23 | v.24 | John Hartfiel | | 2018-08-13 | v.23 | John Hartfiel | | 2018-04-26 | v.22 | John Hartfiel | | | 2018-02-20 | v.20 | John Hartfiel | - small documentation update

| | 2018-01-09 | v.16 | John Hartfiel | - Release 2017.4

- Documentation update

| | 2017-11-27 | v.14 | John Hartfiel | - Typo correction

- Design Files update

| | 2017-11-22 | v.12 | John Hartfiel | | | 2017-11-22 | v.11 | John Hartfiel | | | 2017-11-20 | v.1 | | | | -- | All | | Page info |

|---|

| modified-users |

|---|

| modified-users |

|---|

|

| -- |

|

...