...

| Scroll Title |

|---|

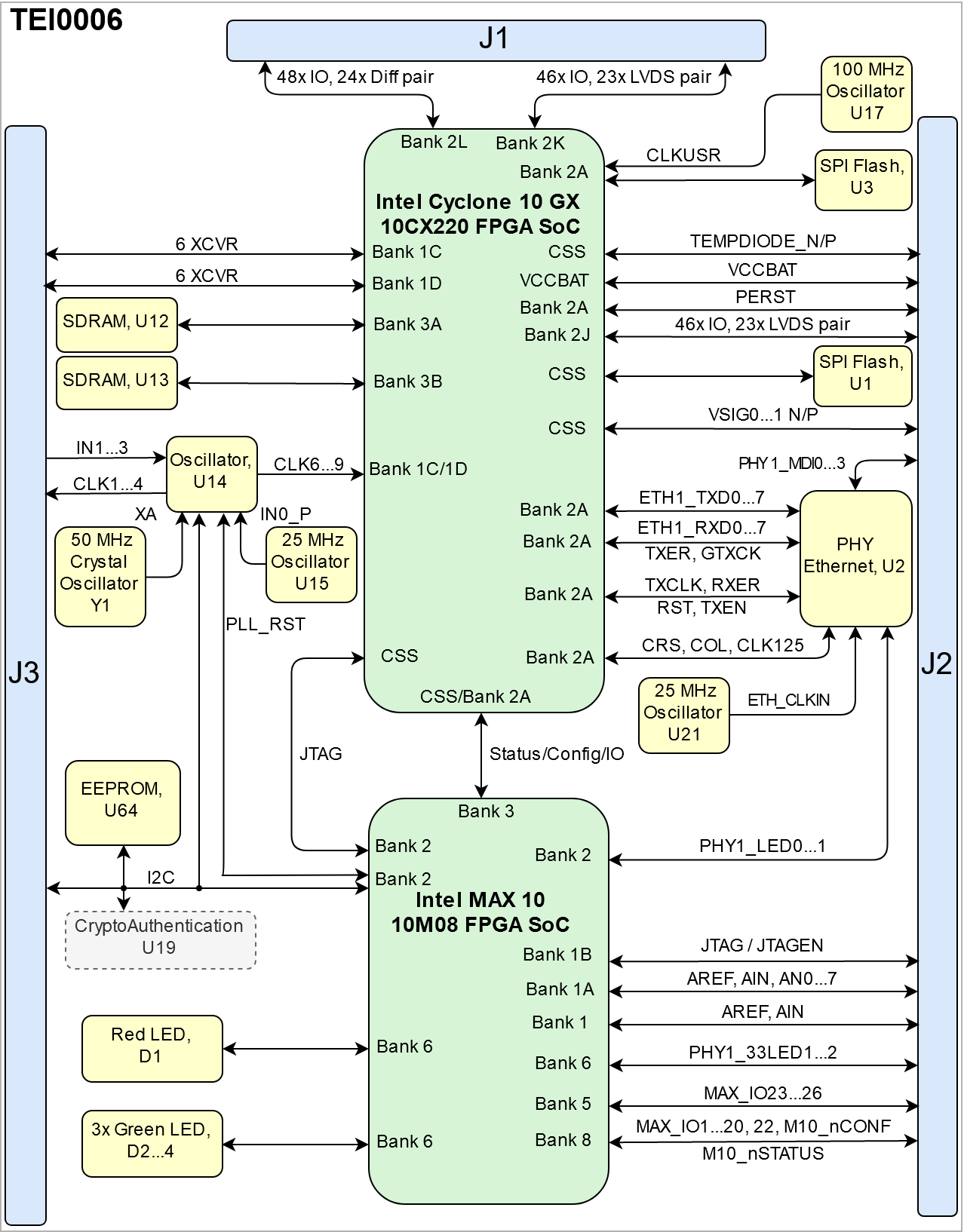

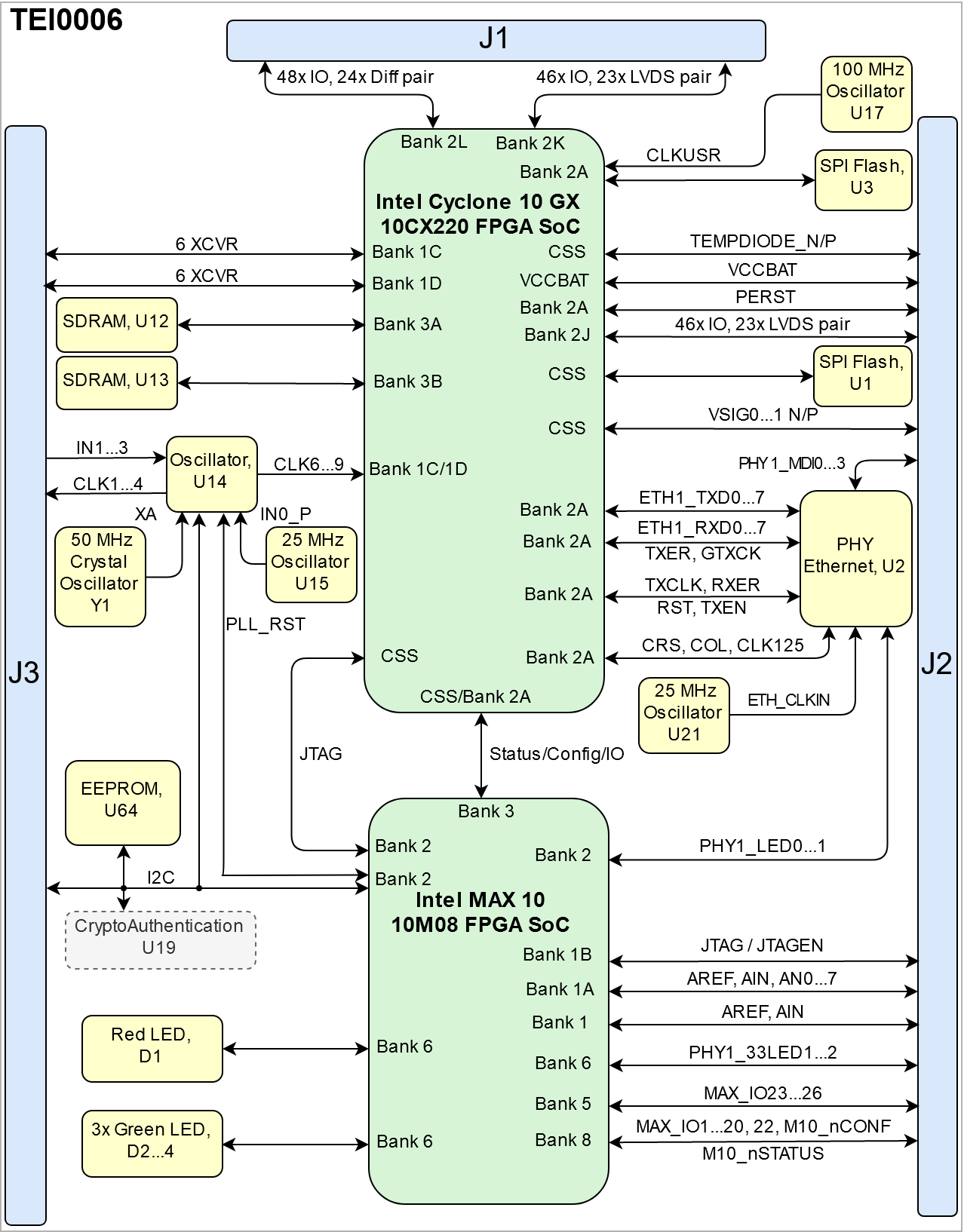

| anchor | Figure_OV_BD |

|---|

| title | TEI0006 block diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramName | TEI0006_OV_BD |

|---|

| simpleViewer | false |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| lbox | true |

|---|

| diagramWidth | 638639 |

|---|

| revision | 2324 |

|---|

|

|

| Scroll Only |

|---|

|

|

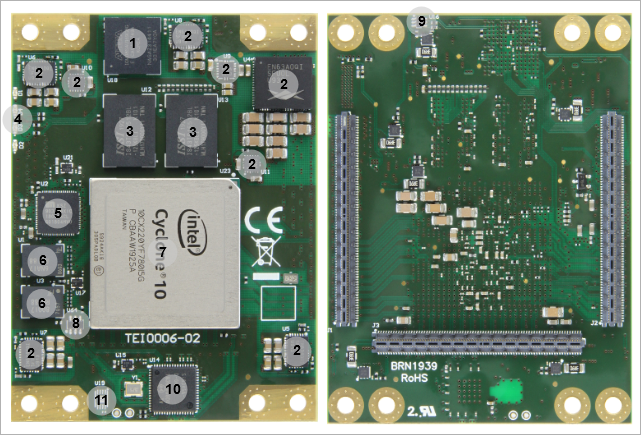

Main Components

...

| Scroll Title |

|---|

| anchor | Figure_OV_BD |

|---|

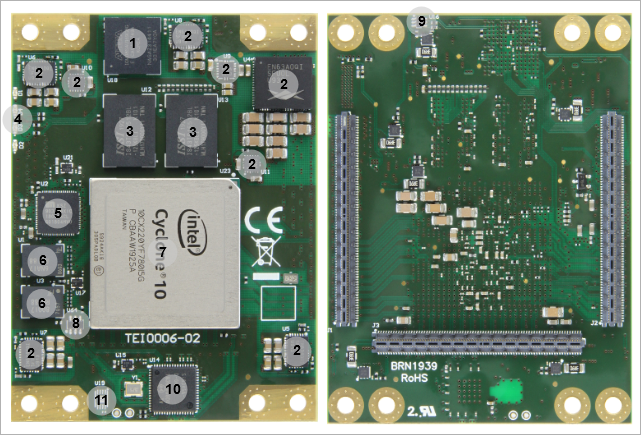

| title | TEI0006 main components |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramName | TEI0006_OV_MC |

|---|

| simpleViewer | false |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 68 |

|---|

|

|

| Scroll Only |

|---|

|

|

- Intel® MAX 10, U18

- DC/DC convertor, U4...11

- SDRAM DDR3 Memory, U12 - U13

- User LEDs, D1...4

- Ethernet Transceiver, U2

- SPI Flash Memory, U1 - U3

- Intel® Cyclone 10 GX, U23

- EEPROM, U64

- Buffer, U16

- 10-Channel Clock Multiplier, U14

- CryptoAuthentication Device (optional), U19

Initial Delivery State

| Page properties |

|---|

|

Notes : Only components like EEPROM, QSPI flash and DDR3 can be initialized by default at manufacture. If there is no components which might have initial data ( possible on carrier) you must keep the table empty |

...

| Scroll Title |

|---|

| anchor | Table_OV_IDS |

|---|

| title | Initial delivery state of programmable devices on the module |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Storage device name | Content | Notes |

|---|

| Intel® MAX 10 | Programmed | See CPLD Firmware | Quad SPI Flash | Not Programmed |

| | EEPROM | Programmed | Ethernet MAC | | DDR3 SDRAM | Not Programmed |

|

|

...

| Scroll Title |

|---|

| anchor | Table_SIP_B2B |

|---|

| title | General PL I/O to B2B connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| FPGA | FPGA Bank | B2B Connector | I/O Signal Count | Voltage Level | Notes |

|---|

Intel Cyclone 10 GX | Bank 1C | J3 | 24 Single ended (12 Diff pair) | 0.95V | GXBL1C_RX0...5 N/P, GXBL1C_TX0...5 N/P | Bank 1D | J3 | 24 Single ended (12 Diff pair) | 0.95V | GXBL1D_RX0...5 N/P, GXBL1D_TX0...5 N/P | Bank 2A | J2 | 2 Single ended | 1.8V | PERST, CLKUSR | Bank 2J | J2 | 46 Single ended (23 Diff pair) | VCCIO2J |

| Bank 2K | J1 | 46 Single ended (23 Diff pair) | VCCIO2K |

| Bank 2L | J1 | 48 Single ended (24 Diff pair) | VADJ up to 3 V |

| Bank 3A | - | - | 1.35V | VDD_DDR | Bank 3B | - | - | 1.35V | VDD_DDR | Intel Max 10 | Bank 1A | J2 | 8 Single ended | 3.3V |

| Bank 1B | J2 | 5 Single ended | 3.3V |

| Bank 2 | J3 | 2 1 Single ended | 1.8VIO |

| Bank 3 | - | - | 1.8VIO |

| Bank 5 | J2 | 4 3 Single ended | 3.3V |

| Bank 6 | J2 | 2 Single ended | 3.3V |

| Bank 8 | J2 | 24 23 Single ended | 3.3V |

|

|

JTAG Interface

JTAG access to the TEI0006 SoM is through B2B connector J2. JTAGEN is pulled up to 3.3V and after power on, JTAG will be enabled.for MAX 10 CPLD is enabled. JTAG port of Cyclon 10 GX device is routed to MAX10 CPLD IOs. The default Firmware connects the JTAG port of the Cyclon 10 GX to the IO pins of the JTAG port in user IO mode. Setting JTAGEN to GND enables JTAG for the Cyclon 10 GX device.

| Scroll Title |

|---|

| anchor | Table_SIP_JTG |

|---|

| title | JTAG pins connection |

|---|

|

| Scroll Title |

|---|

| anchor | Table_SIP_JTG |

|---|

| title | JTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

JTAG Signal | B2B Connector | Note |

|---|

| TMS | J2-160 |

| | TDI | J2-159 |

| | TDO | J2-158 |

| | TCK | J2-157 |

| | JTAGEN | J2-105 | Pulled up to 3.3V. |

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_MIOs |

|---|

| title | MIOs pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| MIO Pin | Connected to | B2B | Notes |

|---|

| MAX_IO1...20, 22 | U18 (Intel MAX 10) - Bank 8 | J2 |

| | MAX_IO23..., 25, 26 | U18 (Intel MAX 10) - Bank 5

| J2 |

|

|

...

| Scroll Title |

|---|

| anchor | Table_OBP |

|---|

| title | On board peripherals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

QSPI Flash Memory

| Page properties |

|---|

|

Notes : Minimum and Maximum density of quad SPI flash must be mentioned for other assembly options. |

...

Clock Sources

The TEI0006 has three crystal oscillator one crystal, three MEMS oscillators and a programmable clock generator.

| Scroll Title |

|---|

| anchor | Table_OBP_CLK |

|---|

| title | Osillators |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Description | Frequency |

|---|

NoteCrystal | MEMS Oscillator | 25MHz | U2 Ethernet | | U15 |

Crystal | MEMS Oscillator | 25MHz | IN0 of U14 | | U17 |

Crystal 48MHz | | 100 MHz | U23, BANK2A USRCLK | | Y1 | Crystal Oscillator | 50MHz | crystal input of U14 | | U14 | Programmable |

U14 | Programmable

|

| Scroll Title |

|---|

| anchor | Table_OBP_CLK_PO |

|---|

| title | Programmable Oscillator connections |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Signals | Clock Type | In/ Out | Connected to | Frequency | Note |

|---|

IN0_P IN0_N | Differential | In In | Oscillator, U15 GND | 25 MHz |

| | IN1..3 | Differential | In | B2B, J3 | Variable |

| XA, XB | Differential |

| Oscillator, U17Y1 GND | 48 50 MHz |

| CLK0 | Differential | Out | Intel Cyclon 10 GX (U23)- Bank 2A | User | Default off | CLK1...4 | Differential | Out | B2B, J3 | User | Default off | | REFCLK_EMIFP | Differential | Out | Intel Cyclon 10 GX (U23)- Bank 3B | User | Default off | | CLK6...7 | Differential | Out | Intel Cyclon 10 GX (U23)- Bank 1D | User | Default off | | CLK8...9 | Differential | Out | Intel Cyclon 10 GX (U23)- Bank 1C | User | Default off | - Bank 1C | User | Default off |

|

CryptoAuthentication

ATECC608A (U19) is a CryptoAuthentication device connected to the I2C bus. This chip is optional, for further description see datasheet of manufacturer.

| Scroll Title |

|---|

| anchor | Table_OBP_EEP |

|---|

| title | I2C Interface of CryptoAuthentication |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Schematic | U19 Pin | B2B | U18 Intel Max 10 Pin | Notes |

|---|

| I2C_SCL | SCL | J3-135 | Bank 2 - K2 | - | | I2C_SDA | SDA | J3-137 | Bank 2 - L2 | - |

|

Power and Power-On Sequence

...

| Scroll Title |

|---|

| anchor | Table_RH_HRH |

|---|

| title | Hardware Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Changes | Documentation Link |

|---|

| 2019-09-11 | 02 | - added 100MHz MEMS oscillator, remove CLKUSR signal from J2

- replaced U21/U15 by SiT8008

- added pull-up to M10_NSTATUS signal

- added pull-up to M10_DEVCLRN, removed signal from J2

- added optional CryptoAuthentication chip U19

| REV02 | | 2018-08-10 | 01 | - | REV01 |

|

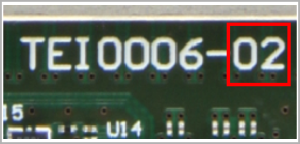

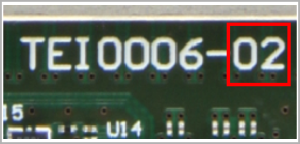

Hardware revision number can be found on the PCB board together with the module model number separated by the dash.

| Scroll Title |

|---|

| anchor | Figure_RV_HRN |

|---|

| title | Board hardware revision number. |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | true |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramName | TEI0006_RV_RHN |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| diagramWidth | 197178 |

|---|

| revision | 13 |

|---|

|

|

| Scroll Only |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

|

...

| Scroll Title |

|---|

| anchor | Table_RH_DCH |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Contributor | Description |

|---|

| Page info |

|---|

| infoType | Modified date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| | 2019-06-14 | v.80 | Pedram Babakhani | Figures updated - Technical specifications updated

| | v.69 | Pedram Babakhani | | -- | all | | Page info |

|---|

| infoType | Modified users |

|---|

| type | Flat |

|---|

| showVersions | false |

|---|

|

| |

|

...