...

| Scroll Title |

|---|

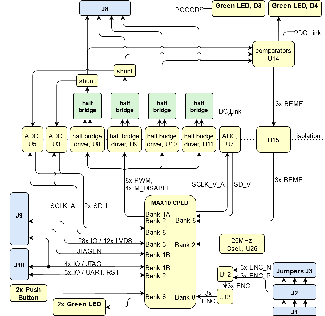

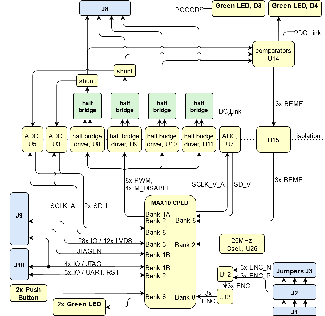

| anchor | Figure_OV_BD |

|---|

| title | CR00140 block diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | false |

|---|

| revision | 1516 |

|---|

| diagramName | BD_CR00140 |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | top |

|---|

| diagramWidth | 650 |

|---|

|

|

| Scroll Only |

|---|

|

|

...

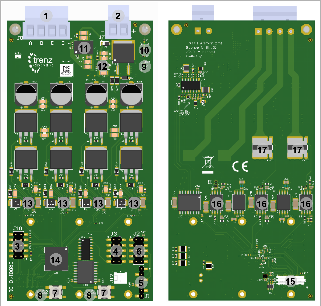

| Scroll Title |

|---|

| anchor | Figure_OV_MC |

|---|

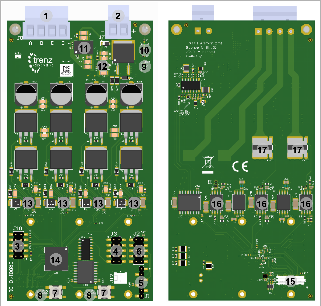

| title | CR00140 main components |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | false |

|---|

| revision | 56 |

|---|

| diagramName | MC_CR00140 |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | top |

|---|

| diagramWidth | 637641 |

|---|

|

|

| Scroll Only |

|---|

|

|

- Motor connector screw terminal, J8

- Power supply screw terminal, J7

- 5x2 pinheader, base for TEI0004 JTAG programmer, J10

- 5x2 pinheader for sensor selection, J3

- 6x1 pinheader for single ended sensors, J1

- 5x2 pinheader for differential sensors, J2

- User push buttons, S1, S2

- User LEDs, D1, D2

- LED DC_Link, D4

- LED Power Good, D3

- DCDC for 15V, U1

- DCDC for 5V, U2

- half bridge drivers, U8, U9, U10, U11

- MAX10 CPLD, U25

- CRUVI high speed connectorCRUVI low speed connector

- ADCs, U3, U5, U7

- Shunt resistors, R22, R28

...

| Scroll Title |

|---|

| anchor | Table_SIP_B2B |

|---|

| title | General PL I/O to B2B connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| CPLD Bank | B2B Connector | I/O Signal Count | Voltage Level | Notes |

|---|

| 3 | J9 | 12 x LVDS / 24 I/Os | VADJ | 6 x RX + 6 x TX | | 3 | J9 | 4 I/Os | VADJ |

| | 8 | J9 | 4 I/Os | 3.3V | Constant 3.3V | | 1B | J9 | 5 I/Os | 3.3V | JTAG, JTAGEN, Constant 3.3V | | 8 | J11 | 8 x I/Os | 3.3V | Constant 3.3V |

|

JTAG Interface

JTAG access to the CPLD of CR00140 is possible via the CRUVI high speed connector J9 and the pinheader J10, which is a base for TEI004 JTAG programmer. The JTAGEN signal is pulled up and available on J9 only. If JTAGEN is pulled low, the four signals can be used as user I/Os.

...

For the connection to a control unit, the CRUVI interface is implemented. One high speed connector J9 and one low speed connector J11 are is assembled. The connectors are further described in section B2B Connectors. The connection of the signals and the voltage levels is described in the CPLD section.

| Scroll Title |

|---|

| anchor | Table_SIP_CRUVI |

|---|

| title | CRUVI signals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Signal | Connector - Pin |

|---|

X0 | J11-3 | | X1 | J11-5 | | X2 | J11-7 | X3 | J11-9 | | X4 | J11-4 | | X5 | J11-10 | | X6 | J11-1 | | X7 | J11-2 | | DGND | J9-12, J9-18, J9-24, J9-30, J9-42, J9-48, J9- | DGND | J11-6, J9-12, J9-18, J9-24, J9-30, J9-42, J9-48, J9-54, J9-13, J9-19, J9-25, J9-31, J9-37, J9-43, J9-49 | +3.3V_D | J11-8, J9-4, J9-9 | | +5.0V_D | J11-12, J9-60 | | VADJ | J9-36 | | A0_P | J9-14 | | A0_N | J9-16 | | A1_P | J9-20 | | A1_N | J9-22 | | A2_P | J9-26 | | A2_N | J9-28 | | A3_P | J9-32 | | A3_N | J9-34 | | A4_P | J9-38 | | A4_N | J9-40 | | A5_P | J9-44 | | A5_N | J9-46 | | B0_P | J9-15 | | B0_N | J9-17 | | B1_P | J9-21 | | B1_N | J9-23 | | B2_P | J9-27 | | B2_N | J9-29 | | B3_P | J9-33 | | B3_N | J9-35 | | B4_P | J9-398 | | B4_N | J9-41 | | B5_P | J9-45 | | B5_N | J9-47 | | HSIO | J9-2 | | HSO | J9-6 | | RESET | J9-8 | | HSI | J9-10 | TDI | J9-51 | | TDO | J9-53 | | TMS | J9-55 | | JTAGEN | J9-57 | | TCK | J9-59 | | SMB_ALERT | J9-3 | | SMB_SDA | J9-5 | | SMB_SCL | J9-7 | | REFCLK | J9-11 |

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_LED |

|---|

| title | On-board LEDs | | On-board LEDs |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Signal name | SC CPLD Pin | CPLD Bank | Connected to | Function | Notes |

|---|

| Scroll Table Layout |

|---|

|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

style | widths | | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

| Signal name | SC CPLD Pin | CPLD Bank | Connected to | Function | Notes |

|---|

X0 | B9 | 8 | J11-3 | CPLD firmware dependent | See CPLD Firmware |

| X1 | A8 | 8 | J11-5 | CPLD firmware dependent | See CPLD Firmware |

| X2 | A7 | 8 | J11-7 | CPLD firmware dependent | See CPLD Firmware |

X3 | A6 | 8 | J11-9 | CPLD firmware dependent | See CPLD Firmware |

| X4 | D8 | 8 | J11-4 | CPLD firmware dependent | See CPLD Firmware |

| X5 | B6 | 8 | J11-10 | CPLD firmware dependent | See CPLD Firmware |

| X6 | C9 | 8 | J11-1 | CPLD firmware dependent | See CPLD Firmware |

| X7 | E8 | 8 | J11-2 | CPLD firmware dependent | See CPLD Firmware |

|---|

| A0_P | J8 | 3 | J9-14 | CPLD firmware dependent | See CPLD Firmware |

| A0_N | K8 | 3 | J9-16 | CPLD firmware dependent | See CPLD Firmware |

| A1_P | M13 | 3 | J9-20 | CPLD firmware dependent | See CPLD Firmware |

| A1_N | M12 | 3 | J9-22 | CPLD firmware dependent | See CPLD Firmware |

| A2_P | M9 | 3 | J9-26 | CPLD firmware dependent | See CPLD Firmware |

| A2_N | M8 | 3 | J9-28 | CPLD firmware dependent | See CPLD Firmware |

| A3_P | N8 | 3 | J9-32 | CPLD firmware dependent | See CPLD Firmware |

| A3_N | N7 | 3 | J9-34 | CPLD firmware dependent | See CPLD Firmware |

| A4_P | M7 | 3 | J9-38 | CPLD firmware dependent | See CPLD Firmware |

| A4_N | N6 | 3 | J9-40 | CPLD firmware dependent | See CPLD Firmware |

| A5_P | K5 | 3 | J9-44 | CPLD firmware dependent | See CPLD Firmware |

| A5_N | J5 | 3 | J9-46 | CPLD firmware dependent | See CPLD Firmware |

| B0_P | N5 | 3 | J9-15 | CPLD firmware dependent | See CPLD Firmware |

| B0_N | N4 | 3 | J9-17 | CPLD firmware dependent | See CPLD Firmware |

| B1_P | J7 | 3 | J9-21 | CPLD firmware dependent | See CPLD Firmware |

| B1_N | K7 | 3 | J9-23 | CPLD firmware dependent | See CPLD Firmware |

| B2_P | L11 | 3 | J9-27 | CPLD firmware dependent | See CPLD Firmware |

| B2_N | M11 | 3 | J9-29 | CPLD firmware dependent | See CPLD Firmware |

| B3_P | L10 | 3 | J9-33 | CPLD firmware dependent | See CPLD Firmware |

| B3_N | M10 | 3 | J9-35 | CPLD firmware dependent | See CPLD Firmware |

| B4_P | J6 | 3 | J9-398 | CPLD firmware dependent | See CPLD Firmware |

| B4_N | K6 | 3 | J9-41 | CPLD firmware dependent | See CPLD Firmware |

| B5_P | L5 | 3 | J9-45 | CPLD firmware dependent | See CPLD Firmware |

| B5_N | L4 | 3 | J9-47 | CPLD firmware dependent | See CPLD Firmware |

| HSIO | N9 | 3 | J9-2 | CPLD firmware dependent | See CPLD Firmware |

| HSO | N10 | 3 | J9-6 | CPLD firmware dependent | See CPLD Firmware |

| RESET | M5 | 3 | J9-8 | CPLD firmware dependent | See CPLD Firmware |

| HSI | N12 | 3 | J9-10 | CPLD firmware dependent | See CPLD Firmware |

TDI | F5 | 1B | J9-51, J10-9 | JTAG / user IO CPLD firmware dependent | See CPLD Firmware |

| TDO | F6 | 1B | J9-53, J10-3 | JTAG / user IO CPLD firmware dependent | See CPLD Firmware |

| TMS | G1 | 1B | J9-55, J10-5 | JTAG / user IO CPLD firmware dependent | See CPLD Firmware |

| JTAGEN | E5 | 1B | J9-57 | JTAG enable CPLD firmware dependent | See CPLD Firmware |

| TCK | G2 | 1B | J9-59, J10-1 | JTAG / user IO CPLD firmware dependent | See CPLD Firmware |

| SMB_ALERT | K2 | 2 | J9-3 | CPLD firmware dependent | See CPLD Firmware |

| SMB_SDA | H5 | 2 | J9-5 | CPLD firmware dependent | See CPLD Firmware |

| SMB_SCL | H4 | 2 | J9-7 | CPLD firmware dependent | See CPLD Firmware |

| REFCLK | M2 | 2 | J9-11 | CPLD firmware dependent | See CPLD Firmware |

| BUTTON1 | C10 | 8 | S2 | CPLD firmware dependent | activ low, See CPLD Firmware |

| BUTTON2 | B10 | 8 | S1 | CPLD firmware dependent | activ low, See CPLD Firmware |

| ENC_A | A10 | 8 | U13-13 | Sensor input channel A | - |

| ENC_B | A9 | 8 | U13-12 | Sensor input channel B | - |

| ENC_I | A11 | 8 | U13-14 | Sensor input channel I | - |

| LED0 | D6 | 8 | D2 | CPLD firmware dependent | See CPLD Firmware |

| LED1 | B2 | 8 | D1 | CPLD firmware dependent | See CPLD Firmware |

| M_BEMF_B_D | B5 | 8 | U15-13 | Back EMF signal phase B | - |

| M_BEMF_C_D | A5 | 8 | U15-12 | Back EMF signal phase C | - |

| M_BEMF_A_D | A4 | 8 | U15-14 | Back EMF signal phase A | - |

| M_PWM_AH | F1 | 1A | U8-2 | Phase A half bridge high (DC_LINK) side driver signal | - |

| M_PWM_AL | E3 | 1A | U8-3 | Phase A half bridge low (PGND) side driver signal | - |

| M_PWM_BH | E1 | 1A | U9-2 | Phase B half bridge high (DC_LINK)side driver signal | - |

| M_PWM_BL | D1 | 1A | U9-3 | Phase B half bridge low (PGND) side driver signal | - |

| M_PWM_CH | E4 | 1A | U10-2 | Phase C half bridge high (DC_LINK)side driver signal | - |

| M_PWM_CL | C1 | 1A | U10-3 | Phase C half bridge low (PGND) side driver signal | - |

| M_PWM_DH | C2 | 1A | U11-2 | Phase D half bridge high (DC_LINK) side driver signal | - |

| M_PWM_DL | B1 | 1A | U11-3 | Phase D half bridge low (PGND) side driver signal | - |

| SD_IA | E6 | 8 | U3-6 | Current measurement phase A | 33 Ohm series Resistor |

| SCLK_A | B3 | 8 | U3-7, U5-7 | Clock for ADC for current measurement phase A and B | (5-20 MHz) |

| SD_V | B4 | 8 | U7-6 | Voltage measurement DC_LINK | 33 Ohm series Resistor |

| SD_IB | A2 | 8 | U5-6 | Current measurement phase B | 33 Ohm series Resistor |

| SCLK_V_A | A3 | 8 | U7-7 | Clock for ADC for voltage measurement DC_LINK | (5-20 MHz) |

| M_DISABLE_D_D | J1 | 2 | U11-5 | Halfe bridge disable phase D | disabled when high, pull up connected |

| M_DISABLE_A_D | M1 | 2 | U8-5 | Halfe bridge disable phase A | disabled when high, pull up connected |

| M_DISABLE_B_D | L2 | 2 | U9-5 | Halfe bridge disable phase B | disabled when high, pull up connected |

| M_DISABLE_C_D | K1 | 2 | U10-5 | Halfe bridge disable phase C | disabled when high, pull up connected |

| REFCLK | M2 | 2 | J9-11 | CPLD firmware dependent | - |

| RST | M3 | 2 | J10-6 | CPLD firmware dependent | - |

| UART_RX | N2 | 2 | J10-7 | CPLD firmware dependent | - |

| UART_TX | N3 | 2 | J10-8 | CPLD firmware dependent | - |

| CLK_25MHZ | H6 | 2 | U26-3 | Clock input for accurate 25 Mhz clk. | - |

...

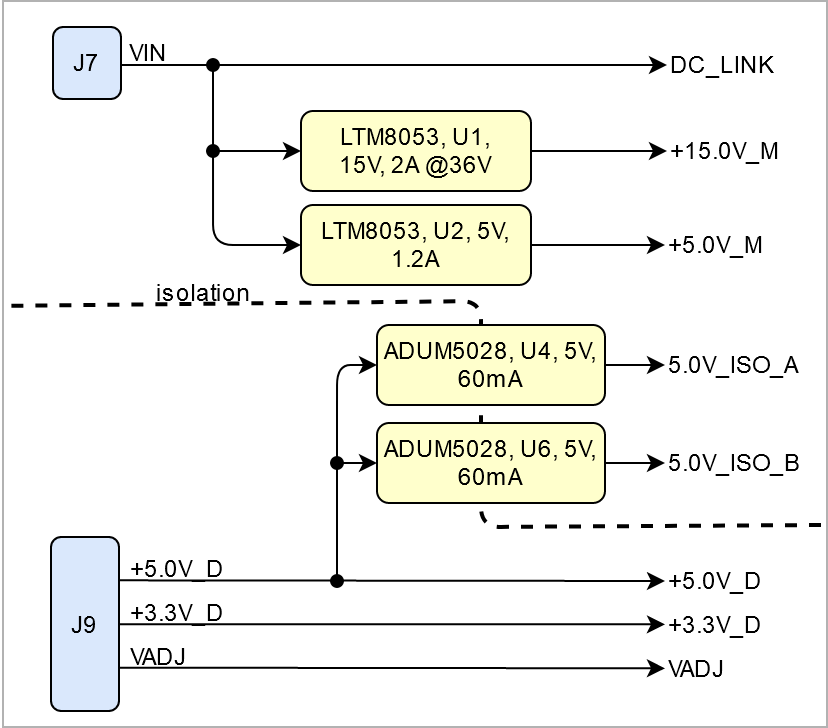

| Scroll Title |

|---|

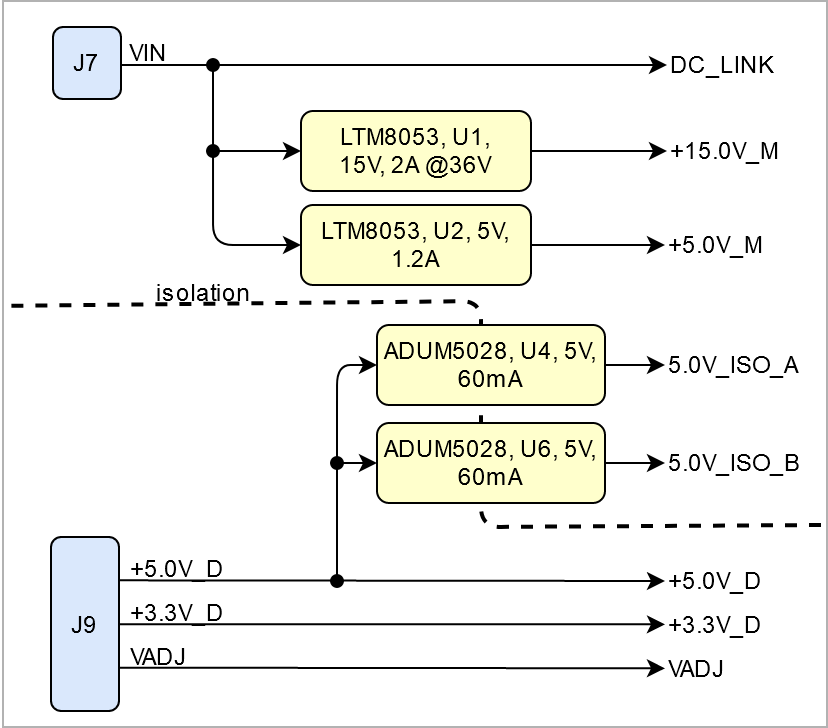

| anchor | Figure_PWR_PD |

|---|

| title | Power Distribution |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | false |

|---|

| revision | 910 |

|---|

| diagramName | PD_CR00140 |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | top |

|---|

| diagramWidth | 412414 |

|---|

|

|

| Scroll Only |

|---|

|

|

Power-On Sequence

...

| Scroll Title |

|---|

| anchor | Table_PWR_PR |

|---|

| title | Module power rails. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Power Rail Name | B2B Connectors

| Direction | Notes |

|---|

+3.3V_D | J11 J9-8, J9-4, J9-9 | In | - | | +5.0V_D | J11-12, J9-60 | In | - | | VADJ | J9-36 | In | - | | VIN | J7 | In | isolated |

|

...