Page History

Template Revision 2.1 - on construction

...

| HTML |

|---|

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

...

| hidden | true |

|---|---|

| id | Comments |

Important General Note:

...

Export PDF to download, if vivado revision is changed!

Designate all graphics and pictures with a number and a description, Use "Scroll Title" macro

...

Figure template (note: inner scroll ignore/only only with drawIO object):

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

|

...

Table template:

- Layout macro can be use for landscape of large tables

- Set column width manually(can be used for small tables to fit over whole page) or leave empty (automatically)

...

| anchor | Table_xyz |

|---|---|

| title | Text |

...

| Scroll pdf ignore | ||||

|---|---|---|---|---|

Table of contents

|

Overview

...

Notes :

short description of the design

Short Link of "Scroll only" macro:

Use short link the Wiki Resource page, for example: http://trenz.org/te0720-info

List of available short links: https://wiki.trenz-electronic.de/display/CON/Redirects

TEF1001 SI5338 Configuration, DDR Configuration and PCIe Core Example Design.

Refer to http://trenz.org/tef1001-info for the current online version of this manual and other available documentation.

Key Features

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Excerpt |

|---|

|

Revision History

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| anchor | Table_DRH |

|---|---|

| title | Design Revision History |

...

- Add -410 assembly variant

- Add some notes on Board part Files (summary window description)

...

- 2018.2

- add TEF1001-02

- MIG Configuration for AW12P7218BLK0M (4GB for REV01)

- MIG Configuration for AW24P7228BLK0M (8GB for REV02)

- BUGFIX QSPI IP configuration

- add SREC to load application into DDR

...

- 2017.4 update

- new assembly variant

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

Design supports following carriers:

...

| anchor | Table_HWC |

|---|---|

| title | Hardware Carrier |

...

...

- DDR configured for AW24P7228BLK0M (8GB for REV02)

...

- DDR configured for AW24P7228BLK0M (8GB for REV02)

* PCB REV01 DDR3 ECC SODIMM is limited to 4GB, for PCB REV02 up to 8GB is possible

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

SREC-File

...

*.srec

...

Converted Software Application for MicroBlaze Processor Systems

...

...

...

...

...

...

...

...

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

...

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

...

- Start with TE Scripts on Vivado TCL: TE::sw_run_hsi

(optional) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk to generate files manually

Note: See SDK Projects - (optional )Copy "prebuilt\software\<short dir>\srec_spi_bootloader.elf" into "\firmware\microblaze_0" (replace shipped one) and regenerate design again (HW (Step5)+SW(Step6 only a.))

Launch

Programming

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

QSPI

- Connect JTAG and Power ON PC

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp hello_tef1001

- Reboot PC

SD

Not supported.

JTAG

- Connect Vivado HW Manager and program FPGA

Note: PCIe enumeration will be not done in this case. SREC Bootloader need Hello TEF1001 application on QSPI Flash for output

Usage

- Prepare HW like described on section Programming

- Power On PCB

Note: 1. FPGA Load Bitfile into FPGA, modified SREC Bootloader configure SI5338 and load application from QSPI into DDR (Depends on linker script)

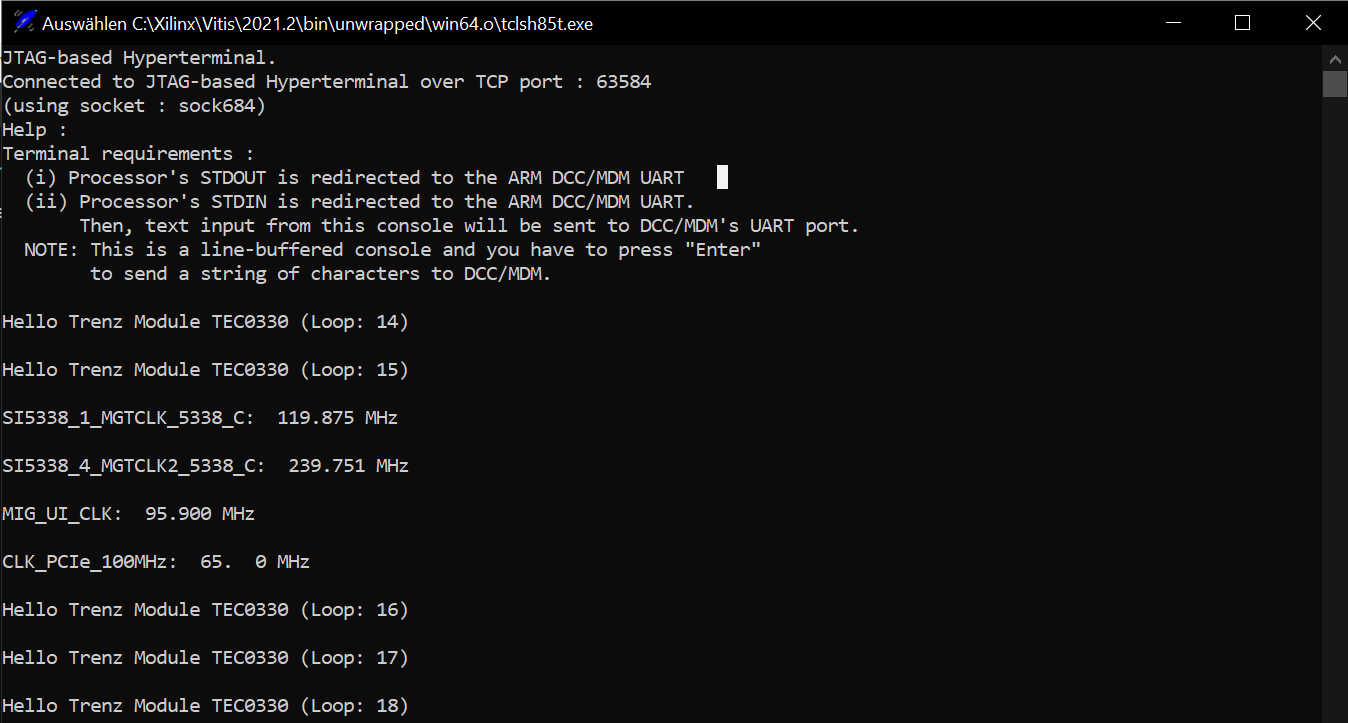

JTAG/UART Console:

- Launch the XSDB console on SDK (Xilinx → XSCT Console):

- type: connect

- type: targets -set -filter {name =~ "MicroBlaze Debug*"} -index 0

- type: jtagterminal -start

- Separat console starts:

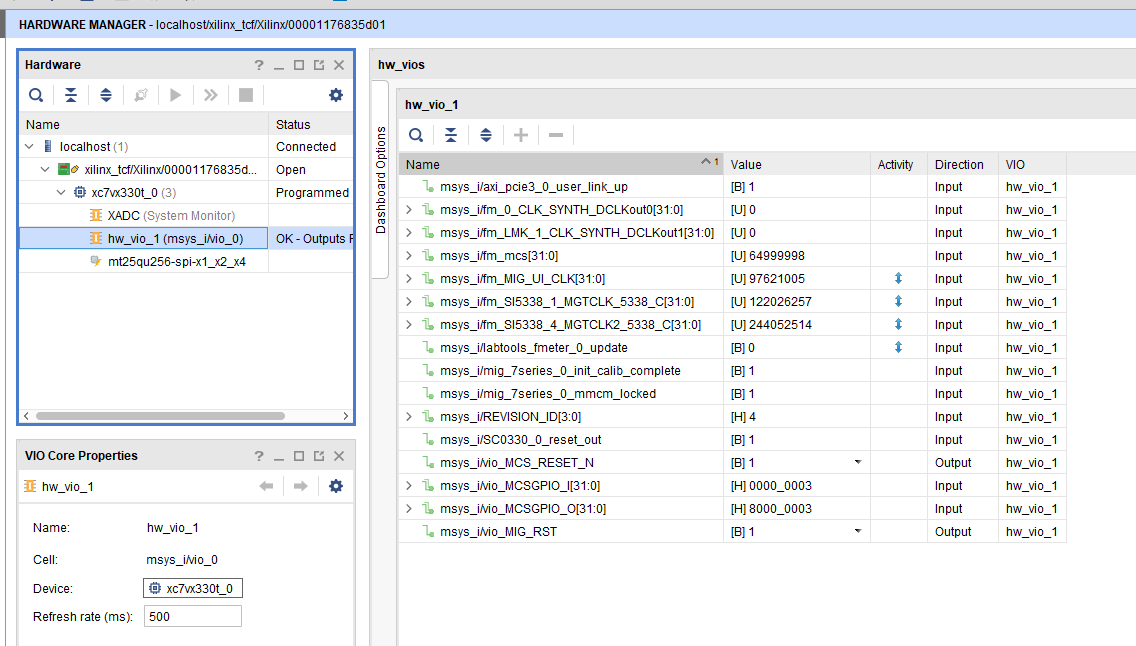

Vivado HW Manager:

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

- Open Vivado HW Manager

- Add VIO to Dashboard:

- Set Radix to unsigned integer for FMeterCLKs (labt_SI_*)

- Control:

- USER LEDs are selectable

Note USR_CPLD_LED on PCB REV1 and REV02, USR_LED Matrix only on REV02 - Optional PCIe Core Reset (on FPGA only)

- Optional System Reset (on FPGA only)

- USER LEDs are selectable

- Read: All SI5338 CLKs (Unit Hz), PCIe Cor MMCM Lock signal, MIG MMCM Lock signal, MIG Init Calibration Done

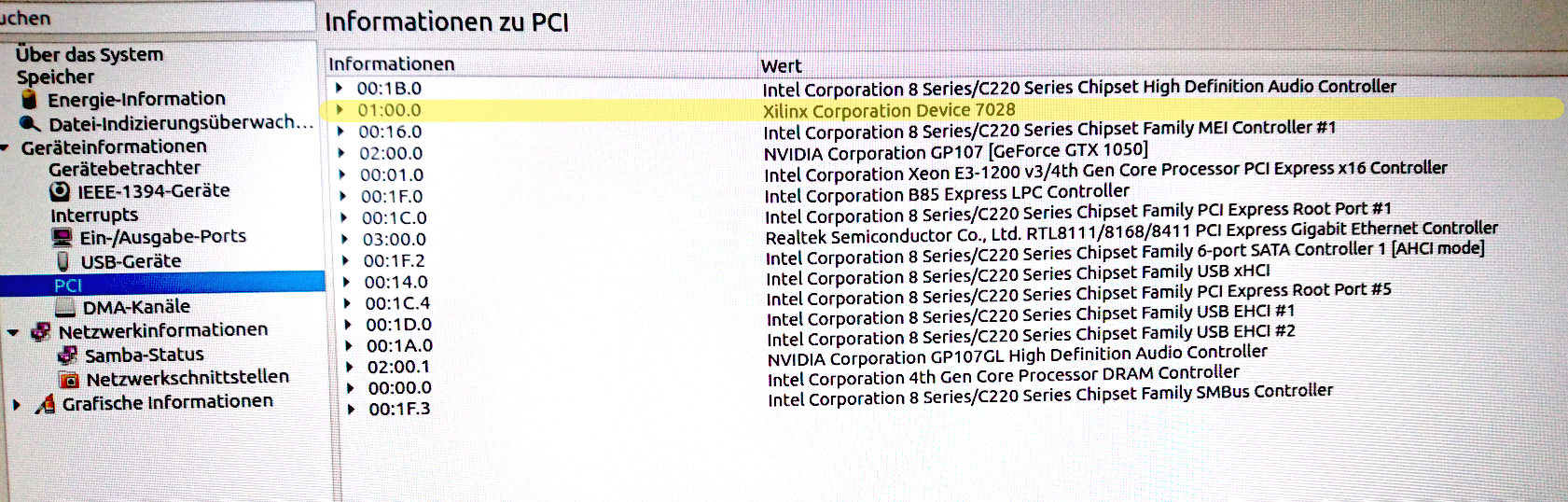

PC:

- Use for example PCI-Z (Win) or KInfoCenter (Linux) to detect PCIe Card

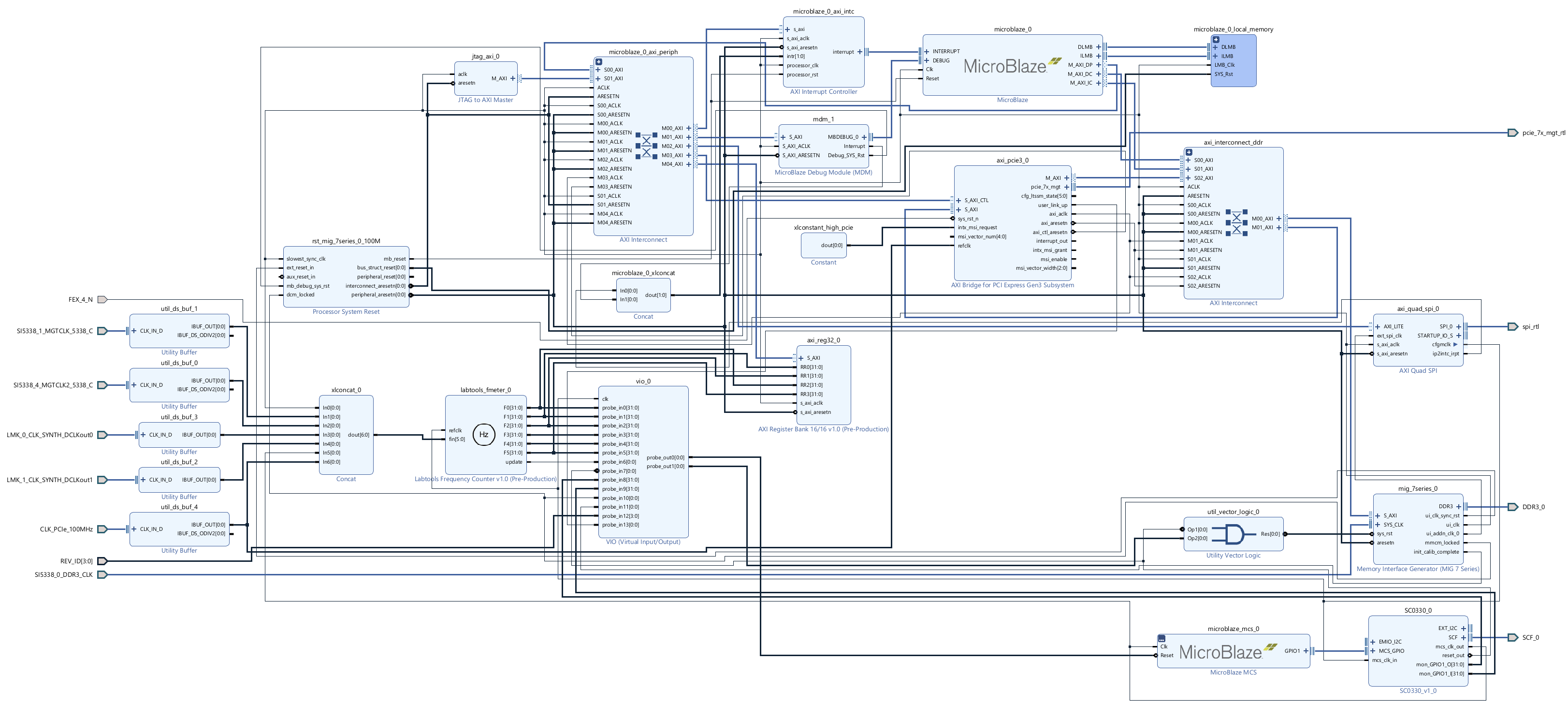

System Design - Vivado

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Block Design

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

Constrains

Basic module constrains

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 66 [current_design]

set_property CONFIG_VOLTAGE 1.8 [current_design]

set_property CFGBVS GND [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.SPI_32BIT_ADDR YES [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property BITSTREAM.CONFIG.M1PIN PULLNONE [current_design]

set_property BITSTREAM.CONFIG.M2PIN PULLNONE [current_design]

set_property BITSTREAM.CONFIG.M0PIN PULLNONE [current_design]

set_property BITSTREAM.CONFIG.USR_ACCESS TIMESTAMP [current_design] |

| Code Block | ||||

|---|---|---|---|---|

| ||||

#

#

#

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLUP [current_design] |

Design specific constrain

...

| language | ruby |

|---|---|

| title | _i_io.xdc |

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

| language | ruby |

|---|---|

| title | _i_pcie.xdc |

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

PCB REV01:

| Code Block | ||||

|---|---|---|---|---|

| ||||

#----------

#CLK DDR3

#AC9 /AD9 for REV01

#AB11 / AC11 for REV02

set_property PACKAGE_PIN AC9 [get_ports CLK_DDR3_200MHz_clk_p]

set_property PACKAGE_PIN AD9 [get_ports CLK_DDR3_200MHz_clk_n]

set_property IOSTANDARD DIFF_SSTL15 [get_ports CLK_DDR3_200MHz_clk_p]

set_property IOSTANDARD DIFF_SSTL15 [get_ports CLK_DDR3_200MHz_clk_n] |

PCB REV02:

...

| language | ruby |

|---|---|

| title | _i_io_ddr_clk.xdc |

...

Software Design - SDK/HSI

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

For SDK project creation, follow instructions from:

Application

...

...

...

...

...

...

srec_spi_bootloader

...

...

modified Files: blconfig.h, bootloader.c

...

add Files: si5338.h, si5338.c, register_map.h

...

...

...

...

- add -410 assembly variant

...

...

- 2018.2 release

...

...

- 2017.4 release

...

...

...

...

...

...