Page History

Template Revision 2.2 - on construction

| HTML |

|---|

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

...

| hidden | true |

|---|---|

| id | Comments |

Important General Note:

...

Export PDF to download, if vivado revision is changed!

Designate all graphics and pictures with a number and a description, Use "Scroll Title" macro

...

...

Figure template (note: inner scroll ignore/only only with drawIO object):

...

| anchor | Figure_xyz |

|---|---|

| title | Text |

| Scroll Ignore |

|---|

Create DrawIO object here: Attention if you copy from other page, use |

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

...

Table template:

- Layout macro can be use for landscape of large tables

- Set column width manually(can be used for small tables to fit over whole page) or leave empty (automatically)

...

| anchor | Table_xyz |

|---|---|

| title | Text |

...

| Scroll pdf ignore | ||||

|---|---|---|---|---|

Table of contents

|

Overview

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Zynq Design PS with Linux and two Ethernet PHYs connected over EMIO and PL.

Refer to http://trenz.org/te0728-info for the current online version of this manual and other available documentation.

Key Features

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Excerpt |

|---|

|

Revision History

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| anchor | Table_DRH |

|---|---|

| title | Design Revision History |

...

- rework board part files

- rework petalinux device tree, driver

- small changes on xdc

...

- initial release

...

...

...

...

...

...

...

...

Linux Message: "macb ... .ethernet eth...: unable to generate target frequency: 25000000 Hz"

...

Requirements

...

...

...

...

...

...

...

...

...

Basic description of TE Board Part Files is available on TE Board Part Files.

Complete List is available on <design name>/board_files/*_board_files.csv

Design supports following modules:

...

...

...

...

...

...

...

Additional HW Requirements:

...

...

...

...

Content

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

Launch

Programming

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

QSPI

Optional for Boot.bin on QSPI Flash and image.ub on SD.

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp u-boot

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup

optional "TE::pr_program_flash_binfile -swapp hello_te0728" possible - Copy image.ub on SD-Card

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Insert SD-Card

SD

- Copy image.ub and Boot.bin on SD-Card.

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Set Boot Mode to SD-Boot.

- Depends on Carrier, see carrier TRM.

- Insert SD-Card in SD-Slot.

JTAG

Not used on this Example.

Usage

- Prepare HW like described on section 43680477

- Connect UART USB (most cases same as JTAG)

- Select SD Card as Boot Mode

Note: See TRM of the Carrier, which is used. - Power On PCB

Note: 1. Zynq Boot ROM loads FSBL from SD into OCM, 2. FSBL loads U-boot from SD into DDR, 3. U-boot load Linux from SD into DDR

Linux

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Linux Console:

Note: Wait until Linux boot finished For Linux Login use:- User Name: root

- Password: root

- You can use Linux shell now.

- I2C 0 Bus type: i2cdetect -y -r 0

- ETH0 works with udhcpc

- ETH1 must be configured manually

- ifconfig eth1 up

- ifconfig eth1 <ip>

Note for Ping test disable ETH0

- RTC check: dmesg | grep rtc

System Design - Vivado

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

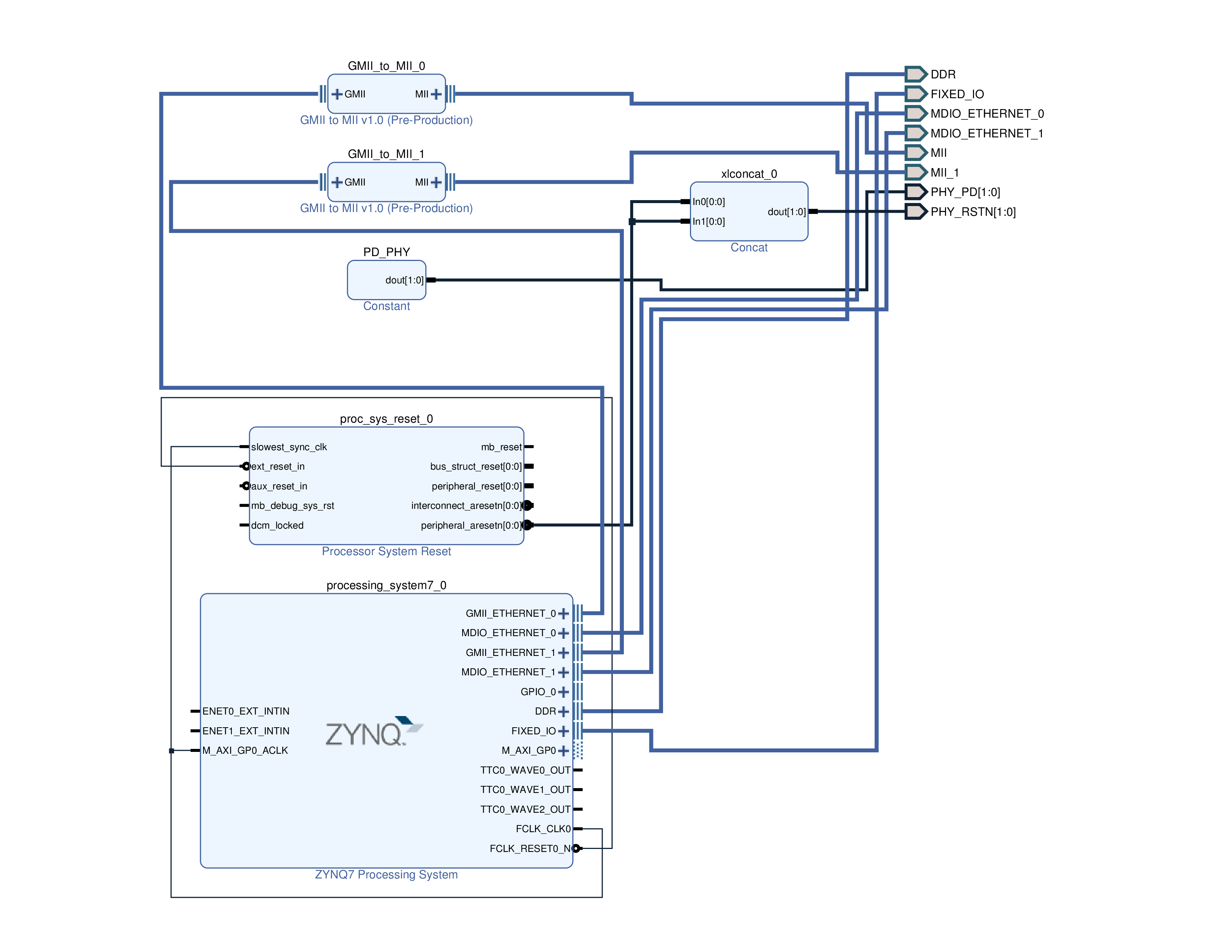

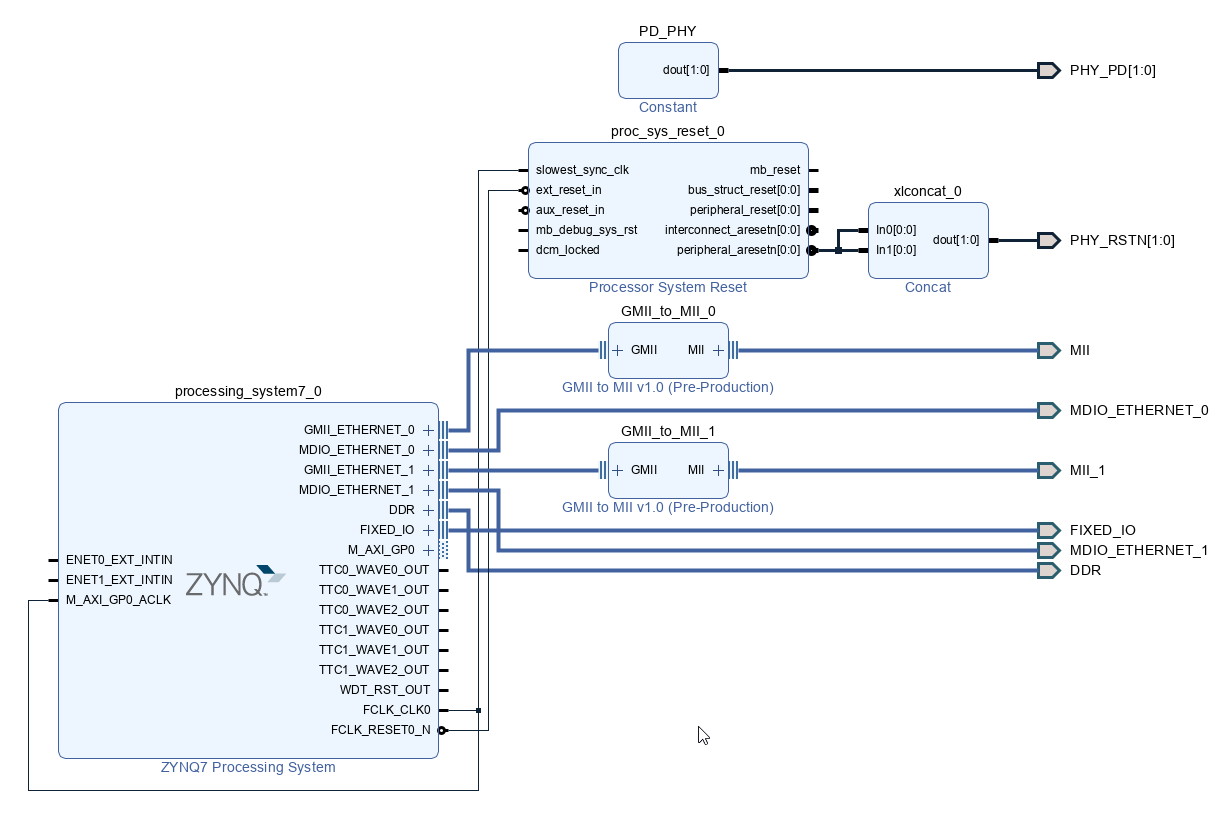

Block Design

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

PS Interfaces

...

| anchor | Table_PSI |

|---|---|

| title | PS Interfaces |

...

Constrains

Basic module constrains

| Code Block | ||||

|---|---|---|---|---|

| ||||

#

# Common bitgen related settings

#

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property CFGBVS VCCO [current_design]

set_property BITSTREAM.CONFIG.USR_ACCESS TIMESTAMP [current_design] |

Design specific constrain

| Code Block | ||||||||

|---|---|---|---|---|---|---|---|---|

| ||||||||

#############

#ETH0/ETH1

#####

#pwr_down

set_property PACKAGE_PIN L21 [get_ports {PHY_PD[0]}]

set_property PACKAGE_PIN R20 [get_ports {PHY_PD[1]}]

#rst_n

set_property PACKAGE_PIN M15 [get_ports {PHY_RSTN[0]}]

set_property PACKAGE_PIN R16 [get_ports {PHY_RSTN[1]}]

#io standard

set_property IOSTANDARD LVCMOS33 [get_ports {PHY*}]

set_property IOSTANDARD LVCMOS33 [get_ports MDIO_*]

set_property IOSTANDARD LVCMOS33 [get_ports {MII_*}]

#pullup/down for PHY address 1

set_property PULLUP true [get_ports MII_col]

set_property PULLDOWN true [get_ports {MII_rxd[0]}]

set_property PULLDOWN true [get_ports {MII_rxd[1]}]

set_property PULLDOWN true [get_ports {MII_rxd[2]}]

set_property PULLDOWN true [get_ports {MII_rxd[3]}]

#pullup/down for PHY address 3

set_property PULLUP true [get_ports MII_1_col]

set_property PULLUP true [get_ports {MII_1_rxd[0]}]

set_property PULLDOWN true [get_ports {MII_1_rxd[1]}]

set_property PULLDOWN true [get_ports {MII_1_rxd[2]}]

set_property PULLDOWN true [get_ports {MII_1_rxd[3]}]

#############

#ETH0

#####

set_property PACKAGE_PIN M16 [get_ports MDIO_ETHERNET_0_mdio_io]

set_property PACKAGE_PIN P16 [get_ports MDIO_ETHERNET_0_mdc]

set_property PACKAGE_PIN M22 [get_ports {MII_txd[3]}]

set_property PACKAGE_PIN K21 [get_ports {MII_txd[2]}]

set_property PACKAGE_PIN M17 [get_ports {MII_txd[1]}]

set_property PACKAGE_PIN J22 [get_ports {MII_txd[0]}]

set_property PACKAGE_PIN J20 [get_ports {MII_rxd[3]}]

set_property PACKAGE_PIN J18 [get_ports {MII_rxd[2]}]

set_property PACKAGE_PIN K18 [get_ports {MII_rxd[1]}]

set_property PACKAGE_PIN L17 [get_ports {MII_rxd[0]}]

set_property PACKAGE_PIN L16 [get_ports MII_col]

set_property PACKAGE_PIN N15 [get_ports MII_crs]

set_property PACKAGE_PIN L18 [get_ports MII_rx_clk]

set_property PACKAGE_PIN P15 [get_ports MII_rx_dv]

set_property PACKAGE_PIN P17 [get_ports MII_rx_er]

set_property PACKAGE_PIN K19 [get_ports MII_tx_clk]

set_property PACKAGE_PIN J21 [get_ports MII_tx_en]

#############

#ETH1

#####

set_property PACKAGE_PIN T16 [get_ports MDIO_ETHERNET_1_mdio_io]

set_property PACKAGE_PIN T17 [get_ports MDIO_ETHERNET_1_mdc]

set_property PACKAGE_PIN R21 [get_ports {MII_1_txd[3]}]

set_property PACKAGE_PIN P22 [get_ports {MII_1_txd[2]}]

set_property PACKAGE_PIN P21 [get_ports {MII_1_txd[1]}]

set_property PACKAGE_PIN N22 [get_ports {MII_1_txd[0]}]

set_property PACKAGE_PIN T19 [get_ports {MII_1_rxd[3]}]

set_property PACKAGE_PIN T18 [get_ports {MII_1_rxd[2]}]

set_property PACKAGE_PIN R19 [get_ports {MII_1_rxd[1]}]

set_property PACKAGE_PIN R18 [get_ports {MII_1_rxd[0]}]

set_property PACKAGE_PIN P20 [get_ports MII_1_col]

set_property PACKAGE_PIN N18 [get_ports MII_1_crs]

set_property PACKAGE_PIN M19 [get_ports MII_1_rx_clk]

set_property PACKAGE_PIN N17 [get_ports MII_1_rx_dv]

set_property PACKAGE_PIN P18 [get_ports MII_1_rx_er]

set_property PACKAGE_PIN N19 [get_ports MII_1_tx_clk]

set_property PACKAGE_PIN M21 [get_ports MII_1_tx_en]

|

Software Design - SDK/HSI

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

For SDK project creation, follow instructions from:

Application

Template location: ./sw_lib/sw_apps/

zynq_fsbl

TE modified 2018.2 FSBL

Xilinx default FSBL,

Changes::

- only active FSBL banner independence form debug flags

zynq_fsbl_flash

TE modified 2018.2 FSBL

FSBL(for Vivado/SDK GUI only) to initialise Zynq for QSPI programming

Changes:

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

- see xfsbl_initialisation.main.c

u-boot

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin.

Software Design - PetaLinux

| HTML |

|---|

<!--

optional chapter

--> |

Description currently not available.

Config

No changes.

U-Boot

...

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

...

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

...

- HDF is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

...

- "prebuilt\os\petalinux\default" or "prebuilt\os\petalinux\<short name>"

Notes: Scripts select "prebuilt\os\petalinux\<short name>", if exist, otherwise "prebuilt\os\petalinux\default"

...

- Run on Vivado TCL: TE::sw_run_hsi

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk

Note: See SDK Projects

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

Kernel

...

Activate:

- I2C-tools

...

...

...

...

No additional software is needed.

...

...

...

...

...

...

...

...

...

...

...