Page History

| HTML |

|---|

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

...

| hidden | true |

|---|---|

| id | Comments |

Important General Note:

...

Export PDF to download, if vivado revision is changed!

Designate all graphics and pictures with a number and a description, Use "Scroll Title" macro

...

...

...

Create DrawIO object here: Attention if you copy from other page, use

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

...

Table template:

- Layout macro can be use for landscape of large tables

- Set column width manually(can be used for small tables to fit over whole page) or leave empty (automatically)

...

| anchor | Table_xyz |

|---|---|

| title | Text |

...

| Scroll pdf ignore | ||||||

|---|---|---|---|---|---|---|

Table of contents

|

Overview

...

| hidden | true |

|---|---|

| id | Comments |

Notes :

...

short description of the design

Short Link of "Scroll only" macro:

...

...

...

List of available short links: https://wiki.trenz-electronic.de/display/CON/Redirects

This demo is a Webserver which utilizes SmartFusion2 SoC ARM Cortex-M3 core, Ethernet, USB / COM-port, Real Time Clock and the on-board LEDs.

The demo is offered in two variants, one which is stored into the embedded non-volatile memory (eNVM) and the other executed from the external DDR3/L SDRAM memory.

Refer to http://trenz.org/tem0002-info for the current online version of this manual and other available documentation.

Key Features

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

- Libero Hardware Project

- SoftConsole Software Project

- Board configuration file

- Manual

...

...

Download

...

...

...

...

...

...

...

Design Flow

...

...

...

The zip archive must to be extracted. The board configuration file needs to copied into your SoftConsole installation directory. When taking the required SoftConsole version into account, SoftConsole version 6.2, and the default installation path, copy the board configuration file into:

"C:\Microsemi\SoftConsole_v6.2\openocd\share\openocd\scripts\board\"

mit thomas bereden

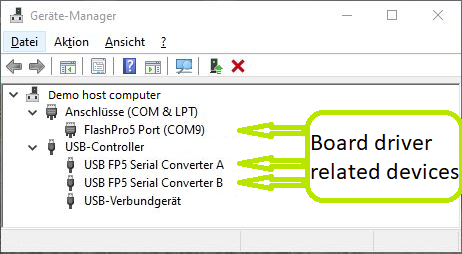

Connect the board via USB cable to your demo host computer. Check in the Windows Device Manager the appearance of the tree board driver related devices:

- FlashPro5 Port (ComX)

- USB FP5 Serial Converter A

- USB FP5 Serial Converter B

The Device Manager is accessible via "Right mouse click context menu" from the Windows Start Menu Button.

...

...

Launch

Programming Hardware design

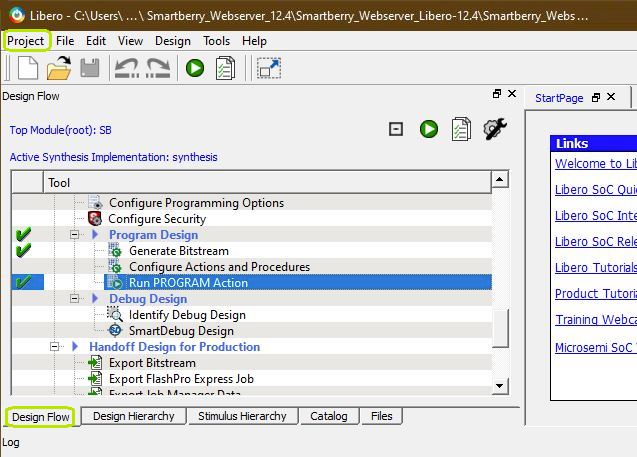

Open Libero 12.4, in the to left corner, open the demo hardware project via "Project > Open Project" and point to file dialog to the demo archives hardware project dicsk:\Path_to_the_hardware_project_inside_the_archive\ , double left mouse click onto the project file "Smartberry_Webserver.prjx" to open it.

The board is automatically selected and setup to be flashed by Libero.

In the upper left section of Libero, select the tab "Design Flow" and flash it to the board via "Program Design > and double left mouse click onto Run PROGRAM Action".

Warnings can be ignored.

The hardware design is volatile and therefore lost when powering the board down.

Programming Software project

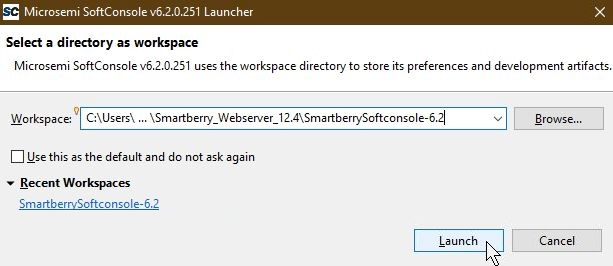

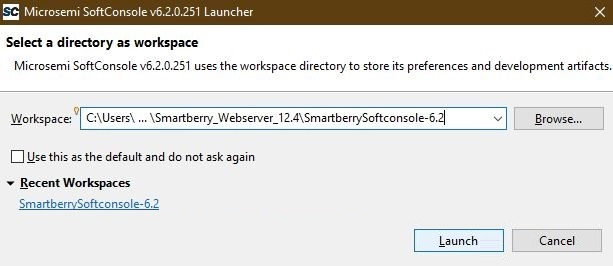

Open SoftConsole 6.2 and point the "Workspace:" to the folder "SmartberrySoftconsole-6.2" inside the demo folder.

Subsequently the program opens.

The SoftConsole display to the left the projects which the Workspace contains.

The two demo projects "Smartberry_Webserver_6.2" and "Smartberry_Webserver_DDR_6.2" are identical variants of the demo, they only differ in the memory location. The first one is stored in embedded non volatile memory (eNVM) and the later is stored volatile in the external DDR ram and therefore lost during power down.

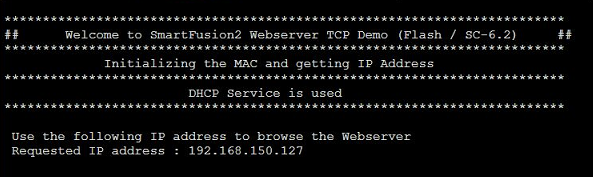

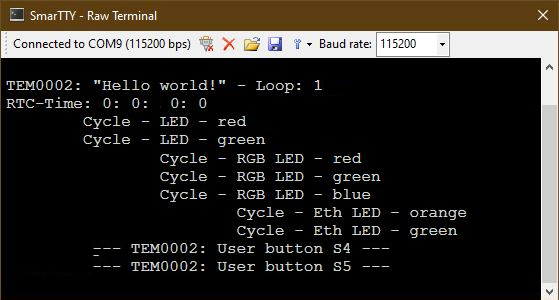

Before flashing the demo, open a comport terminal to the boards comport, so that its messages about the used IP Adress and Mode can be captured.

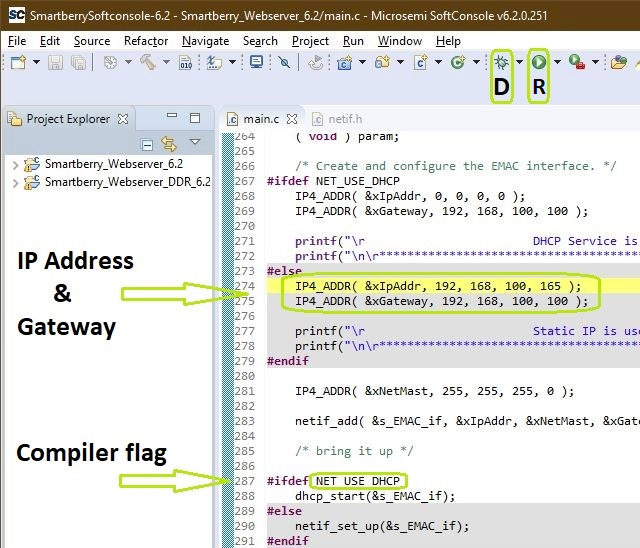

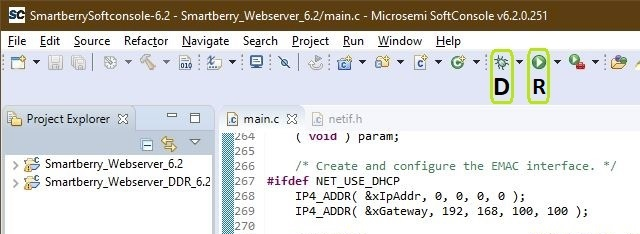

To simply run the demo press the triangle right to the button marked with a "R" in the picture above and select the variant of the demo.

Pressing the triangle next to the button marked with "D" let you select which variant to be executed in debug mode.

Debug controlls - Resume - Pause - Stop

Switch between Debug and Run perspective (upper right corner program window)

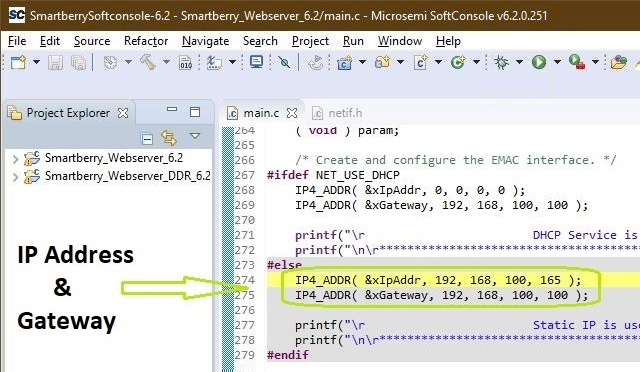

Static IP configuration

To disengaging the DHCP mode one has to setup up an IP Address in the code unit "main.c" line 274, a gateway address has is not required. Alternativly, the demo hosts IP Address can be changed.

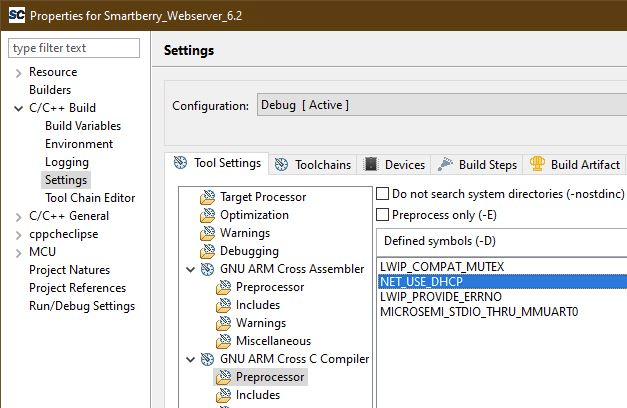

Furthermore the corresponding compiler flag needs to be deleted in the project setting. To do so, in the "Project Explorer" tab, right mouse click onto the project and select Properties in the appearing menu.

In the left section of the properties window select "C/C++ Build > Settings" in the right section select the tab "Tool Settings > GNU ARM Cross C Compiler > Preprocessor" under "Defined symbols (-D)" delete the compiler flag "NET_USE_DHCP" and press "Apply". Confirm the following dialog and press "Cancel".

Lastly, the project needs to be recompiled. In the top menu of the SoftConsole select "Project > Build ALL / Build Project".

Warnings can be ignored.

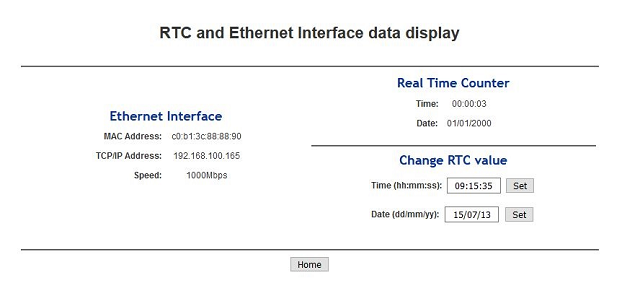

Pictures of the webserver pages

Open a new tab in a web browser and enter the IP Adress from the comport terminal.

...

Design Flow

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Note |

|---|

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first lunch. |

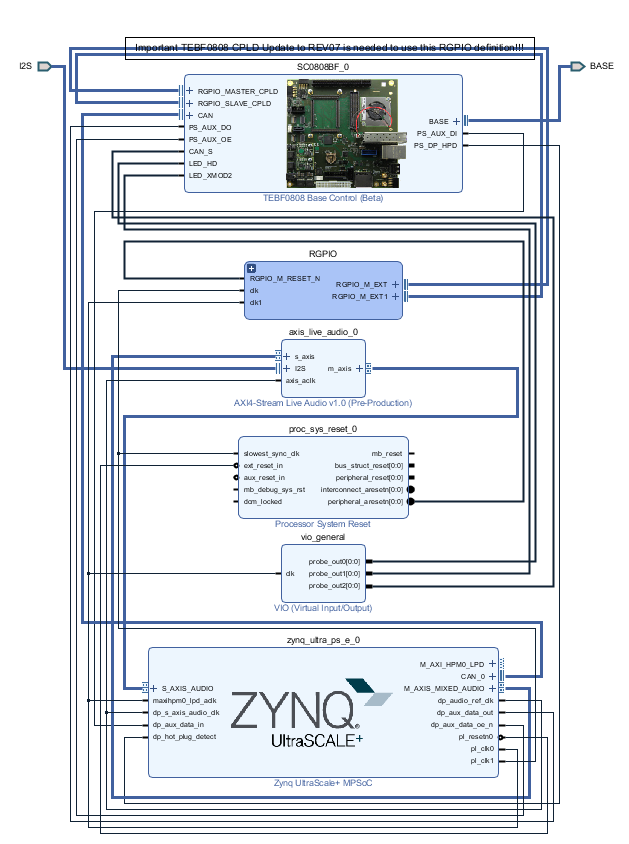

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

Xilinx Development Tools#XilinxSoftware-BasicUserGuidesVivado Projects - TE Reference DesignProject Delivery.

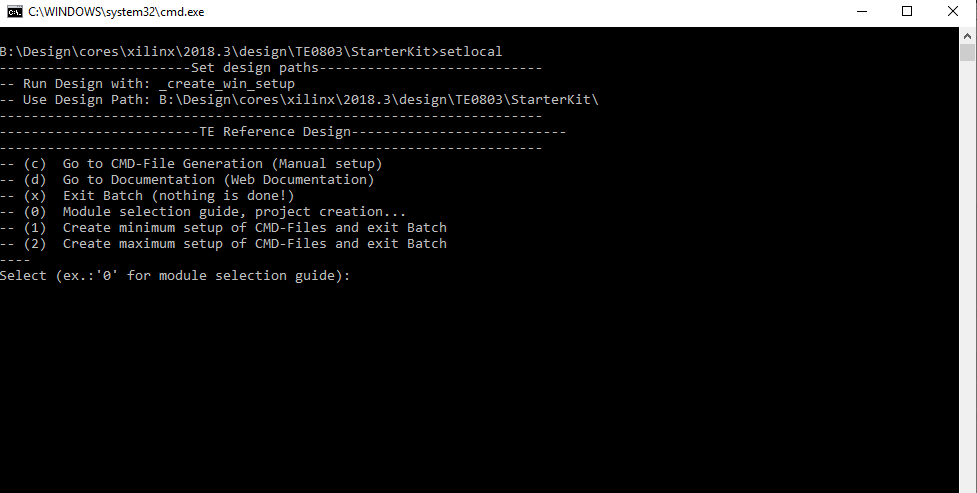

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

_create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:Press 0 and enter to start "Module Selection Guide"(optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process)(optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"Note: Select correct one, see alsoTE Board Part FilesImportant: Use Board Part Files, which ends with *_tebf0808

Create XSA and export to prebuilt folderRun on Vivado TCL: TE::hw_build_design -export_prebuiltNote: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

Create Linux (bl31.elf, uboot.elf , Image and system.dtb) with exported XSAXSA is exported to "prebuilt\hardware\<short name>"Note: HW Export from Vivado GUI create another path as default workspace.Create Linux images on VM, see PetaLinux KICKstartUse TE Template from /os/petalinux/Execute the script file for Debian/Ubuntu

Add Linux files (bl31.elf, uboot.elf , Image and system.dtb) to prebuilt folder"prebuilt\os\petalinux\<ddr size>" or "prebuilt\os\petalinux\<short name>"

Generate Programming Files with VitisRun on Vivado TCL: TE::sw_run_vitis -allNote: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv"(alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_vitisNote: TCL scripts generate also platform project, this must be done manuelly in case GUI is used. See Vitis

Preparing SD card for SD Filesystem and hard disk for HD Filesystem → See Programming section

Launch

...

...

- Programming and Startup procedure

Programming

Usage

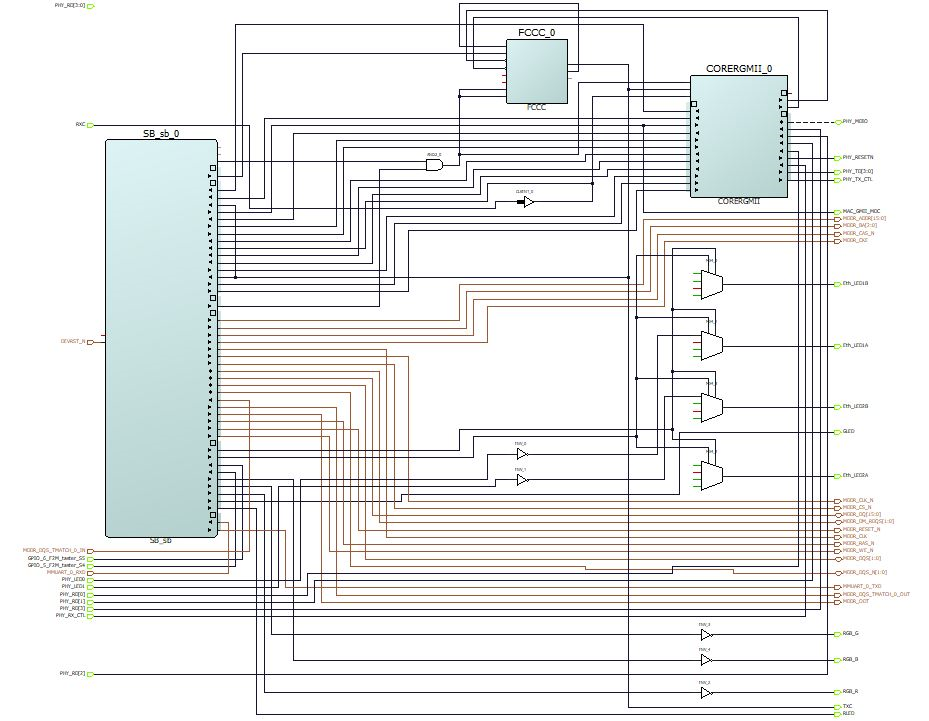

System Design - Libero

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Smart Design

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

Constrains

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLNONE [current_design]

|

Software Design - SoftConsole

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Application

...

| hidden | true |

|---|---|

| id | Comments |

----------------------------------------------------------

FPGA Example

scu

MCS Firmware to configure SI5338 and Reset System.

srec_spi_bootloader

TE modified 2019.2 SREC

Bootloader to load app or second bootloader from flash into DDR

Descriptions:

- Modified Files: blconfig.h, bootloader.c

- Changes:

- Add some console outputs and changed bootloader read address.

- Add bugfix for 2018.2 qspi flash

xilisf_v5_11

TE modified 2019.2 xilisf_v5_11

...

Zynq Example:

...

...

...

...

- READ MAC from EEPROM and make Address accessible by UBOOT (need copy defines on uboot platform-top.h)

- CPLD access

- Read CPLD Firmware and SoC Type

- Configure Marvell PHY

...

ZynqMP Example:

...

zynqmp_fsbl

TE modified 2019.2 FSBL

General:

- Modified Files: xfsbl_main.c, xfsbl_hooks.h/.c, xfsbl_board.h/.c(search for 'TE Mod' on source code)

- Add Files: te_xfsbl_hooks.h/.c (for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device Name

Module Specific:

- Add Files: all TE Files start with te_*

- Si5338 Configuration

- ETH+OTG Reset over MIO

zynqmp_fsbl_flash

TE modified 2019.2 FSBL

General:

- Modified Files: xfsbl_initialisation.c, xfsbl_hw.h, xfsbl_handoff.c, xfsbl_main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

zynqmp_pmufw

Xilinx default PMU firmware.

----------------------------------------------------------

General Example:

hello_te0820

Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output.

u-boot

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin.

SDK template in ./sw_lib/sw_apps/ available.

zynqmp_fsbl

TE modified 2019.2 FSBL

General:

- Modified Files: xfsbl_main.c, xfsbl_hooks.h/.c, xfsbl_board.h/.c(search for 'TE Mod' on source code)

- Add Files: te_xfsbl_hooks.h/.c (for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device Name

Module Specific:

- Add Files: all TE Files start with te_*

- Si5345 Configuration

- OTG+PCIe Reset over MIO

- I2C MUX for EEPROM MAC

zynqmp_fsbl_flash

TE modified 2019.2 FSBL

General:

- Modified Files: xfsbl_initialisation.c, xfsbl_hw.h, xfsbl_handoff.c, xfsbl_main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

zynqmp_pmufw

Xilinx default PMU firmware.

hello_te0808

Hello TE0808 is a Xilinx Hello World example as endless loop instead of one console output.

u-boot

U-Boot.elf is generated with PetaLinux. Vitis is used to generate Boot.bin.

Additional Software

| Page properties | ||||

|---|---|---|---|---|

| ||||

| Note: |

...