Page History

...

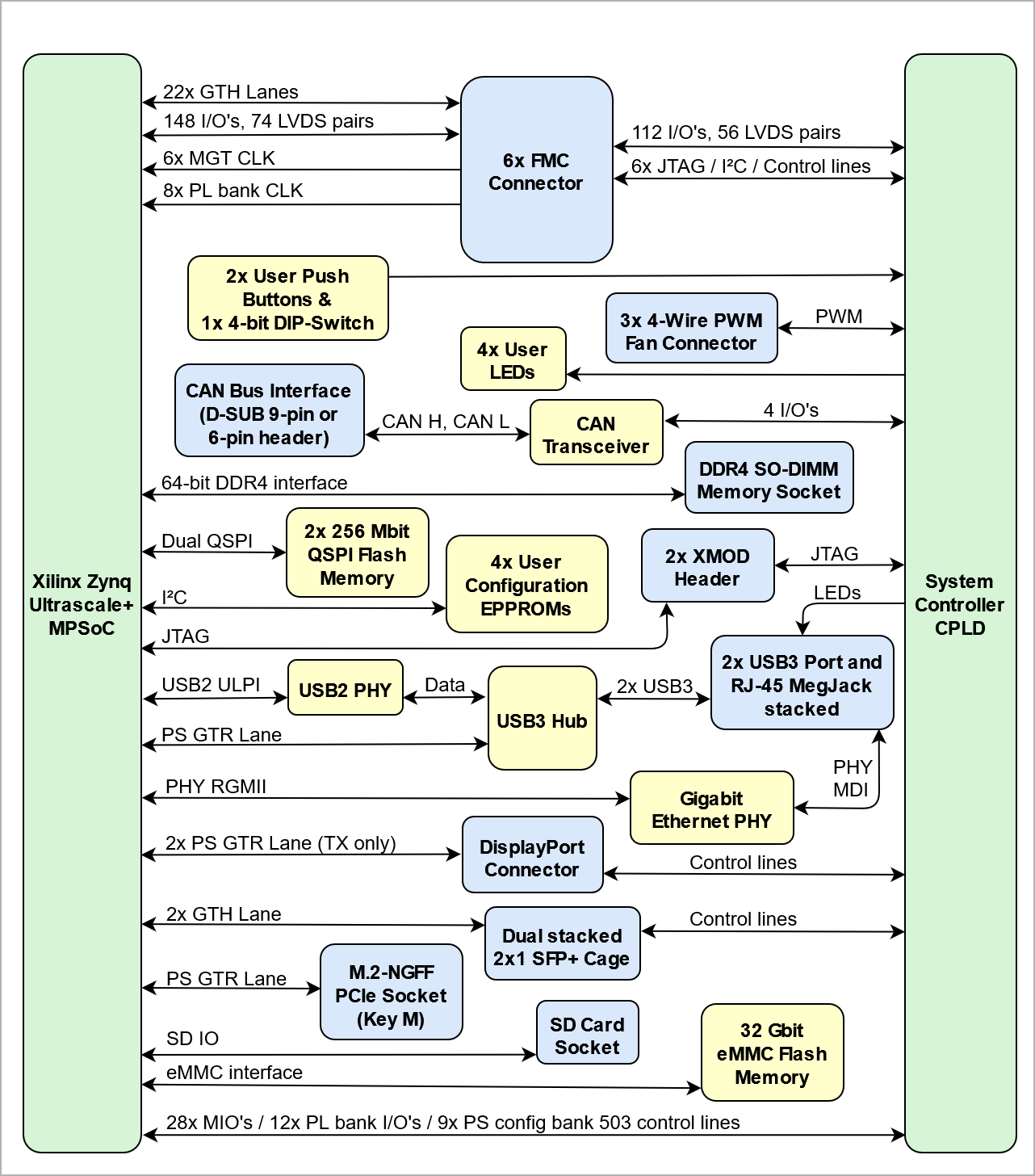

The Trenz Electronic TEB0911 UltraRack+ board is integrating a Xilinx Zynq UltrascaleUltraScale+ MPSoC with 4 GByte Flash memory for configuration and operation, DDR4-SDRAM SO-DIMM socket with 64-bit wide data bus, 22 MGT lanes and powerful switch-mode power supplies for all on-board voltages. . The TEB0911 board exposes the pins of the Zynq MPSoC to accessible connectors and provides a whole range of on-board components to test and evaluate the Zynq UltrascaleUltraScale+ MPSoC and for developing purposes. The board is capable to be fitted to a enclosure, whereby on the enclosure's rear and front panel, I/O's, LVDS-pairs and MGT lanes are accessible through 6 on-board FMC connectors and other standard high-speed interfaces, namely USB3, SFP+, SSD, GbE, etc.

...

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

Main Components

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

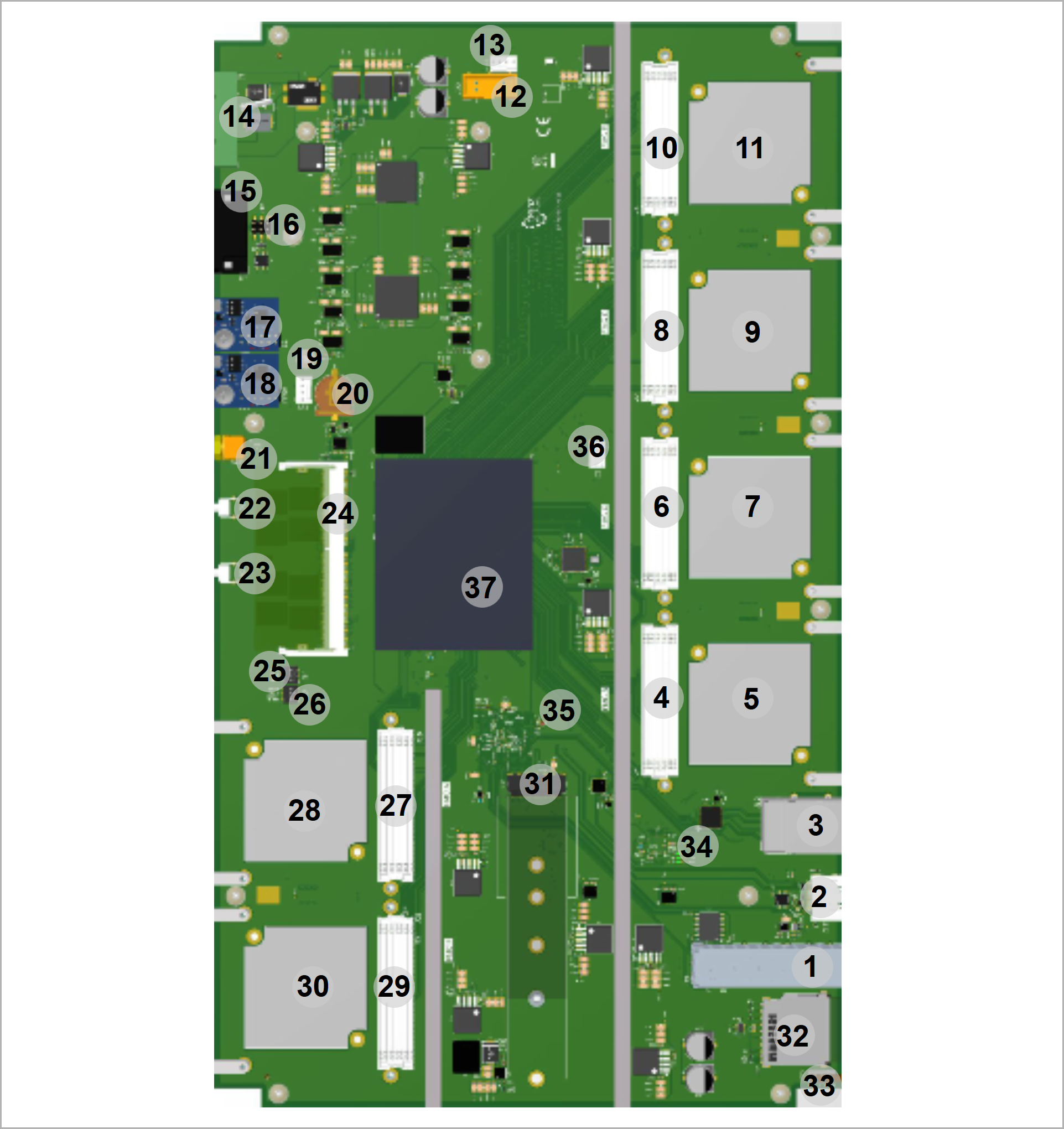

- SFP+ 2x1 cage with integrated LED light pipes, J9

- DisplayPort connector, J12

- USB3 A 2x , RJ45 1x (stacked), J13

- FMC connector (FMC B), J4

- FMC B cooling fan, M2

- FMC connector (FMC C), J8

- FMC C cooling fan, M3

- FMC connector (FMC D), J7

- FMC D cooling fan, M4

- FMC connector (FMC E), J6

- FMC E cooling fan, M5

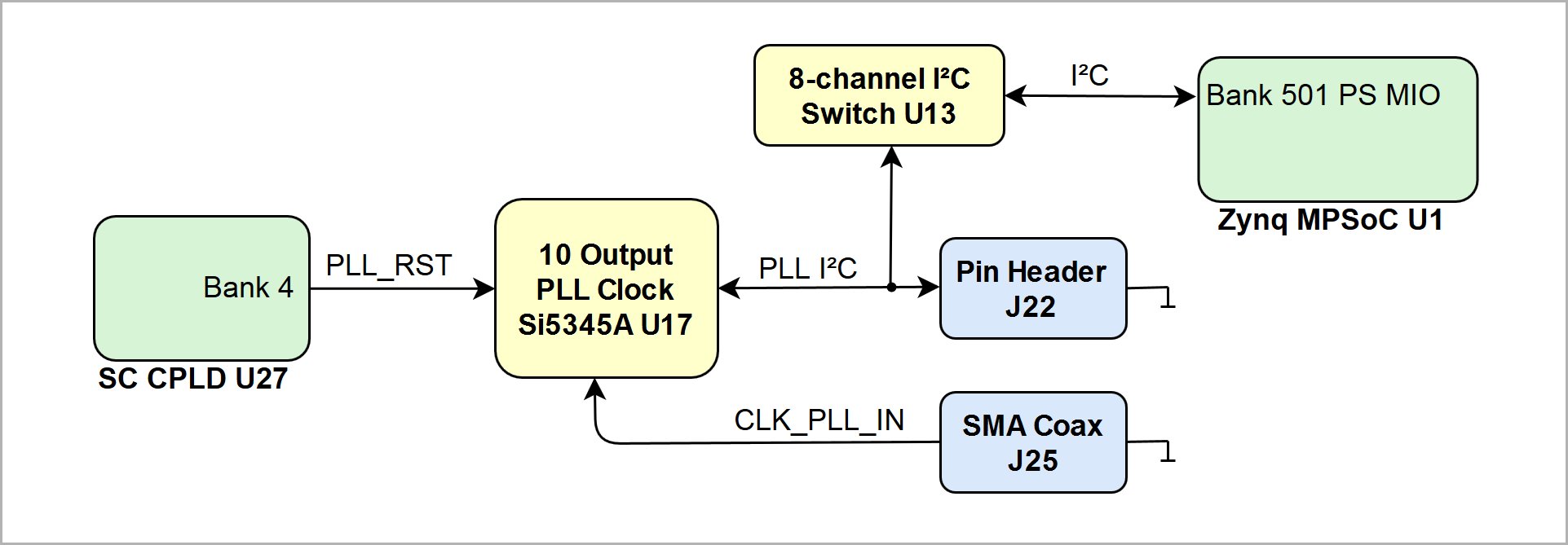

- I²C programming header of on-board PLL clock generator U17, J22

- 4-Wire PWM fan connector, J23

- Main Power Jack 24V, J1

- CAN bus D-SUB 9-pin male connector, J3

- CAN bus 6-pin header male, J15

- XMOD JTAG header for access to System Controller CPLD, J35

- XMOD JTAG header for access to Zynq MPSoC, J24

- 4-Wire PWM fan connector, J33

- Battery Holder CR1220, B1

- SMA coaxial connector (PLL Si5345A U17 clock input), J25

- Push Button, S1

- Push Button, S2

- DDR4 SO-DIMM socket, U3

- 4-bit DIP-switch, S4

- 4-bit DIP-switch, S3

- FMC connector (FMC A), J10

- FMC A cooling fan, M1

- FMC connector (FMC F), J21

- FMC F cooling fan, M6

- NGFF M.2 PCIe socket (Key M), U2

- SD Card socket, J11

- User LEDs (3x green, 1x red) with LED light pipe, D13 ... D16

- Green LEDs dedicated to USB3 hub U4, D17 ... D19

- Red LED indicating FPGAs 'DONE' signal, D6

- 4-Wire PWM fan connector, J2

- Xilinx Zynq Ultrascale+ MPSoC, U1

Initial Delivery State

Storage device name | Content | Notes |

|---|---|---|

| User configuration EEPROMs (1x Microchip 24LC128-I/ST, 3x Microchip 24AA025E48T-I/OT) | Empty | Not programmed |

| USB3 HUB Configuration EEPROM (Microchip 24LC128-I/ST) | Empty | Not programmed |

| Si5338A programmable PLL NVM OTP | Empty | Not programmed |

| Si5345A programmable PLL NVM OTP | Empty | Not programmed |

| eMMC Flash memory | Empty | Not programmed |

| 2x QSPI Flash memory | Empty | Not programmed |

...

| HTML |

|---|

<!-- MGT lanes should be listed separately, as they are more specific than just general I/Os. --> |

Following tables contains information about the interfaces, I/O's, clock and VCCIO sources available on the FMC connectors A - F:

Anchor FMC A FMC A

FMC A

FMC A Interfaces:

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes |

|---|---|---|---|---|---|---|

J10 (FMC A) | I/O | 12 | 6 | Bank 44 HD | FMCAF_1V8 | - |

| 56 | 28 | SC CPLD U27 Bank 1 | FMCAF_1V8 | - | ||

| I²C | 2 | - | I²C-Switch U37 | - | Muxed to MIO Bank 501 I²C Inteface | |

| JTAG | 4 | - | SC CPLD U27 Bank 2 | 3.3VSB | - | |

| MGT | - | 8 (4 x RX/TX) | Bank 128 GTH | - | 4x MGT lanes | |

| Clock Input | - | 1 | Bank 128 GTH | - | 1x Reference clock input to MGT bank | |

| Control Signals | 3 | - | SC CPLD U27 Bank 0 | 3.3VSB | 'FMCA_PG_C2M', 'FMCA_PG_M2C', 'FMCA_PRSNT' |

Table 3: FMC A connector interfaces

FMC A MGT Lanes:

| FMC | MGT Lane | Bank | Type | Signal Schematic Name | FMC Connector Pin | FPGA Pin |

|---|---|---|---|---|---|---|

J10 (FMC A) | 0 | 128 | GTH |

| J10-C6 | MGTHRXP0_128, T33 |

| 1 | 128 | GTH |

| J10-A2 | MGTHRXP1_128, P33 | |

| 2 | 128 | GTH |

| J10-A6 | MGTHRXP2_128, N31 | |

| 3 | 128 | GTH |

| J10-A10 | MGTHRXP3_128, M33 |

Table 4: FMC A connector MGT lanes

FMC A Clock Signals:

| FMC | Signal Schematic Name | Bank | FMC Connector Pin | FPGA Pin | Notes |

|---|---|---|---|---|---|

J10 (FMC A) |

| 128 | J10-D4 | MGTREFCLK0P_128, R27 | Supplied by attached module |

Table 5: FMC A connector clock signal input

FMC A VCC/VCCIO:

| FMC | Available VCC/VCCIO | FMC Connector Pin | Source | Notes |

|---|---|---|---|---|

J10 (FMC A) | FMCA_3V3 | J10-D36 | DCDC U32, | Enable by SC CPLD U27, bank 2, pin Y18 |

| 3V3SB | J10-D32 | DCDC U50, max. cur.: 1A | not dedicated for FMC connectors | |

| 12V_FMC_AF | J10-C35 | DCDC U51, | - | |

| FMCAF_1V8 | J10-H40 | DCDC U39, | Enable by SC CPLD U27, bank 2, pin W19 |

Table 6: FMC A connector available VCC/VCCIO

FMC A Cooling Fan:

| FMC | Fan Designator | Enable Signal | Notes |

|---|---|---|---|

J10 (FMC A) | M1 | Enable by SC CPLD U27, bank 2, pin Y19 | - |

Table 7: FMC A connector cooling fan

Anchor FMC F FMC F

FMC F

FMC F Interfaces:

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes |

|---|---|---|---|---|---|---|

J21 (FMC F) | I/O | 12 | 6 | Bank 44 HD | FMCAF_1V8 | - |

| 28 | 14 | SC CPLD U27 Bank 1 | FMCAF_1V8 | - | ||

| 28 | 14 | SC CPLD U27 Bank 3 | FMCAF_1V8 | - | ||

| I²C | 2 | - | I²C-Switch U37 | - | Muxed to MIO Bank 501 I²C Inteface | |

| JTAG | 4 | - | SC CPLD U27 Bank 2 | 3.3VSB | - | |

| MGT | - | 4 (2 x RX/TX) | Bank 129 GTH | - | 2x MGT lanes | |

| Clock Input | - | 1 | Bank 129 GTH | - | 1x Reference clock input to MGT bank | |

| Control Signals | 3 | - | SC CPLD U27 Bank 2 | 3.3VSB | 'FMCF_PG_C2M', 'FMCF_PG_M2C', 'FMCF_PRSNT' |

Table 8: FMC F connector interface

FMC F MGT Lanes:

| FMC | MGT Lane | Bank | Type | Signal Schematic Name | FMC Connector Pin | FPGA Pin |

|---|---|---|---|---|---|---|

J21 (FMC F) | 0 | 129 | GTH |

| J21-C6 | MGTHRXP0_129, L31 |

| 1 | 129 | GTH |

| J21-A2 | MGTHRXP1_129, K33 |

Table 9: FMC F connector MGT lanes

FMC F Clock Signals:

| FMC | Signal Schematic Name | Bank | FMC Connector Pin | FPGA Pin | Notes |

|---|---|---|---|---|---|

J21 (FMC F) |

| 129 | J21-D4 | MGTREFCLK0P_129, L27 | Supplied by attached module |

Table 10: FMC F connector clock signal input

FMC F VCC/VCCIO:

| FMC | Available VCC/VCCIO | FMC Connector Pin | Source | Notes |

|---|---|---|---|---|

J21 (FMC F) | FMCF_3V3 | J21-D36 | DCDC U42, | Enable by SC CPLD U27, bank 2, pin Y10 |

| 3V3SB | J21-D32 | DCDC U50, max. cur.: 1A | not dedicated for FMC connectors | |

| 12V_FMC_AF | J21-C35 | DCDC U51, | - | |

| FMCAF_1V8 | J21-H40 | DCDC U39, | Enable by SC CPLD U27, bank 2, pin W19 |

Table 11: FMC F connector available VCC/VCCIO

FMC F Cooling Fan:

| FMC | Fan Designator | Enable Signal | Notes |

|---|---|---|---|

J21 (FMC F) | M6 | Enable by SC CPLD U27, bank 2, pin W18 | - |

Table 12: FMC F connector cooling fan

Anchor FMC B FMC B

FMC B

FMC B Interfaces:

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes |

|---|---|---|---|---|---|---|

J4 (FMC B) | I/O | 24 | 12 | Bank 47 HD | FMCBC_1V8 | - |

| 20 | 10 | Bank 48 HD | FMCBC_1V8 | - | ||

| 24 | 12 | Bank 49 HD | FMCBC_1V8 | - | ||

| I²C | 2 | - | I²C-Switch U13 | - | Muxed to MIO Bank 501 I²C Inteface | |

| JTAG | 4 | - | SC CPLD U27 Bank 0 | 3.3VSB | - | |

| MGT | - | 8 (4 x RX/TX) | Bank 130 GTH | - | 4x MGT lanes | |

| Clock Input | - | 2 | Bank 48 HD | - | 2x Reference clock inputs to PL bank | |

| - | 1 | Bank 130 GTH | - | 1x Reference clock input to MGT bank | ||

| Control Signals | 3 | - | SC CPLD U27 Bank 0 | 3.3VSB | 'FMCB_PG_C2M', 'FMCB_PG_M2C', 'FMCB_PRSNT' |

Table 13: FMC B connector interfaces

FMC B MGT Lanes:

| FMC | MGT Lane | Bank | Type | Signal Schematic Name | FMC Connector Pin | FPGA Pin |

|---|---|---|---|---|---|---|

J4 (FMC B) | 3 | 130 | GTH |

| J4-C6 | MGTHRXP3_130, B33 |

| 2 | 130 | GTH |

| J4-A2 | MGTHRXP2_130, C31 | |

| 1 | 130 | GTH |

| J4-A6 | MGTHRXP1_130, D33 | |

| 0 | 130 | GTH |

| J4-A10 | MGTHRXP0_130, E31 |

Table 14: FMC B connector MGT lanes

FMC B Clock Signals:

| FMC | Signal Schematic Name | Bank | FMC Connector Pin | FPGA Pin | Notes |

|---|---|---|---|---|---|

J4 (FMC B) |

| 130 | J4-D4 | MGTREFCLK0P_130, G27 | Supplied by attached module |

| 48 HD | J4-H4 | IO_L6P_HDGC_48, F17 | Supplied by attached module | |

| 48 HD | J4-G2 | IO_L5P_HDGC_48, G18 | Supplied by attached module |

Table 15: FMC B connector clock signal input

FMC B VCC/VCCIO:

| FMC | Available VCC/VCCIO | FMC Connector Pin | Source | Notes |

|---|---|---|---|---|

J4 (FMC B) | FMCB_3V3 | J4-D36 | DCDC U33, | Enable by SC CPLD U27, bank 0, pin G11 |

| 3V3SB | J4-D32 | DCDC U50, max. cur.: 1A | not dedicated for FMC connectors | |

| 12V | J4-C35 | DCDC U82, | not dedicated for FMC connectors | |

| FMCBC_1V8 | J4-H40 | DCDC U40, | Enable by SC CPLD U27, bank 0, pin A3 |

Table 16: FMC B connector available VCC/VCCIO

FMC B Cooling Fan:

| FMC | Fan Designator | Enable Signal | Notes |

|---|---|---|---|

J4 (FMC B) | M2 | Enable by SC CPLD U27, bank 0, pin A2 | - |

Table 17: FMC B connector cooling fan

Anchor FMC C FMC C

FMC C

FMC C Interfaces:

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes |

|---|---|---|---|---|---|---|

J8 (FMC C) | I/O | 20 | 10 | Bank 50 HD | FMCBC_1V8 | - |

| 6848 | 3424 | Bank 67 HP | FMCBC_1V8 | - | ||

| I²C | 2 | - | I²C-Switch U13 | - | Muxed to MIO Bank 501 I²C Inteface | |

| JTAG | 4 | - | SC CPLD U27 Bank 2 | 3.3VSB | - | |

| MGT | - | 8 (4 x RX/TX) | Bank 230 GTH | - | 4x MGT lanes | |

| Clock Input | - | 2 | Bank 50 HD | - | 2x Reference clock inputs to PL bank | |

| - | 1 | Bank 230 GTH | - | 1x Reference clock input to MGT bank | ||

| Control Signals | 3 | - | SC CPLD U27 Bank 2 | 3.3VSB | 'FMCC_PG_C2M', 'FMCC_PG_M2C', 'FMCC_PRSNT' |

Table 18: FMC C connector interfaces

FMC C MGT Lanes:

| FMC | MGT Lane | Bank | Type | Signal Schematic Name | FMC Connector Pin | FPGA Pin |

|---|---|---|---|---|---|---|

J8 (FMC C) | 3 | 230 | GTH |

| J8-C6 | MGTHRXP3_230, A4 |

| 2 | 230 | GTH |

| J8-A2 | MGTHRXP2_230, B2 | |

| 1 | 230 | GTH |

| J8-A6 | MGTHRXP1_230, C4 | |

| 0 | 230 | GTH |

| J8-A10 | MGTHRXP0_230, D2 |

Table 19: FMC C connector MGT lanes

FMC C Clock Signals:

| FMC | Signal Schematic Name | Bank | FMC Connector Pin | FPGA Pin | Notes |

|---|---|---|---|---|---|

J8 (FMC C) |

| 230 | J8-D4 | MGTREFCLK0P_230, C8 | Supplied by attached module |

| 50 HD | J8-H4 | IO_L7P_HDGC_50, J12 | Supplied by attached module | |

| 50 HD | J8-G2 | IO_L8P_HDGC_50, H13 | Supplied by attached module |

Table 20: FMC C connector clock signal input

FMC C VCC/VCCIO:

| FMC | Available VCC/VCCIO | FMC Connector Pin | Source | Notes |

|---|---|---|---|---|

J8 (FMC C) | FMCC_3V3 | J8-D36 | DCDC U34, | Enable by SC CPLD U27, bank 0, pin E11 |

| 3V3SB | J8-D32 | DCDC U50, max. cur.: 1A | not dedicated for FMC connectors | |

| 12V | J8-C35 | DCDC U82, | not dedicated for FMC connectors | |

| FMCBC_1V8 | J8-H40 | DCDC U40, | Enable by SC CPLD U27, bank 0, pin A3 |

Table 21: FMC C connector available VCC/VCCIO

FMC C Cooling Fan:

| FMC | Fan Designator | Enable Signal | Notes |

|---|---|---|---|

J8 (FMC C) | M3 | Enable by SC CPLD U27, bank 0, pin B3 | - |

Table 22: FMC C connector cooling fan

Anchor FMC D FMC D

FMC D

FMC D Interfaces:

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes |

|---|---|---|---|---|---|---|

J7 (FMC D) | I/O | 20 | 10 | Bank 65 HP | FMCDE_1V8 | - |

| 48 | 24 | Bank 66 HP | FMCDE_1V8 | - | ||

| I²C | 2 | - | I²C-Switch U13 | - | Muxed to MIO Bank 501 I²C Inteface | |

| JTAG | 4 | - | SC CPLD U27 Bank 2 | 3.3VSB | - | |

| MGT | - | 8 (4 x RX/TX) | Bank 229 GTH | - | 4x MGT lanes | |

| Clock Input | - | 2 | Bank 65 HP | - | 2x Reference clock inputs to PL bank | |

| - | 1 | Bank 229 GTH | - | 1x Reference clock input to MGT bank | ||

| Control Signals | 3 | - | SC CPLD U27 Bank 2 | 3.3VSB | 'FMCD_PG_C2M', 'FMCD_PG_M2C', 'FMCD_PRSNT' |

Table 23: FMC D connector interfaces

FMC D MGT Lanes:

| FMC | MGT Lane | Bank | Type | Signal Schematic Name | FMC Connector Pin | FPGA Pin |

|---|---|---|---|---|---|---|

J7 (FMC D) | 3 | 229 | GTH |

| J7-C6 | MGTHRXP3_229, F2 |

| 2 | 229 | GTH |

| J7-A2 | MGTHRXP2_229, H2 | |

| 1 | 229 | GTH |

| J7-A6 | MGTHRXP1_229, J4 | |

| 0 | 229 | GTH |

| J7-A10 | MGTHRXP0_229, K2 |

Table 24: FMC D connector MGT lanes

FMC D Clock Signals:

| FMC | Signal Schematic Name | Bank | FMC Connector Pin | FPGA Pin | Notes |

|---|---|---|---|---|---|

J7 (FMC D) |

| 229 | J7-D4 | MGTREFCLK0P_229, G8 | Supplied by attached module |

| 65 HP | J7-H4 | IO_L14P_T2L_N2_GC_65, AG5 | Supplied by attached module | |

| 65 HP | J7-G2 | IO_L13P_T2L_N0_GC_QBC_65, AE5 | Supplied by attached module |

Table 25: FMC D connector clock signal input

FMC D VCC/VCCIO:

| FMC | Available VCC/VCCIO | FMC Connector Pin | Source | Notes |

|---|---|---|---|---|

J7 (FMC D) | FMCD_3V3 | J7-D36 | DCDC U35, | Enable by SC CPLD U27, bank 0, pin F8 |

| 3V3SB | J7-D32 | DCDC U50, max. cur.: 1A | not dedicated for FMC connectors | |

| 12V | J7-C35 | DCDC U82, | not dedicated for FMC connectors | |

| FMCDE_1V8 | J7-H40 | DCDC U41, | Enable by SC CPLD U27, bank 0, pin C5 |

Table 26: FMC D connector available VCC/VCCIO

FMC D Cooling Fan:

| FMC | Fan Designator | Enable Signal | Notes |

|---|---|---|---|

J7 (FMC D) | M4 | Enable by SC CPLD U27, bank 0, pin D7 | - |

Table 27: FMC D connector cooling fan

Anchor FMC E FMC E

FMC E

FMC E Interfaces:

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes |

|---|---|---|---|---|---|---|

J6 (FMC E) | I/O | 24 | 12 | Bank 65 HP | FMCDE_1V8 | - |

| 44 | 22 | Bank 64 HP | FMCDE_1V8 | - | ||

| I²C | 2 | - | I²C-Switch U13 | - | Muxed to MIO Bank 501 I²C Inteface | |

| JTAG | 4 | - | SC CPLD U27 Bank 2 | 3.3VSB | - | |

| MGT | - | 8 (4 x RX/TX) | Bank 228 GTH | - | 4x MGT lanes | |

| Clock Input | - | 2 | Bank 64 HP | - | 2x Reference clock inputs to PL bank | |

| - | 1 | Bank 228 GTH | - | 1x Reference clock input to MGT bank | ||

| Control Signals | 3 | - | SC CPLD U27 Bank 2 | 3.3VSB | 'FMCE_PG_C2M', 'FMCE_PG_M2C', 'FMCE_PRSNT' |

Table 28: FMC E connector interfaces

FMC E MGT Lanes:

| FMC | MGT Lane | Bank | Type | Signal Schematic Name | FMC Connector Pin | FPGA Pin |

|---|---|---|---|---|---|---|

J6 (FMC E) | 3 | 228 | GTH |

| J6-C6 | MGTHRXP3_228, L4 |

| 2 | 228 | GTH |

| J6-A2 | MGTHRXP2_228, M2 | |

| 1 | 228 | GTH |

| J6-A6 | MGTHRXP1_228, P2 | |

| 0 | 228 | GTH |

| J6-A10 | MGTHRXP0_228, T2 |

Table 29: FMC E connector MGT lanes

FMC E Clock Signals:

| FMC | Signal Schematic Name | Bank | FMC Connector Pin | FPGA Pin | Notes |

|---|---|---|---|---|---|

J6 (FMC E) |

| 228 | J6-D4 | MGTREFCLK0P_228, L8 | Supplied by attached module |

| 64 HP | J6-H4 | IO_L12P_T1U_N10_GC_64, AL8 | Supplied by attached module | |

| 64 HP | J6-G2 | IO_L11P_T1U_N8_GC_64, AK8 | Supplied by attached module |

Table 30: FMC E connector clock signal input

FMC E VCC/VCCIO:

| FMC | Available VCC/VCCIO | FMC Connector Pin | Source | Notes |

|---|---|---|---|---|

J6 (FMC E) | FMCE_3V3 | J6-D36 | DCDC U36, | Enable by SC CPLD U27, bank 0, pin E8 |

| 3V3SB | J6-D32 | DCDC U50, max. cur.: 1A | not dedicated for FMC connectors | |

| 12V | J6-C35 | DCDC U82, | not dedicated for FMC connectors | |

| FMCDE_1V8 | J6-H40 | DCDC U41, | Enable by SC CPLD U27, bank 0, pin C5 |

Table 31: FMC E connector available VCC/VCCIO

FMC E Cooling Fan:

| FMC | Fan Designator | Enable Signal | Notes |

|---|---|---|---|

J6 (FMC E) | M5 | Enable by SC CPLD U27, bank 0, pin D6 | - |

Table 32: FMC E connector cooling fan

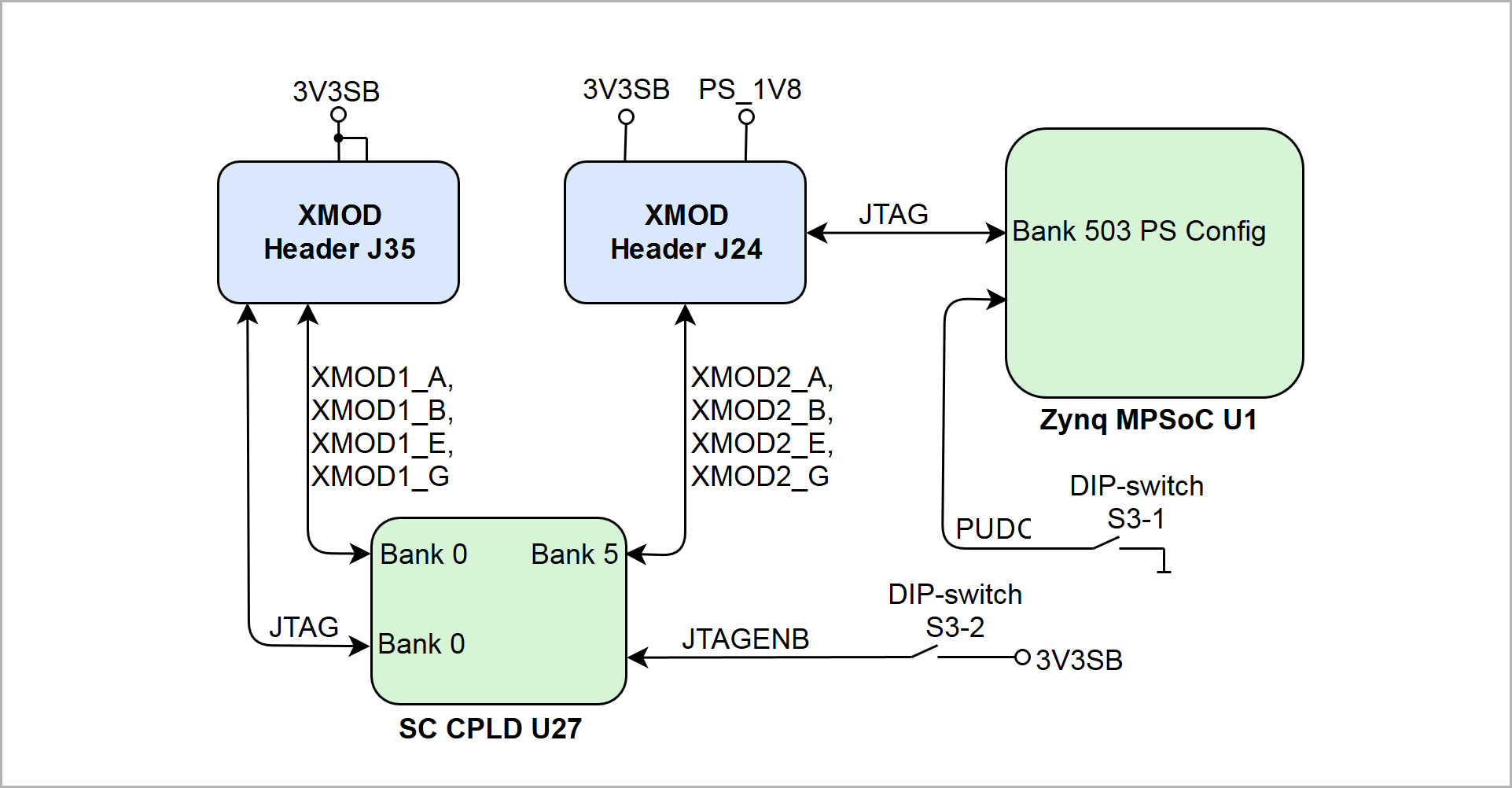

XMOD JTAG Interface

JTAG access to the Zynq MPSoC and SC CPLD is provided through XMOD header J24 and J35:

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

Signal Assignment of XMOD header J24 and J35

...

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

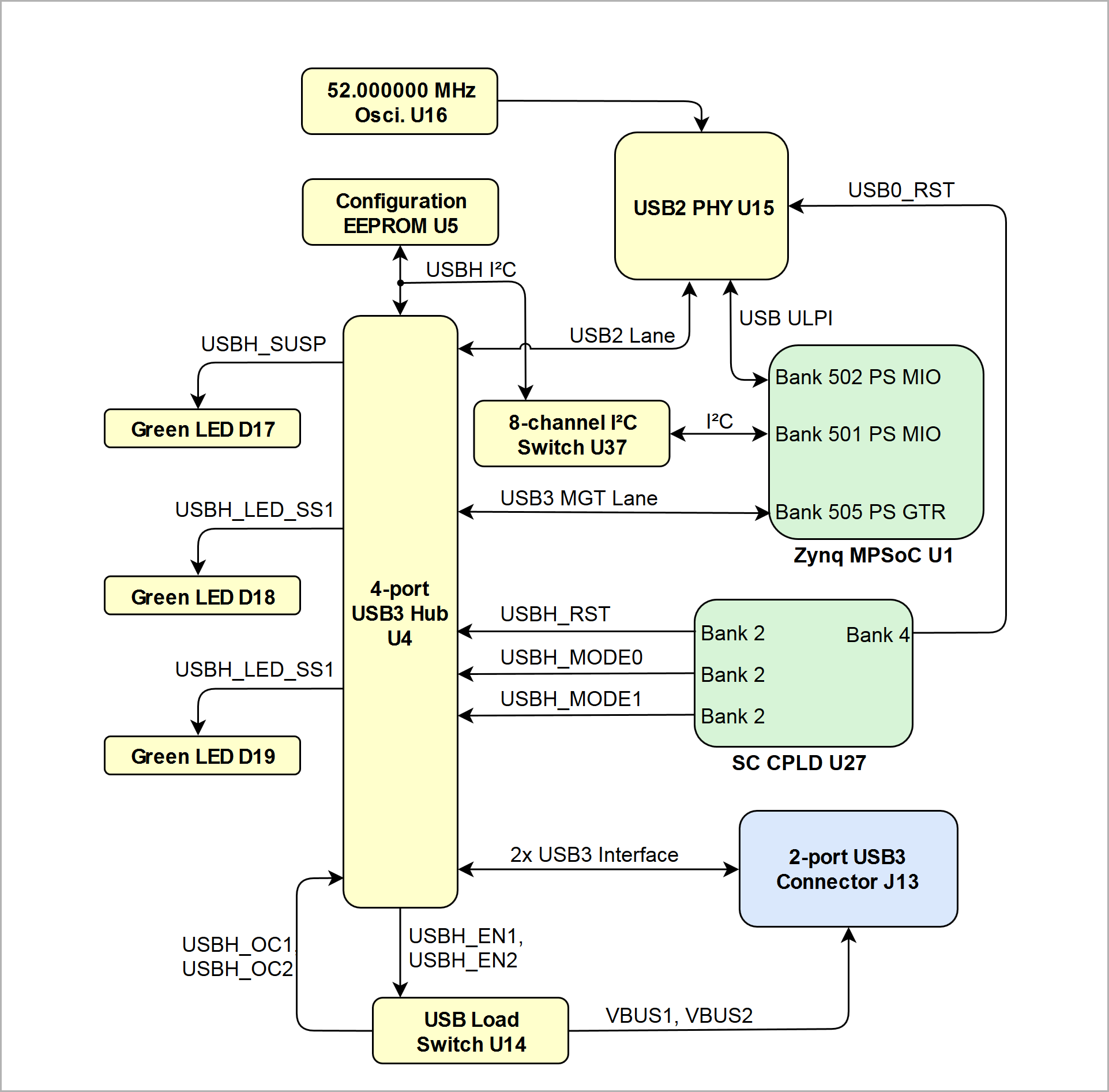

The 4-port USB3 hub is connected to the Zynq MPSoC's PS GTR bank, the USB2 PHY is connected to the PS MIO bank 502:

...

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

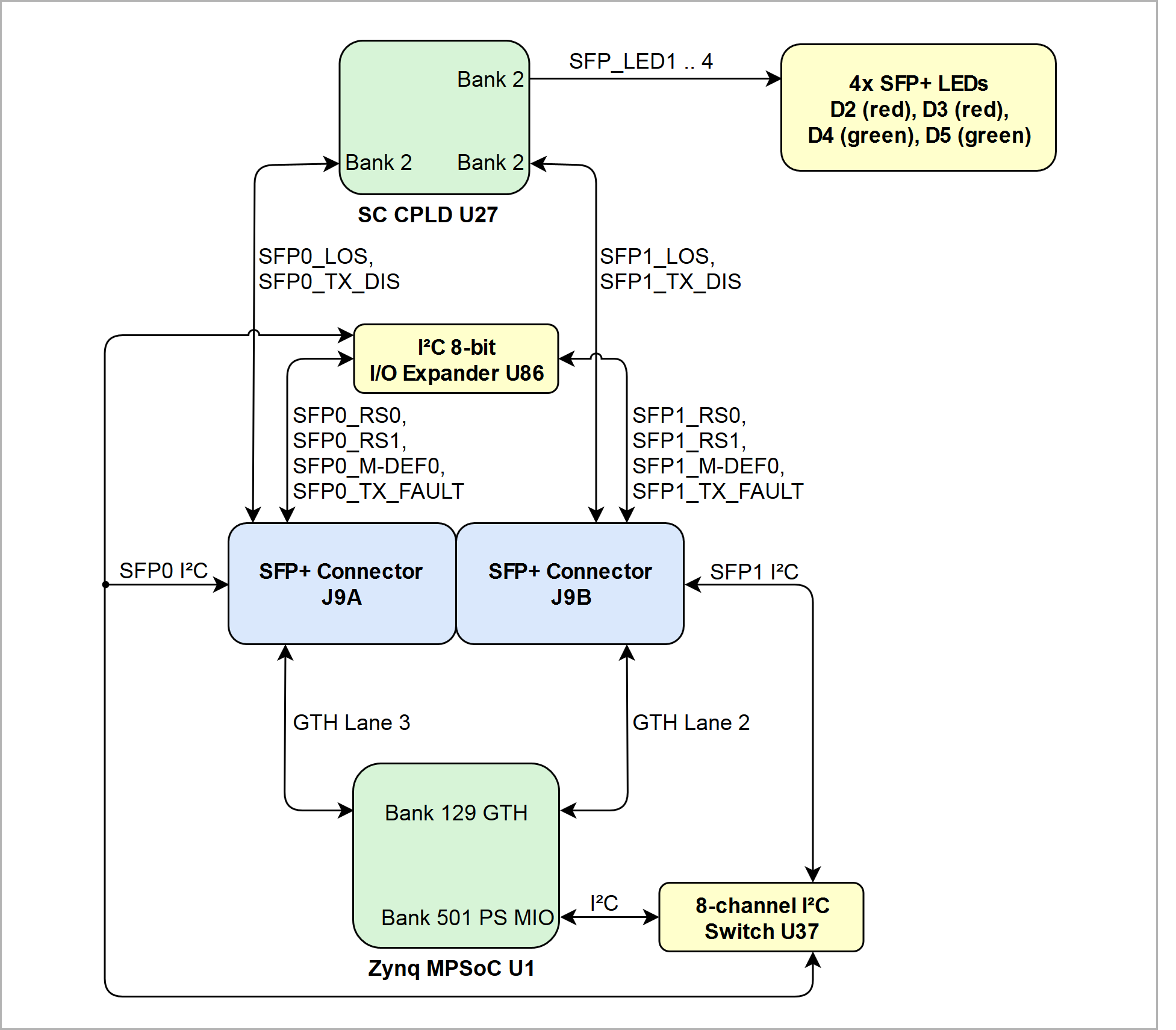

| Connector | Interface | Signal Schematic Name | Connected to | Logic | Notes |

|---|---|---|---|---|---|

SFP+ J9A | MGT Lane |

| MGTHTXP3_129, G31 | TX: Output RX: Input | Multi gigabit highspeed data lane |

| I²C |

| 8-channel I²C-switch U37 | BiDir | 2-wire Serial Interface | |

| Control Lines |

| I²C 8-bit I/O Port-Expander U86 | Output, low active | Full RX bandwidth | |

| Output, low active | Reduced RX bandwidth | |||

| Input, low active | Module present / not present | |||

| Input, high active | Fault / Normal Operation | |||

| SC CPLD U27, bank 2, pin V8 | Input, high active | Loss of receiver signal | ||

| SC CPLD U27, bank 2, pin Y7 | Output, low active | SFP Enabled / Disabled | ||

SFP+ J9B | MGT Lane |

| MGTHTXP2_129, H29 | TX: Output RX: Input | Multi gigabit highspeed |

| I²C |

| 8-channel I²C-switch U37 | Bidir | 2-wire Serial Interface | |

| Control Lines |

| I²C 8-bit I/O Port-Expander U86 | Output, low active | Full RX bandwidth | |

| Output, low active | Reduced RX bandwidth | |||

| Input, low active | Module present / not present | |||

| Input, high active | Fault / Normal Operation | |||

| SC CPLD U27, bank 2, pin W7 | Input, high active | Loss of receiver signal | ||

| SC CPLD U27, bank 2, pin V7 | Output. low active | SFP Enabled / Disabled |

...

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

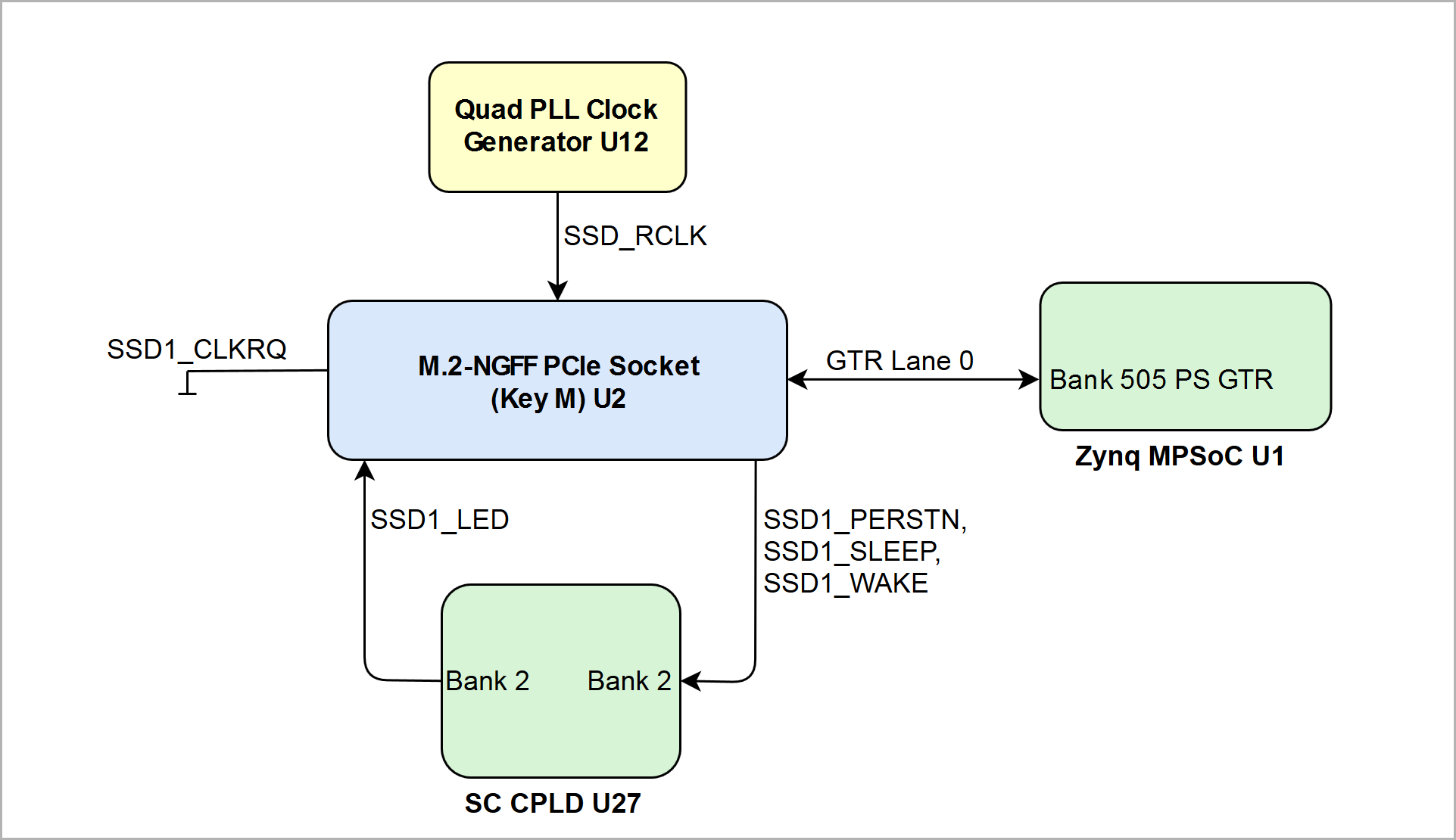

| Connector | Interface | Signal Schematic Name | Connected to | Notes |

|---|---|---|---|---|

M.2-NGFF PCIe Socket U2 | MGT Lane |

| PS_MGTRTXP0_505, AB29 | Multi gigabit highspeed TX: Output RX: Input |

| Clock Input |

| Quad programmable PLL clock generator U12, CLK0 | Reference clock signal | |

| Control Lines |

| SC CPLD U27, bank 2, pin AA13 | LED, Output, High active | |

| SC CPLD U27, bank 2, pin AA12 | PCIe sleep state, Input, Low active | ||

| SC CPLD U27, bank 2, pin AA11 | PCIe reset, Input, Low active | ||

| SC CPLD U27, bank 2, pin AB11 | PCIe Link reactivation, Input, Low active | ||

| connect to GND | PCIe Clock Request, Low active |

...

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

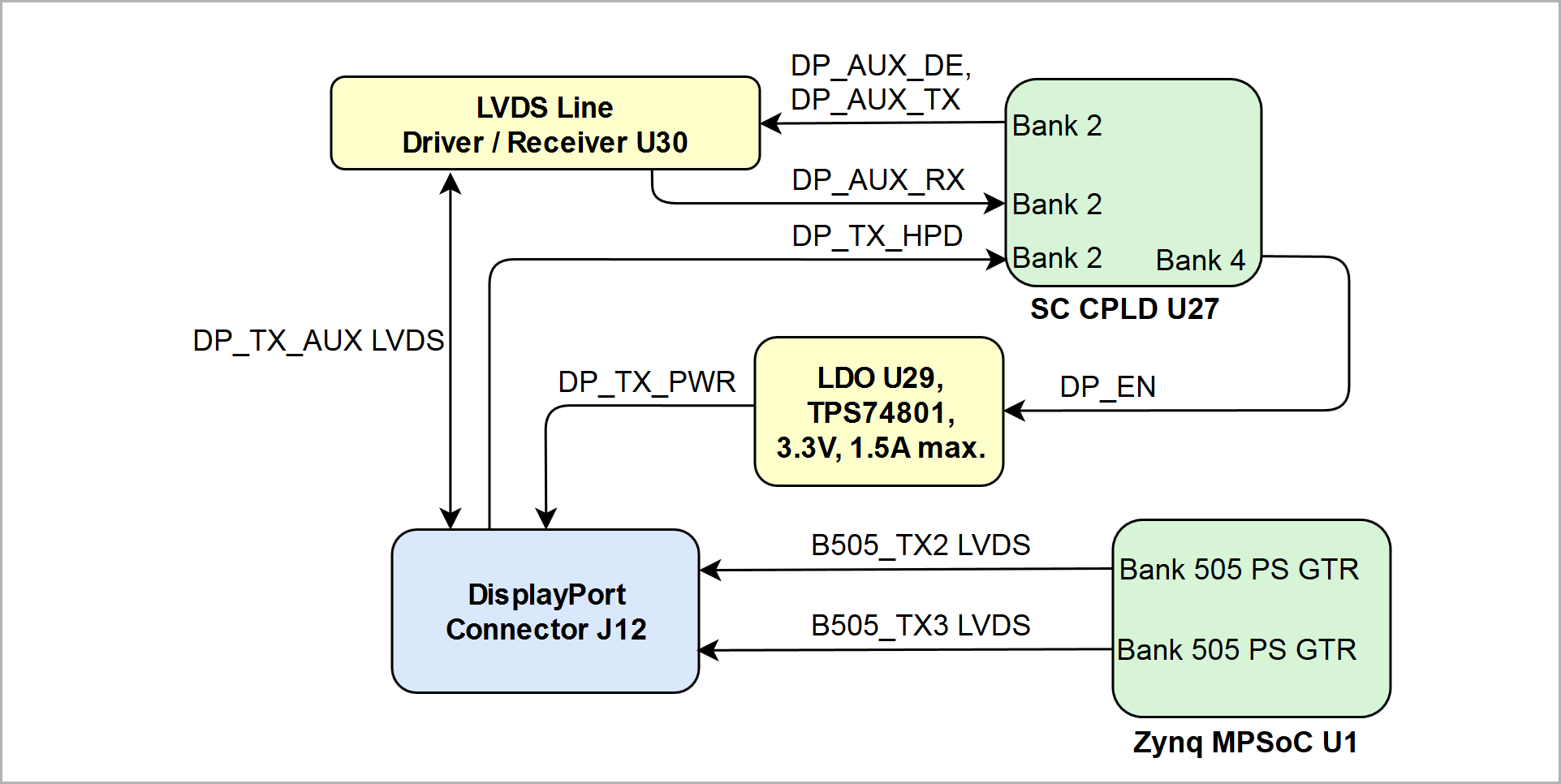

Follwowing table contains a brief description of the MGT lanes and control and status signals of the DisplayPort interface:

...

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

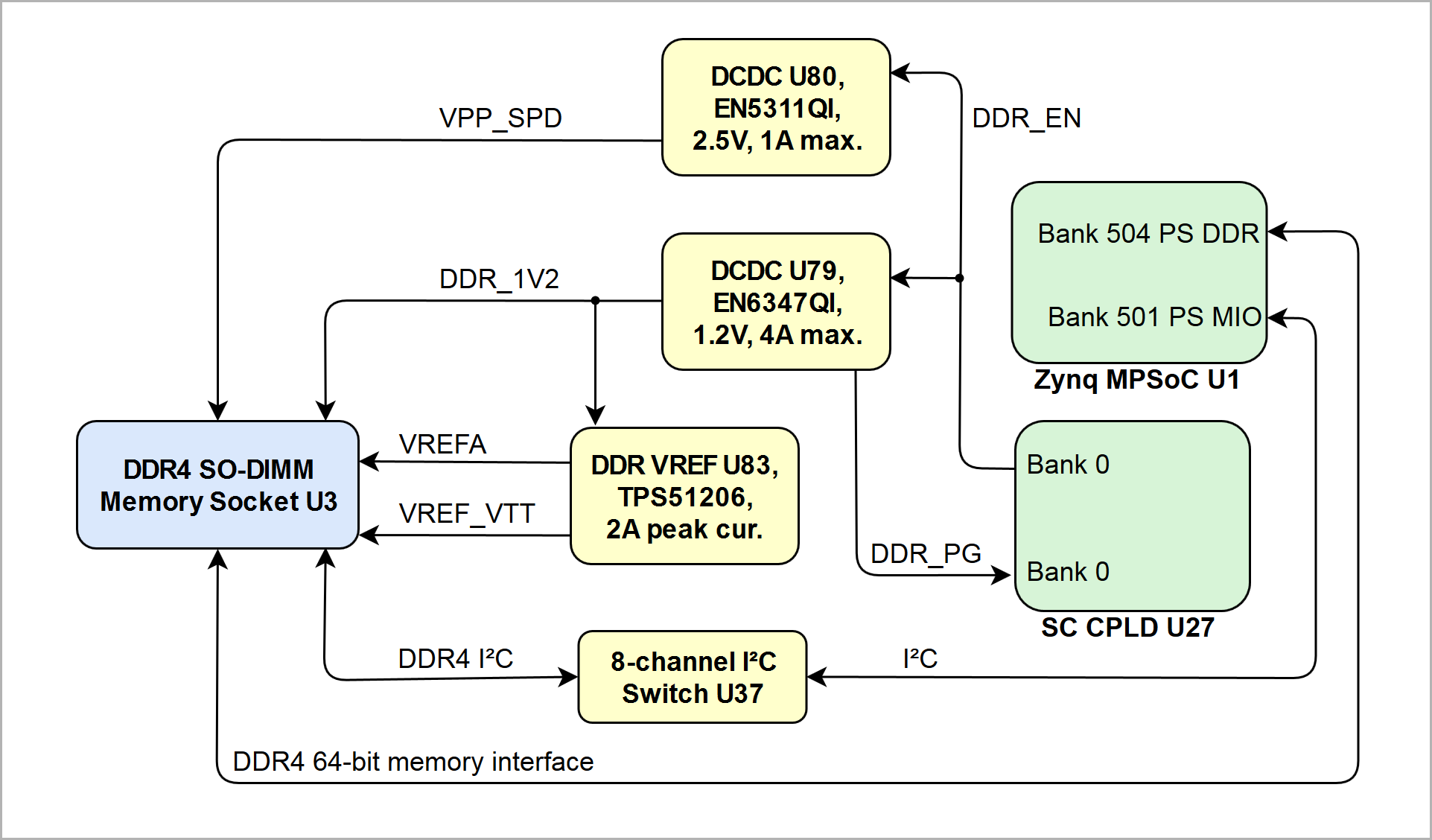

Following table gives an overview about the I/O signals of the DDR4 SDRAM memory interface:

| Connector | DDR4 SDRAM I/O Signal | Signal Schematic Name | Connected to | Notes |

|---|---|---|---|---|

DDR4 SO-DIMM Socket U13 | Address inputs |

| PS DDR Bank 504 | - |

| Bank address inputs |

| - | ||

| Bank group inputs |

| - | ||

| Differential clocks |

| 2 x DDR4 clock | ||

| Data input/output |

| - | ||

| Check bit input/output |

| - | ||

| Data strobe (differential) |

| - | ||

| Data mask and data bus inversion |

| - | ||

| Serial address inputs |

| address range configuration on I²C bus | ||

| Control Signals |

| chip selest signal | ||

| On-die termination enable | |||

| nRESET | |||

| Command and address parity input | |||

| Clock enable | |||

| CRC error flag | |||

| Activation command input | |||

| Temperature event | |||

| I²C |

| 8-channel I²C switch U37 | - |

Table 40: DDR4 64-bit memory interface signals and pins

Refer to the Xilinx Zynq UltraScale+ datasheet DS925 for more information on whether the specific package of the Zynq UltraScale+ MPSoC supports the maximum data transmission rate of 2400 MByte/s, which also depends on the used SO-DIMM module.

...

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

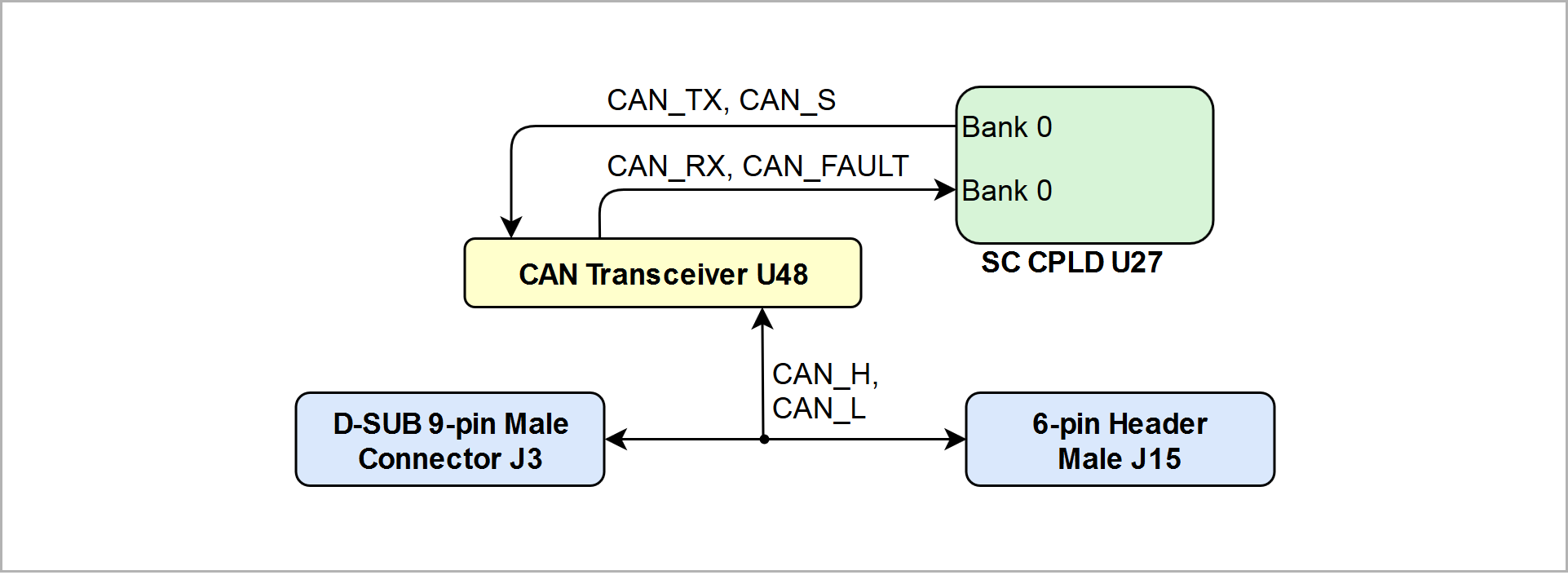

The CAN interface of external devices can be connected via D-SUB 9-pin male connector J3 or to the 6-pin male header J15:

| Connector | Signal Schematic Name | Connected to | Notes |

|---|---|---|---|

D-SUB 9-pin J3 |

| CAN Transceiver U48, pin 7 | - |

| CAN Transceiver U48, pin 6 | - | |

6-pin male header J15 |

| CAN Transceiver U48, pin 7 | - |

| CAN Transceiver U48, pin 6 | - | |

| CAN Transceiver | Signal Schematic Name | Connected to | Notes |

| TCAN337 U48 |

| SC CPLD U27, bank 0, pin C16 | 3.3V VCCIO |

| SC CPLD U27, bank 0, pin B15 | 3.3V VCCIO | |

| SC CPLD U27, bank 0, pin C15 | 3.3V VCCIO | |

| SC CPLD U27, bank 0, pin D15 | 3.3V VCCIO |

Table 41: CAN interface signals and pins

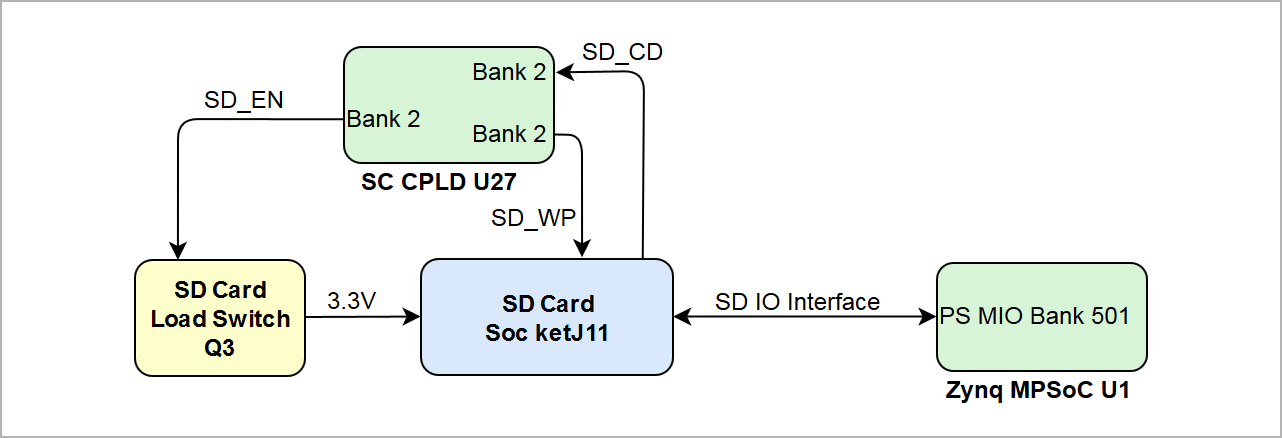

SD Card Interface

The SD Card interface of the TEB0911 board is routed via SD IO interface to the PS MIO bank 501 of the Zynq Ultrascale+ MPSoC (3.3V VCCO). The SC CPLD U27 controls the load switch Q3 to enable the card sockets J11 with signal 'SD_EN', bank 2, pin U11. The "Card Detect" and "Write Protect" signal are also routed to the SC CPLD:

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

The SD Card socket have following signal and pin assignment:

...

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

| Connector | Signal Schematic Name | Connected to | Notes |

|---|---|---|---|

Pin Header J22 |

| clock generator U17, pin 16 | PS_1V8 VCCIO |

| clock generator U17, pin 18 | ||

SMA Coax J25 |

| clock generator U17, pin 1 | - |

Table 44: Clock generator Si5345A external interfaces

On-board Peripherals

| HTML |

|---|

<!-- Components on the Module, like Flash, PLL, PHY... --> |

...

Table 65: Module hardware revision history

Hardware revision number can be found on the PCB board together with the board model number separated by the dash.

...

| HTML |

|---|

<!-- Generate new entry: 1.add new row below first 2.Copy "Page Information Macro(date)" Macro-Preview, Metadata Version number, Author Name and description to the empty row. Important Revision number must be the same as the Wiki document revision number 3.Update Metadata = "Page Information Macro (current-version)" Preview+1 and add Author and change description. --> |

Date | Revision | Contributors | Description | ||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||||||

| 2019-08-27 | v.184 | John Hartfiel |

| ||||||||||||||||||||||||||

| 2019-05-10 | v.183 | John Hartfiel |

| ||||||||||||||||||||||||||

| 2018-07-23 | v.182 | Ali Naseri |

| ||||||||||||||||||||||||||

| -- | all |

|

Table 66: Document change history

...