Page History

...

| Section | ||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||

...

RGPIO_EXT External Interface

Communication channel between master and slave interface.

| Port Name | IO | Description |

|---|---|---|

| RGPIO_M_CLK | out | RGPIO Master Clock |

| RGPIO_M_RX | in | RGPIO Master RXD |

| RGPIO_M_TX | out | RGPIO Master TXD |

| Port Name | IO | Description |

|---|---|---|

| RGPIO_S_CLK | out | RGPIO Slave Clock |

| RGPIO_S_RX | in | RGPIO Slave RXD |

| RGPIO_S_TX | out | RGPIO Slave TXD |

RGPIO_M_USR Interface

Master user interface to communicate with slave device.

| Port Name | IO | Description |

|---|---|---|

| RGPIO_M_OUT | out | Data 23bit data output to slave device* |

| RGPIO_M_IN | in | Data 23bit data input from slave device* |

| RGPIO_M_RESERVED_OUT | out | Reserved 4bit reserved for future usage |

| RGPIO_M_RESERVED_IN | in | Reserved 4bit reserved for future usage |

| RGPIO_M_SLAVE_ACTIVATION_CODE | out | Activation 4bit activation code from external slave for information only |

| RGPIO_M_ENABLE | in | Enable RGPIO communication. High active. Set RGPIO data as valid for Slave. Data will always transmitted, if CLK is available. |

| RGPIO_M_USRCLK | in | RGPIO transmission CLK for master and slave |

| RGPIO_M_RESET_N | in | RGPIO Reset. Low active. |

*currently limited to 23 bit to use IP with CPLD implementations of TE Boards. For general usage, this restriction will be removed on future IP update.

RGPIO_

...

S_USR Interface

Slave user interface to communicate with master device.

| Port Name | IO | Description |

|---|---|---|

| RGPIO_S_OUT | out | Data 23bit data output to master device* |

| RGPIO_S_IN | in | Data 23bit data input from master device* |

| RGPIO_S_RESERVED_OUT | out | Reserved 4bit reserved for future usage |

| RGPIO_S_RESERVED_IN | in | Reserved 4bit reserved for future usage |

| RGPIO_S_MASTER_ACTIVATION_CODE | out | Activation 4bit activation code from external master for information only |

| RGPIO_S_ENABLED | out | Interface status. Indicates RGPIO data are valid. |

*currently limited to 23 bit to use IP with CPLD implementations of TE Boards. For general usage, this restriction will be removed on future IP update.

Designing with the Core

This chapter includes guidelines and additional information to facilitate designing with the core.

...

There is no example Design for this IP core release.

Use Master Slave loopback over RGPIO_EXT interface to test IP Master and Slave Interface together.

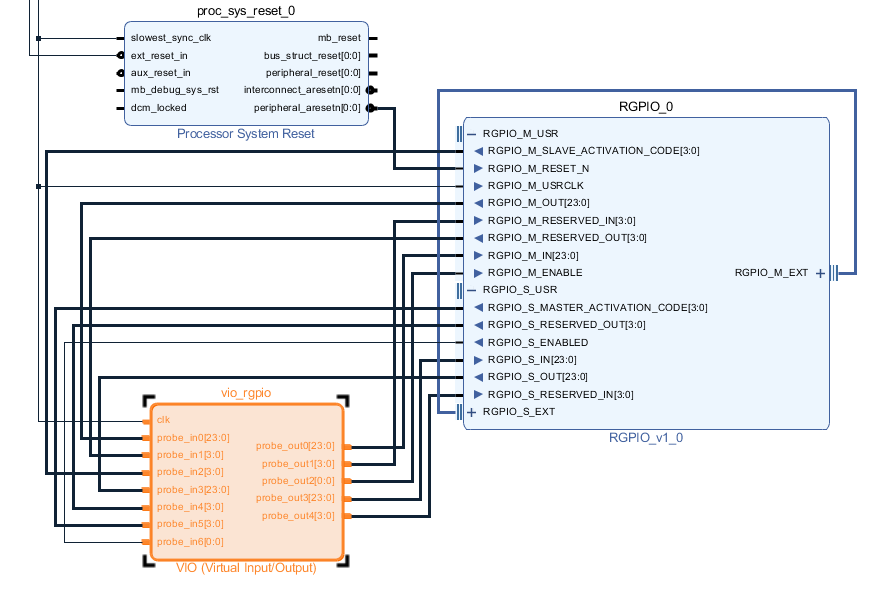

Vivado Block Design:

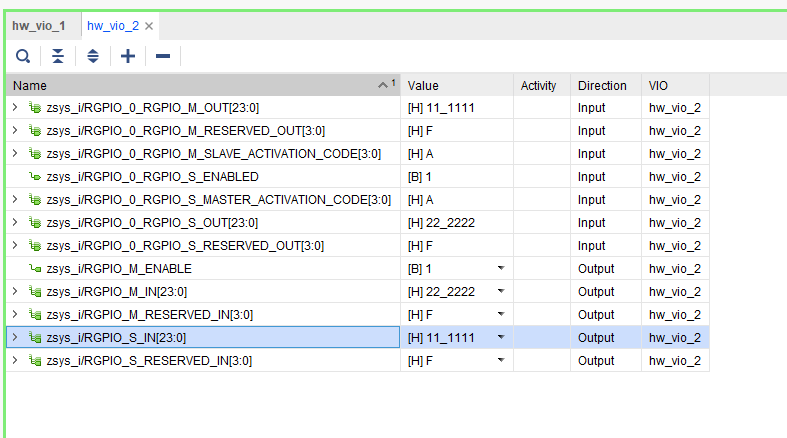

VIO HW Manager:

Test Bench

There is no test bench for this IP core release.

...

Document Change History

| Date | Document Revision | IP Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| v1.0 |

|

|

Legal Notices

| Include Page | ||||

|---|---|---|---|---|

|

...