...

| Scroll Title |

|---|

| anchor | Table_DRH |

|---|

| title | Design Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Vivado | Project Built | Authors | Description |

|---|

| 2019-09-18 | 2018.2 | TE0745-IBERT_noprebuilt-vivado_2018.2-build_04_20190918103506.zip

TE0745-IBERT-vivado_2018.2-build_04_20190918103450.zip | John Hartfiel | - bugfix for TE0745-02-45-3EA board parts

| | 2018-12-19 | 2018.2 | TE0745-IBERT_noprebuilt-vivado_2018.2-build_04_20181219143313.zip

TE0745-IBERT-vivado_2018.2-build_04_20181219143258.zip | John Hartfiel | |

|

...

For general structure and of the reference design, see Project Delivery - AMD devices

Design Sources

| Scroll Title |

|---|

| anchor | Table_DS |

|---|

| title | Design sources |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Type | Location | Notes |

|---|

| Vivado | <design name>/block_design

<design name>/constraints

<design name>/ip_lib

<design name>/hdl | Vivado Project will be generated by TE Scripts | | SDK/HSI | <design name>/sw_lib | Additional Software Template for SDK/HSI and apps_list.csv with settings for HSI |

|

...

Reference Design is available on:

Design Flow

...

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

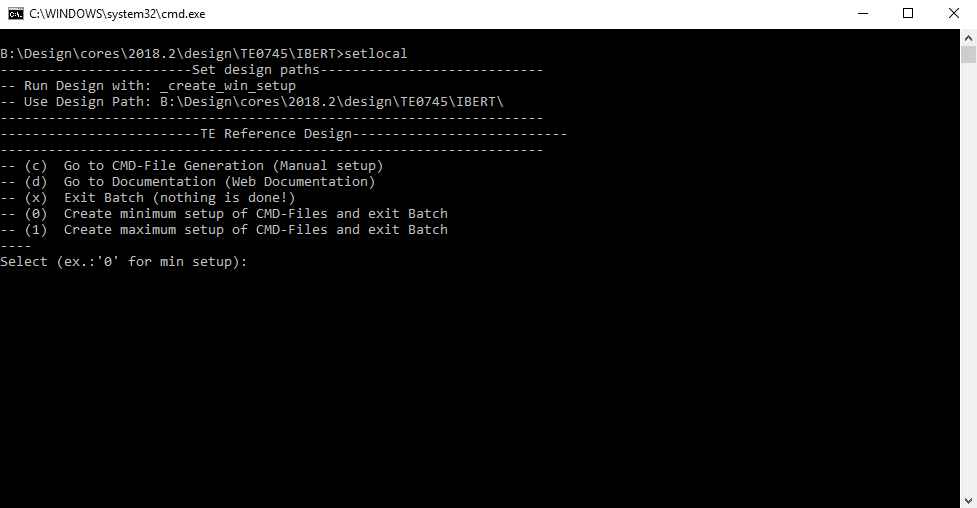

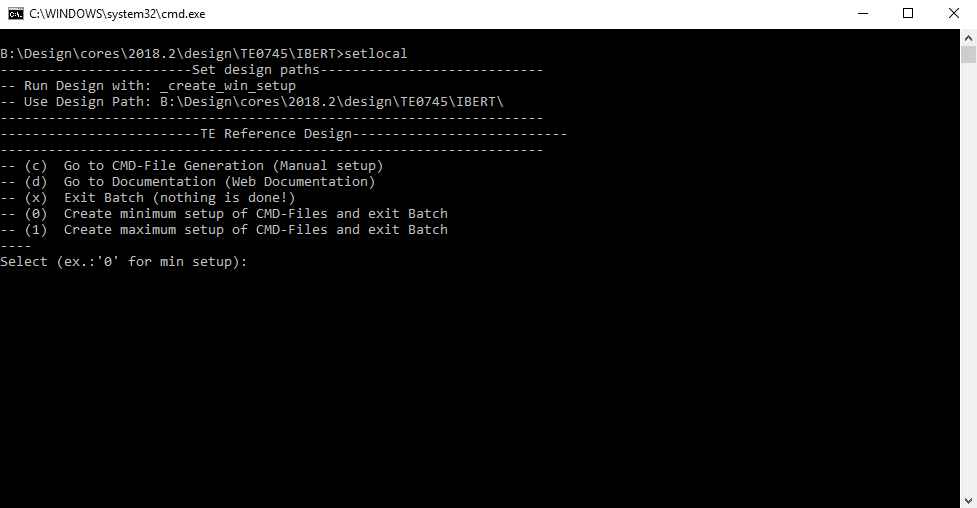

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter for minimum setup

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Generate Programming Files with HSI/SDK

- Run on Vivado TCL: TE::sw_run_hsi

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk

Note: See SDK Projects

...

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

QSPI

Optional for Boot.bin on QSPI Flash and image.ub on SD.

...

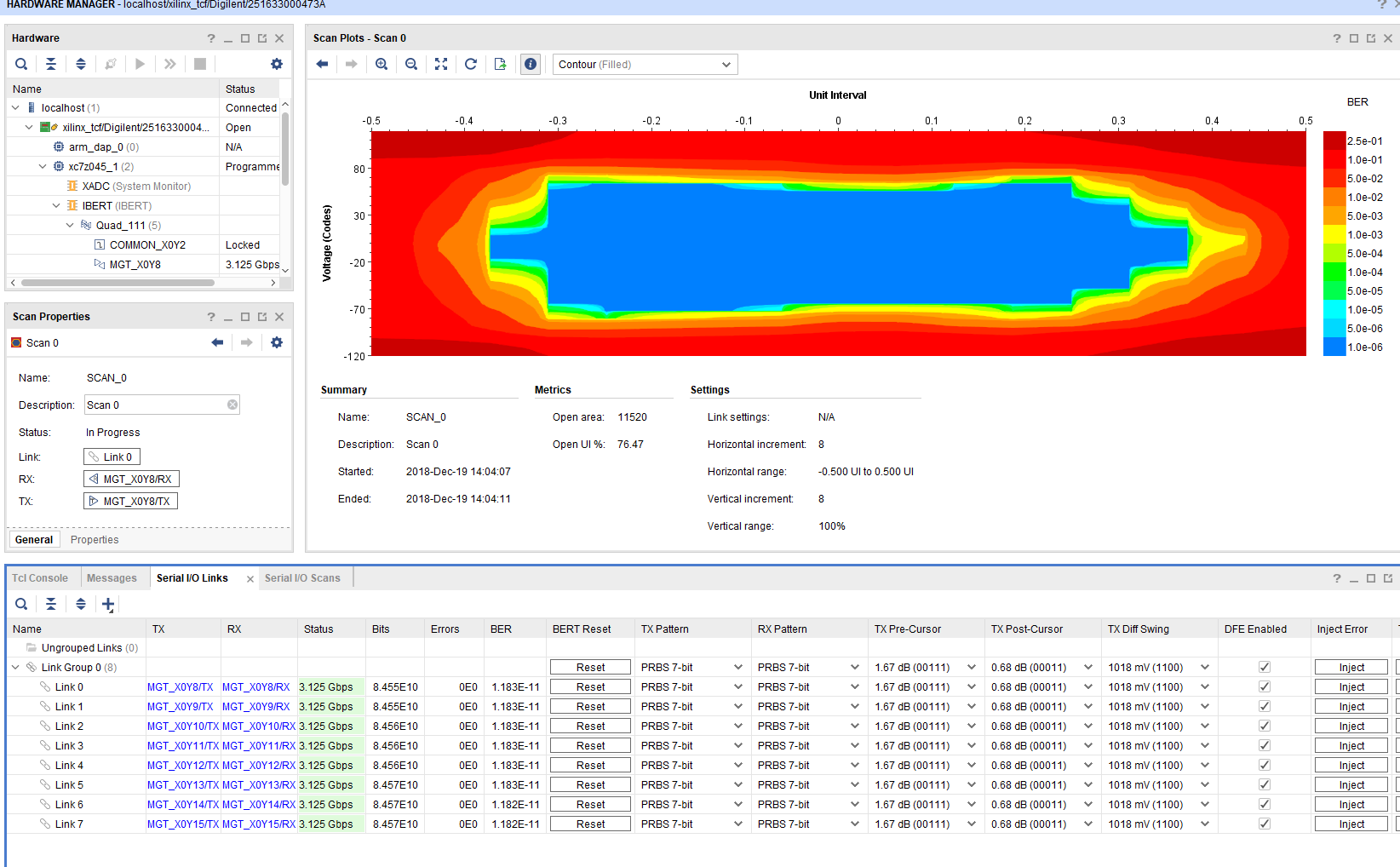

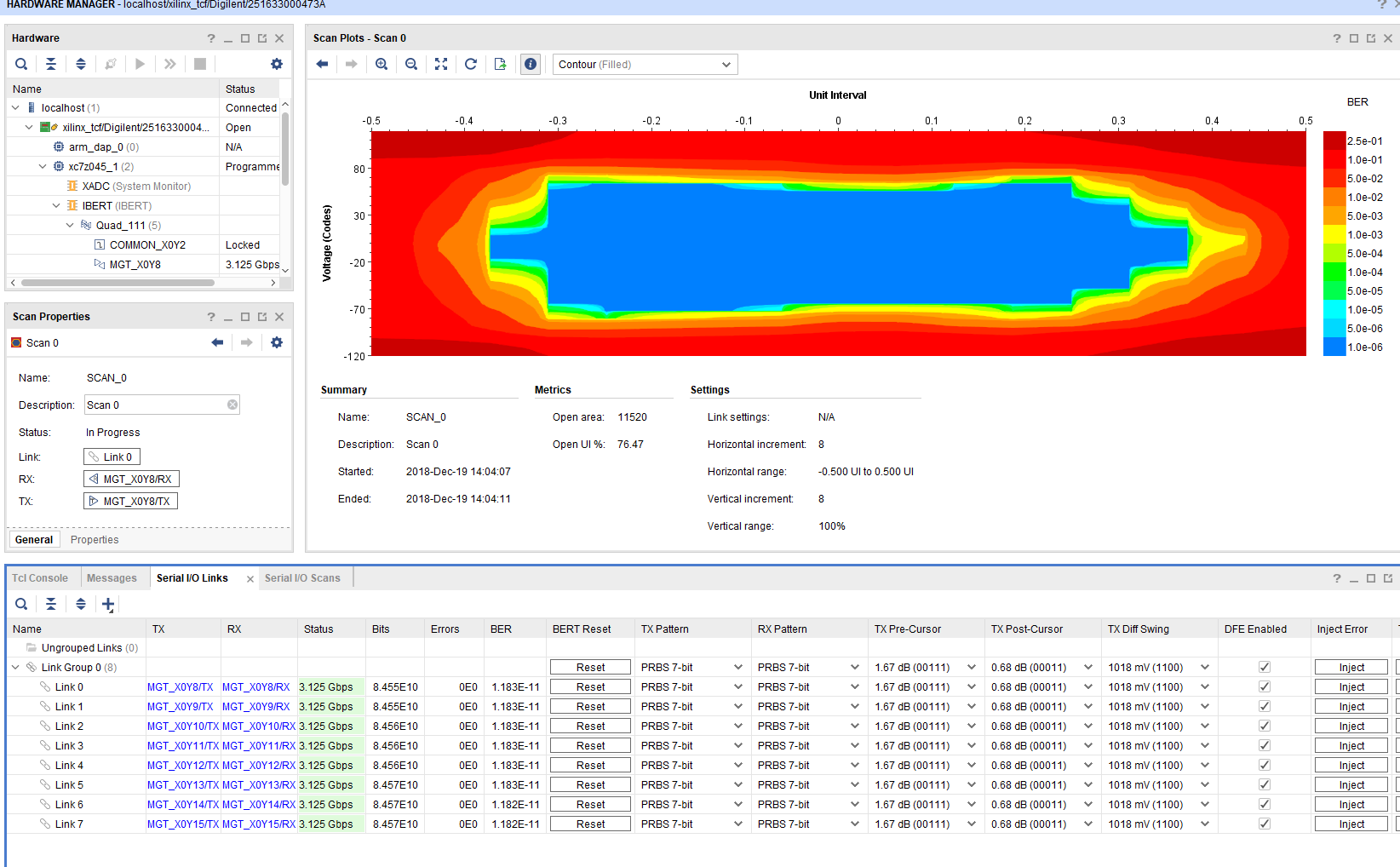

| Scroll Title |

|---|

| anchor | Figure_VHM |

|---|

| title | Vivado Hardware Manager |

|---|

|

|

| IBERT MGT ( on Z045 / on Z030 ) | TE0745 Xil Symb | TE0745 Schem Name | TEB0745 SFP Designator |

|---|

X0Y8 | MGT0_111 | MGT_ |

RX4| RX/TX4 | J20/21 |

| X0Y9 | MGT1_111 | MGT_ |

RX5| RX/TX5 | J18/19 |

| X0Y10 | MGT2_111 | MGT_ |

RX6| RX/TX6 | J15/17 |

| X0Y11 | MGT3_111 | MGT_ |

RX7| RX/TX7 | J13/14 |

| X0Y12 / X0Y0 | MGT0_112 | MGT_ |

RX0| RX/TX0 | J10/11 |

| X0Y13 / X0Y1 | MGT1_112 | MGT_ |

RX1| RX/TX1 | J8/9 |

| X0Y14 / X0Y2 | MGT2_112 | MGT_ |

RX2| RX/TX2 | J6/7 |

| X0Y15 / X0Y3 | MGT3_112 | MGT_ |

RX3System Design - Vivado

...

| Page properties |

|---|

|

Note:

- Add description for other Software, for example SI CLK Builder ...

- SI5338 and SI5345 also Link to:

|

No additional software is needed.

SI5338

File location <design name>/misc/Si5338/RegisterMap.txt

...

| Scroll Title |

|---|

| anchor | Table_dch |

|---|

| title | Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | 2*,*,3*,4* |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Document Revision | Authors | Description |

|---|

| Page info |

|---|

| infoType | Modified | modified-date | modified- date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| - IBERT Mapping Table add Z030 Names

| | 2019-09-18 | v.4 | John Hartfiel | - bugfix for TE0745-02-45-3EA

| | 2018-12-19 | v.2 | John Hartfiel | | | -- | all | | Page info |

|---|

| infoType | Modified users |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| -- |

|

...