Page History

Template Revision 2.6 - on construction

| HTML |

|---|

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

...

| hidden | true |

|---|---|

| id | Comments |

Important General Note:

...

Export PDF to download, if vivado revision is changed!

Designate all graphics and pictures with a number and a description, Use "Scroll Title" macro

...

Figure template (note: inner scroll ignore/only only with drawIO object):

...

| anchor | Figure_xyz |

|---|---|

| title | Text |

| Scroll Ignore |

|---|

Create DrawIO object here: Attention if you copy from other page, use |

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

...

Table template:

- Layout macro can be use for landscape of large tables

- Set column width manually(can be used for small tables to fit over whole page) or leave empty (automatically)

...

| anchor | Table_xyz |

|---|---|

| title | Text |

...

| Scroll pdf ignore | ||||

|---|---|---|---|---|

Table of contents

|

Overview

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Design Example with minimum PS Setup (DDR, QSPI, UART0) only for custom boards or easier debug via SDK.

Refer to http://trenz.org/te0808-info for the current online version of this manual and other available documentation.

Key Features

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Excerpt |

|---|

|

Revision History

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| anchor | Table_DRH |

|---|---|

| title | Design Revision History |

...

- new assembly variants

...

- custom FSBL

...

- additional notes for FSBL generated with Win SDK

- changed *.bif

...

- new assembly variant

...

- Update Board Part for TEBF0808

- no changes for test board design and minimal board parts

...

- rework Board Part Files

...

TE0808-test_board-vivado_2017.2-build_07_20171220192501.zip

TE0808-test_board_noprebuilt-vivado_2017.2-build_07_20171220192448.zip

...

- Update Board Part Files

...

- Update Board Part CSV File

- Regenerate design

...

TE0808-test_board-vivado_2017.2-build_05_20171116151545.zip

TE0808-test_board_noprebuilt-vivado_2017.2-build_05_20171116151600.zip

...

- Update Board Part CSV File with new Flash assembly variants

...

...

...

...

...

- initial release

Release Notes and Know Issues

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| anchor | Table_KI |

|---|---|

| title | Known Issues |

...

Requirements

Software

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| anchor | Table_SW |

|---|---|

| title | Software |

...

Hardware

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Basic description of TE Board Part Files is available on TE Board Part Files.

Complete List is available on <design name>/board_files/*_board_files.csv

Design supports following modules:

...

| anchor | Table_HWM |

|---|---|

| title | Hardware Modules |

...

Note: Design contains also Board Part Files for TE0803+TEBF0808 configuration, this boart part files are not used for this reference design.

Design supports following carriers:

...

| anchor | Table_HWC |

|---|---|

| title | Hardware Carrier |

...

Additional HW Requirements:

...

| anchor | Table_AHW |

|---|---|

| title | Additional Hardware |

...

- content of the zip file

For general structure and of the reference design, see Project Delivery - Xilinx devices

Design Sources

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

- Modified Files: xfsbl_main.c, xfsbl_hooks.h/.c, xfsbl_board.h/.c(search for 'TE Mod' on source code)

- Add Files: te_xfsbl_hooks.h/.c (for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device Name

Module Specific:

- Add Files: all TE Files start with te_*

- Si5338 Configuration

- ETH+OTG Reset over MIO

zynqmp_fsbl_flash

TE modified 2018.3 FSBL

General:

- Modified Files: xfsbl_initialisation.c, xfsbl_hw.h, xfsbl_handoff.c, xfsbl_main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

zynqmp_pmufw

Xilinx default PMU firmware.

----------------------------------------------------------

General Example:

hello_te0820

Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output.

u-boot

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin.

Template location: ./sw_lib/sw_apps/

zynqmp_fsbl

TE modified 2018.3 FSBL

General:

- Modified Files: xfsbl_main.c, xfsbl_hooks.h/.c, xfsbl_board.h/.c(search for 'TE Mod' on source code)

- Add Files: te_xfsbl_hooks.h/.c (for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device Name

zynqmp_fsbl_flash

TE modified 2018.3 FSBL

General:

- Modified Files: xfsbl_initialisation.c, xfsbl_hw.h, xfsbl_handoff.c, xfsbl_main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

hello_te0808

Hello TE0808 is a Xilinx Hello World example as endless loop instead of one console output.

Additional Software

| Page properties | ||||

|---|---|---|---|---|

| ||||

| Note: |

No additional software is needed.

Appx. A: Change History and Legal Notices

Document Change History

To get content of older revision got to "Change History" of this page and select older document revision number.

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

...

| anchor | Table_dch |

|---|---|

| title | Document change history. |

...

Authors

...

| Page info | ||||||||

|---|---|---|---|---|---|---|---|---|

|

...

| Page info | ||||

|---|---|---|---|---|

|

...

File

...

File-Extension

...

Description

...

Debian SD-Image

...

*.img

...

Debian Image for SD-Card

...

MCS-File

...

*.mcs

...

Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only)

...

MMI-File

...

*.mmi

...

File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only)

...

SREC-File

...

*.srec

...

Converted Software Application for MicroBlaze Processor Systems

...

| anchor | Table_PF |

|---|---|

| title | Prebuilt files (only on ZIP with prebult content) |

...

File

...

File-Extension

...

Description

...

Download

Reference Design is only usable with the specified Vivado/SDK/PetaLinux/SDx version. Do never use different Versions of Xilinx Software for the same Project.

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

Reference Design is available on:

Design Flow

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Note |

|---|

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first lunch. |

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

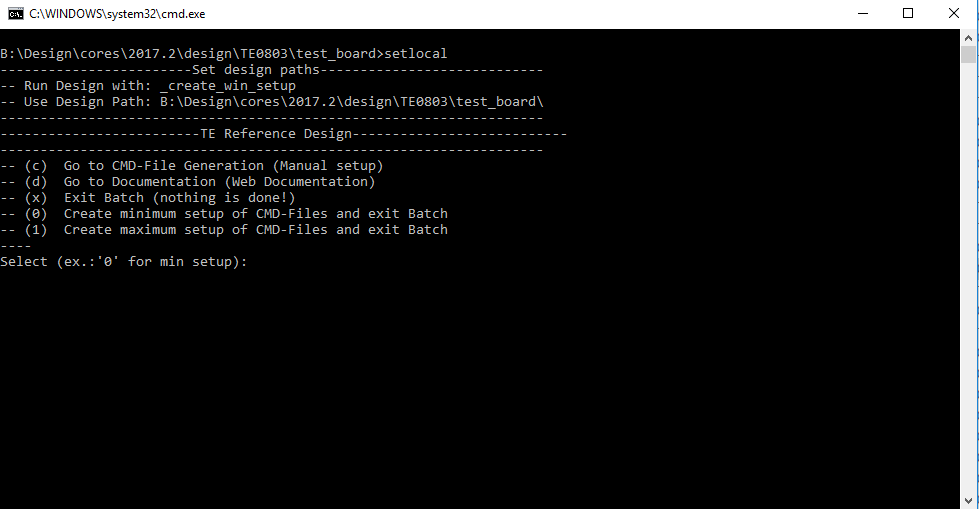

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter to start "Module Selection Guide"

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process

- S(optional for manual changes)elect correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

Important: Use Board Part Files, which did not ends with *_tebf0808

- S(optional for manual changes)elect correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Generate Programming Files with HSI/SDK

- Run on Vivado TCL: TE::sw_run_hsi

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk

Note: See SDK Projects

- Run on Vivado TCL: TE::sw_run_hsi

Launch

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Programming

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

QSPI

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp hello_te0808

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup

Use SDK instead of Vivado is also possible, see: SDK Projects#Xilinx%22HelloWorld%22onZynqMP

SD

This does not work, because SD controller is not selected on PS.

JTAG

Load configuration and Application with SDK Debugger into device, see:

Usage

QSPI Boot:

- Prepare HW like described on section Programming

- Connect UART USB (most cases same as JTAG)

- Select QSPI Card as Boot Mode

Note: See TRM of the Carrier, which is used. - Power On PCB

Note: 1. ZynqMP Boot ROM loads PMU Firmware and FSBL from QSPI into OCM, 2. FSBL loads Application into DDR

Debugging:

System Design - Vivado

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

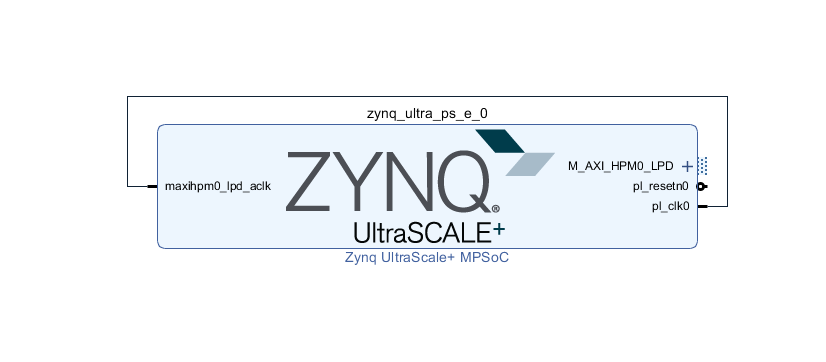

Block Design

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

PS Interfaces

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Activated interfaces:

...

| anchor | Table_PSI |

|---|---|

| title | PS Interfaces |

...

Constrains

Basic module constrains

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLNONE [current_design] |

Design specific constrain

Not needed.

Software Design - SDK/HSI

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

For SDK project creation, follow instructions from:

Application

...

| hidden | true |

|---|---|

| id | Comments |

----------------------------------------------------------

FPGA Example

scu

MCS Firmware to configure SI5338 and Reset System.

srec_spi_bootloader

TE modified 2018.3 SREC

Bootloader to load app or second bootloader from flash into DDR

Descriptions:

- Modified Files: blconfig.h, bootloader.c

- Changes:

- Add some console outputs and changed bootloader read address.

- Add bugfix for 2018.2 qspi flash

xilisf_v5_11

TE modified 2018.3 xilisf_v5_11

- Changed default Flash type to 5.

----------------------------------------------------------

Zynq Example:

zynq_fsbl

TE modified 2018.3 FSBL

General:

- Modified Files:main.c, fsbl_hooks.h/.c (search for 'TE Mod' on source code)

Add Files: te_fsbl_hooks.h/.c(for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device ID

Module Specific:

- Add Files: all TE Files start with te_*

- READ MAC from EEPROM and make Address accessible by UBOOT (need copy defines on uboot platform-top.h)

- CPLD access

- Read CPLD Firmware and SoC Type

- Configure Marvell PHY

zynq_fsbl_flash

TE modified 2018.3 FSBL

General:

- Modified Files: main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

ZynqMP Example:

----------------------------------------------------------

zynqmp_fsbl

TE modified 2018.3 FSBL

General:

...