...

| Scroll Title |

|---|

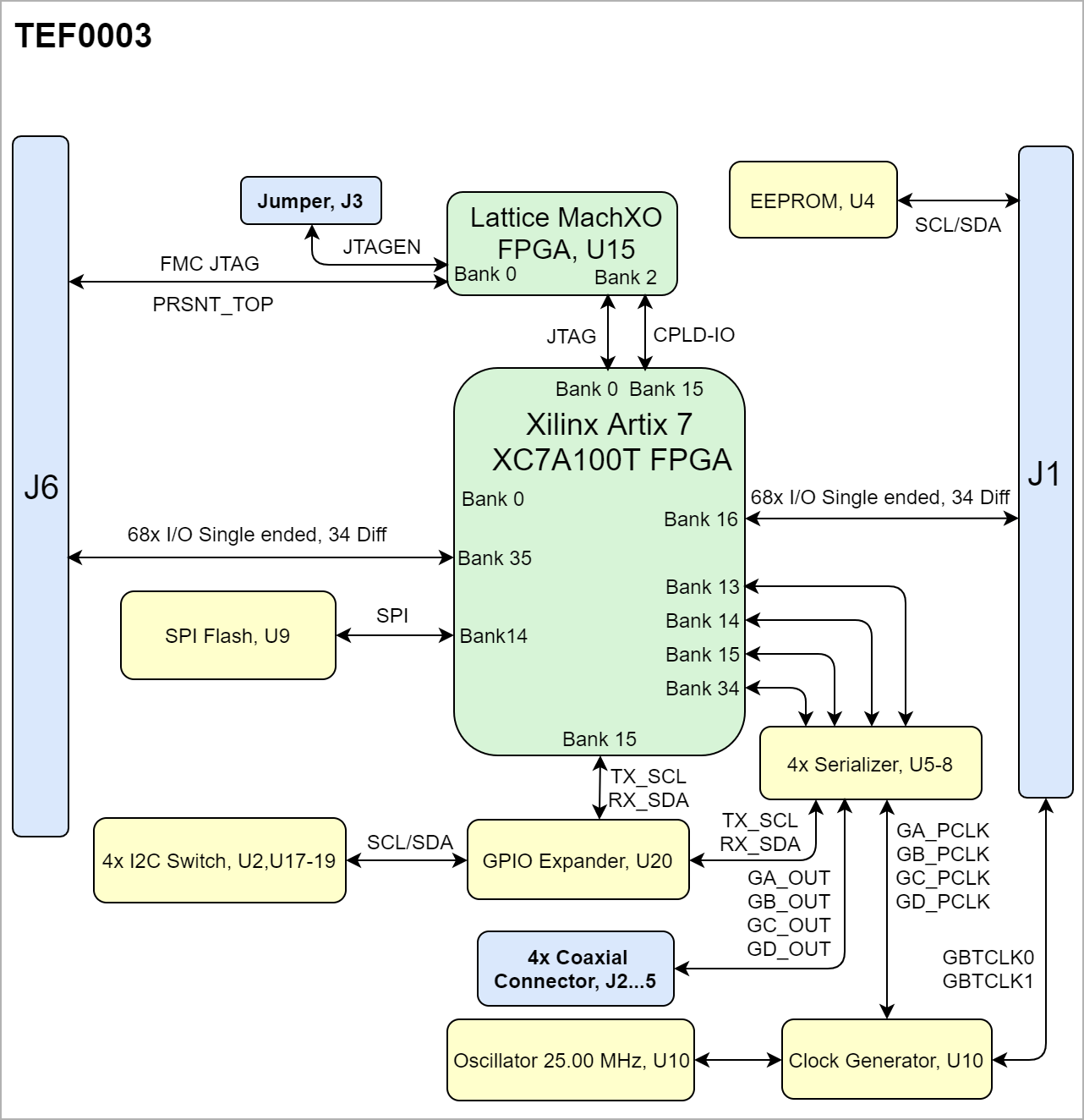

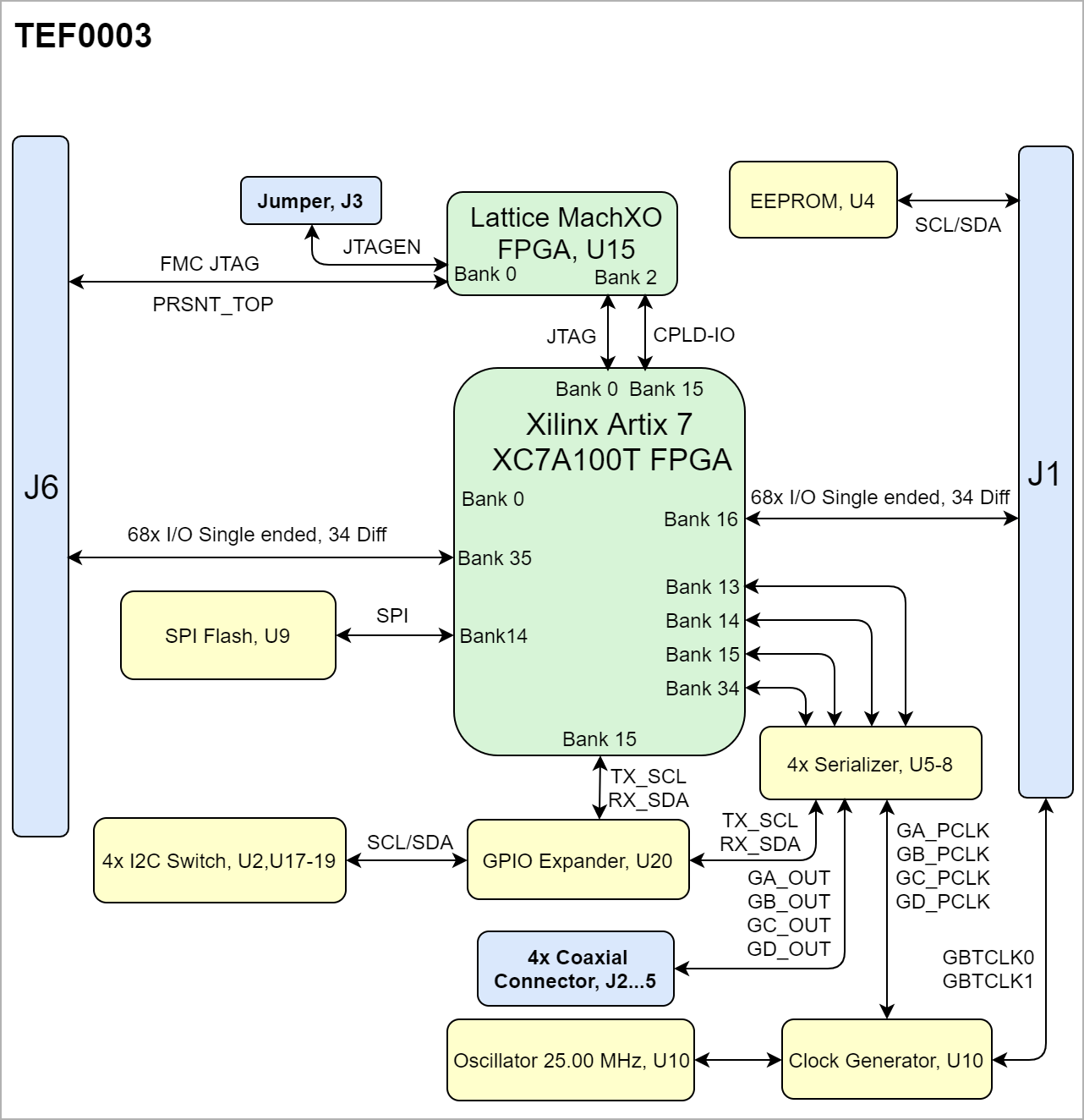

| anchor | Figure_OV_BD |

|---|

| title | TEF0003 block diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 1012 |

|---|

| diagramName | TEF0003_OV_BD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

Image Modified Image Modified

|

|

Main Components

...

| Scroll Title |

|---|

| anchor | Table_OV_RST |

|---|

| title | Reset Process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Signal | Description | Note |

|---|

PRSNT_TOP | Lattice MachXO Configuration Pin |

| | PROG_B | Artix 7 Configuration Pin | Connected Pulled up to 1.8 |

|

Signals, Interfaces and Pins

...

| Scroll Title |

|---|

| anchor | Table_SIP_FMC |

|---|

| title | General PL I/O to FMC Connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| FPGA | FPGA Bank | Connector Designator | I/O Signal Count | Voltage Level | Notes |

|---|

| Artix 7, U1 | 16 | J1B | 68 Single Ended, 34 Differential | 1.8V |

| | 35 | J6B | 68 Single Ended, 34 Differential | 1.8V |

| | Lattice MachXO, U | 0 | J1F | 4 Single Ended | 3.3V | CPLD | | 0 | J6F | 4 Single Ended | 3.3V | CPLD |

|

Coaxial Connectors

| Scroll Title |

|---|

| anchor | Table_SIP_Coaxial |

|---|

| title | Coaxial Connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Schematic | Connected to | Notes |

|---|

| J2 | GA_OUT | Serializer, U5 |

| | J3 | GB_OUT | Serializer, U6 |

| | J4 | GC_OUT | Serializer, U7 |

| | J5 | GD_OUT | Serializer, U8 |

|

|

JTAG Interface

The Lattice MachXO (U15) is available to meet the requirement of a CPLD, JTAG access to the MachXO is available through FMC Adapter J6. JTAG access to the Artix 7(U1) is available via MachXO, Bank 2.

| Scroll Title |

|---|

| anchor | Table_SIP_CPLDJTG |

|---|

| title | CPLD JTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

JTAG Signal | B2B Connector | Notes |

|---|

| FMC_TMS | J6F-TCK |

| | FMC_TDI_TOP | J6F-J1-TDI |

| | FMC_TDO_TOP | J6F-TDO |

| | FMC_TCK | J6F-TCK |

| | JTAGEN | Pulled down |

|

|

| Scroll Title |

|---|

| anchor | Table_SIP_JTG |

|---|

| title | JTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

JTAG Signal | Connected to | Note |

|---|

| TMS | Lattice MachXO, U15 BankArtix 7 FPGA, U1 | Bank 2 Bank 0 | | TDI | Lattice MachXO, U15 Artix 7 FPGA, U1 | Bank 2 Bank 0 | | TDO | Lattice MachXO, U15 Artix 7 FPGA, U1 | Bank 2 Bank 0 | | TCK | Lattice MachXO, U15 Artix 7 FPGA, U1 | Bank 2 Bank 0 | | INIT | Artix 7 FPGA, U1 | Connected Pulled up to 1.8 |

|

On-board Peripherals

...

| Scroll Title |

|---|

| anchor | Table_OBP |

|---|

| title | On board peripherals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

Quad SPI Flash Memory

| Page properties |

|---|

|

Notes : Minimum and Maximum density of quad SPI flash must be mentioned for other assembly options. |

...

| Scroll Title |

|---|

| anchor | Table_OBP_EEP |

|---|

| title | I2C EEPROM interface MIOs and pins |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| U4 Pin | FMC Pcam Adapter | Schematic |

|---|

U4 PinNotesSCLSDAA0A1

| | A2 | - | - | Pulled Low | | WP | - | - | Pulled Low |

|

| Scroll Title |

|---|

| anchor | Table_OBP_I2C_EEPROM |

|---|

| title | I2C address for EEPROM |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| I2C Address | Designator | Notes |

|---|

0x50| 0xA0 | U4 | Write operations are enabled |

|

Clock Sources

| Scroll Title |

|---|

| anchor | Table_OBP_CLK |

|---|

| title | Osillators |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Description | Frequency | Note |

|---|

| U4U11 | Oscillator | 25.00 MHz |

| | U10 | Programmable Clock Generator | Variable |

|

|

...

| Scroll Title |

|---|

| anchor | Table_PWR_PC |

|---|

| title | Power Consumption |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Power Input Pin | Typical Current |

|---|

| VIN3P3V | TBD* |

|

* TBD - To Be Determined

...

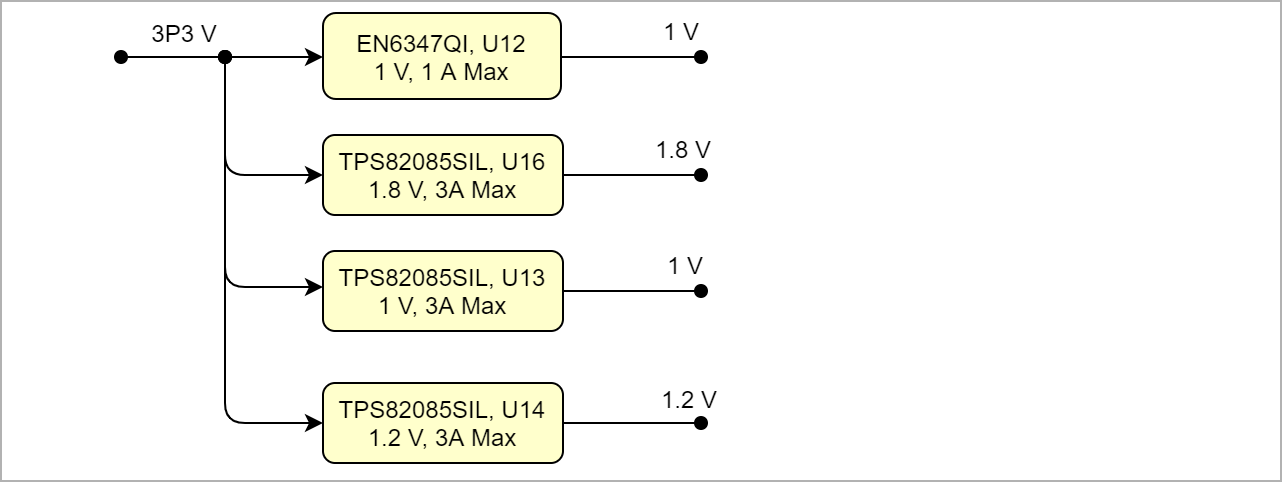

| Scroll Title |

|---|

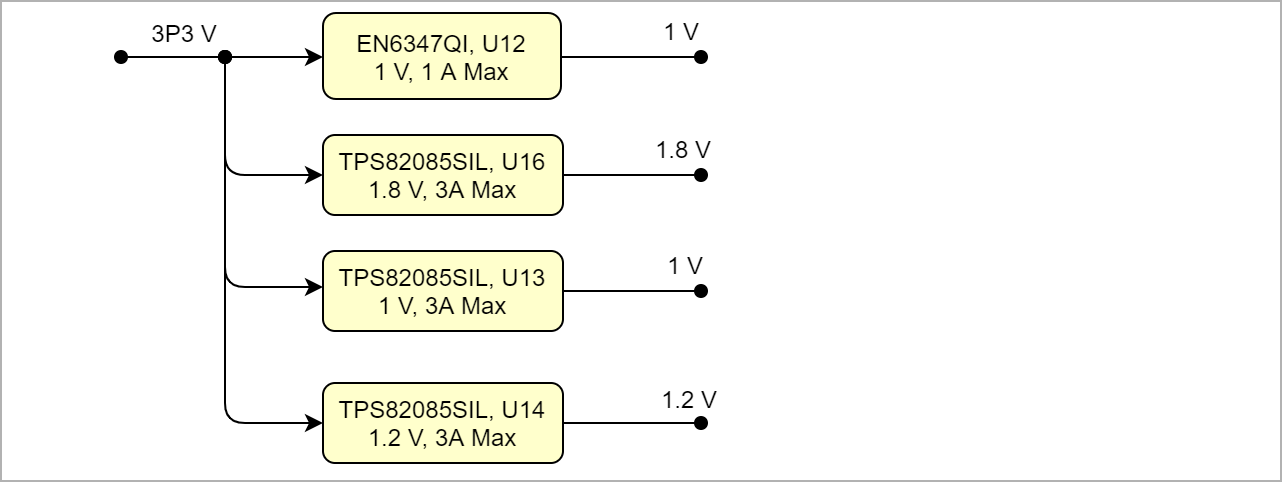

| anchor | Figure_PWR_PD |

|---|

| title | Power Distribution |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 57 |

|---|

| diagramName | TEF0003_PWR_PD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

|

|

...

| Scroll Title |

|---|

| anchor | Table_TS_AMR |

|---|

| title | PS absolute maximum ratings |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Symbols | Description | Min | Max | Unit |

|---|

| 12V3P3V | Input Supply Voltage | -12120.5 | 3.75 | V | | T_STG | Storage Temperature | -40 | 85 | °C |

|

Recommended Operating Conditions

...

| Scroll Title |

|---|

| anchor | Table_TS_ROC |

|---|

| title | Recommended operating conditions. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Parameter | Min | Max | Units | Reference Document |

|---|

12V12 | 12| 2.375 | 3.465 | V |

| | T_OPR | -40 | 85 | °C | See MT25QU512ABB8E12-0SIT (U9) datasheet. |

|

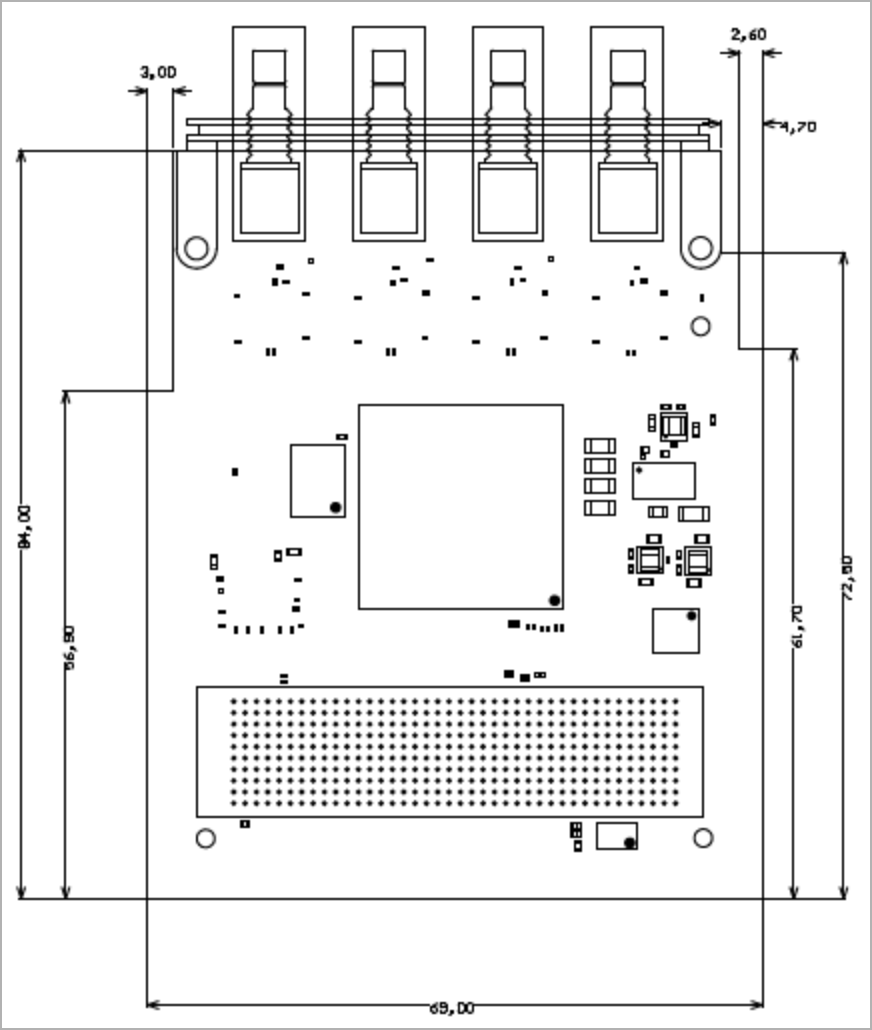

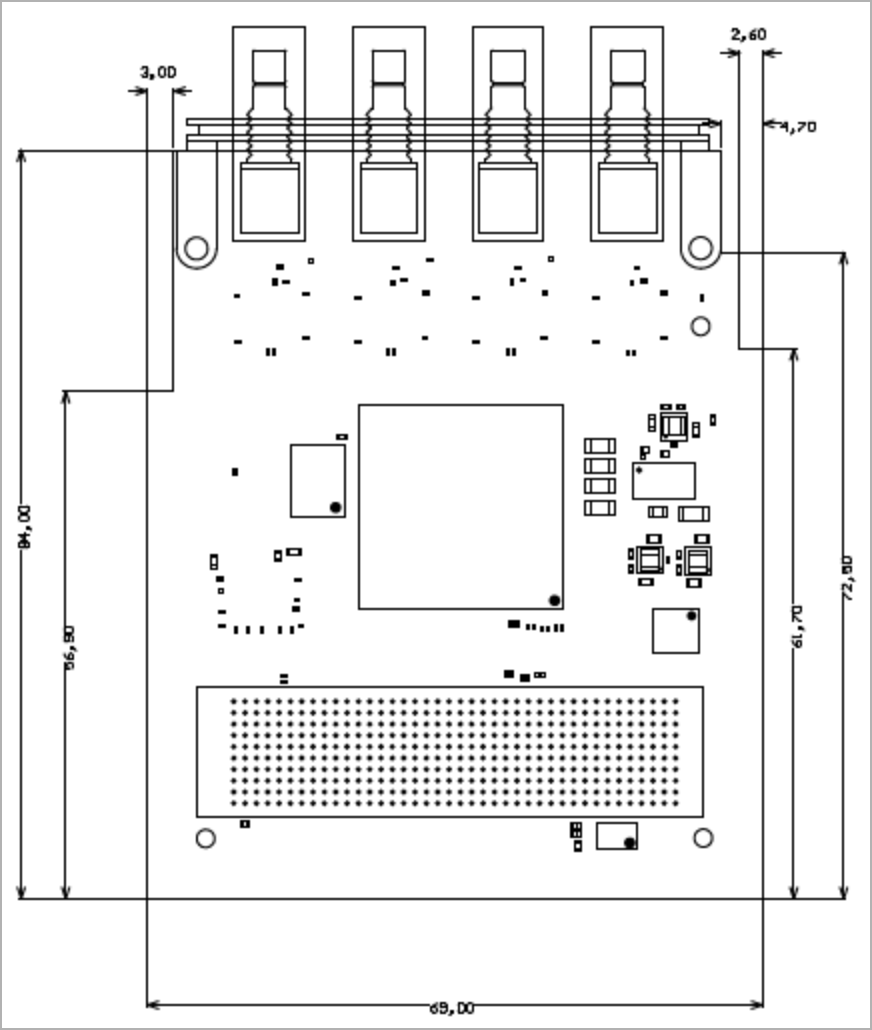

Physical Dimensions

Module size: 84 mm × 65 mm. Please download the assembly diagram for exact numbers.

Mating height with standard connectors: 10 mm.

...

| Scroll Title |

|---|

| anchor | Figure_TS_PD |

|---|

| title | Physical Dimension |

|---|

|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 25 |

|---|

| diagramName | TEF0003_TS_PD |

|---|

| aspect | 5e705185-5827-752c-089d-756568e6698b |

|---|

| simpleViewer | false |

|---|

| width | 639 |

|---|

| aspectHash | 7695f7bc00c98da1082cb1c11a0a6258edf875fc |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 436 |

|---|

|

| Scroll Only |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|

|

|

...

| Scroll Title |

|---|

| anchor | Table_RH_HRH |

|---|

| title | Hardware Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Changes | Documentation Link |

|---|

| 2017-06-27 | REV01 | Initial Release | REV01 |

|

Hardware revision number can be found on the PCB board together with the module model number separated by the dash.

...