...

- SMT pin header, J26

- SMT pin header, J27

- Board to Board (B2B) Connector, JM1

- Board to Board (B2B) Connectorr, JM2

- XMOD header, JX1

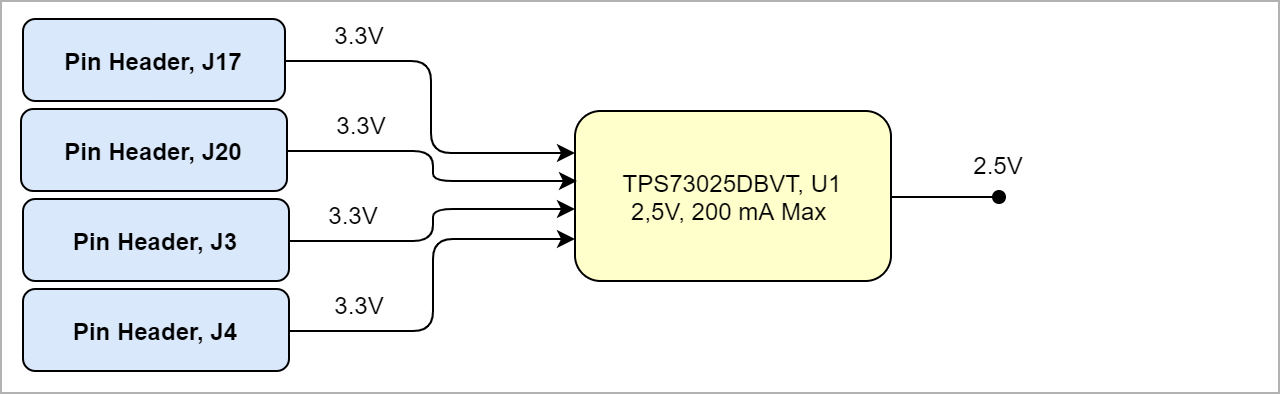

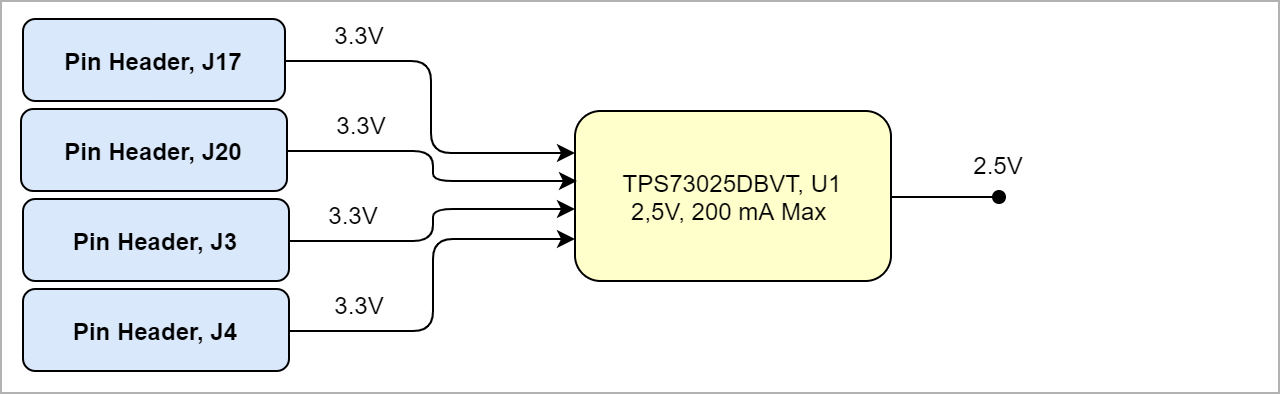

- Voltage Regulator, U1

- User Red LED, D2

- User Green LED, D1 (Red)

- SFP+ Connector, J1

- User Red LED, D3

- 50 - pin header solder pad(Not assembled), J20

- 16 - pin header solder pad(Not assembled), J3,

- 10-pin header solder pad(Not assembled), J4

- 50-pin header solder pad(Not assembled), J17

Initial Delivery State

| Page properties |

|---|

|

| Notes :Only components like EEPROM, QSPI flash and DDR3 can be initialized by default at manufacture.If there is no components which might have initial data ( possible on carrier) you must keep the table empty |

- Pin headers (not soldered to the board, but included in the package as separate component)

| Scroll Title |

|---|

| anchor | Table_OV_IDS |

|---|

| title | Initial delivery state of programmable devices on the module |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Storage device name | Content | Notes |

|---|

| --- | --- | --- |

|

...

| Scroll Title |

|---|

| anchor | Table_OV_RST |

|---|

| title | Reset process. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Signal | B2B | Signal State | Note |

|---|

| PROG_B | JM1-94 | Active Low | Clear FPGA configuration vand and initiate a new configuration |

|

...

Board to Board (B2B) I/Os

FPGA bank number and number Number of I/O signals and Interfaces connected to the B2B connector:

| Scroll Title |

|---|

| anchor | Table_SIP_B2B |

|---|

| title | General PL I/O to B2B connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| B2B Connector | Interface | Number of I/O | Notes |

|---|

JM1

| User I/O | 52 Single ended, 27 Differential | - | | MGT lanes | 4 Differential, 2 lanes |

| | MGT reference clock input | 2 Single ended, 1 Differential |

| | JTAG | 4 Single ended |

| | SoM control signals | 2 Single ended | 'PROG_B', ' DONE' | | JM2 | User I/O | 36 Single ended or 18 differential | - | | SFP+ Interface control signals | 8 Single ended |

| | QSPI interface | 6 Single ended |

| | UART interface | 2 Single ended |

| | User LEDs | 2 Single ended | Red, Green | | SoM control signals | 1 Single ended | 'BOOTMODE' |

|

TEBA0714 is equipped with four pin headers J17, J20, J3 and J4 which are not assembled on the board, in case of need customer can solder the pins and have access to the signals in the following table.

| Scroll Title |

|---|

|

| Scroll Title |

|---|

| anchor | Table_SIP_PinHeader |

|---|

| title | General PL I/O to Pin headers information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pin Header | Interface | Number of I/O | Notes |

|---|

J17

| User I/O | 36 Single ended, 18 Differential | Module FPGA Bank 14 | | SPI interface | 6 Single ended | - | | Power | 4 Single ended | 3.3V, V_CFG | | J20 | User I/O | 42 Single ended or 21 differential | Module FPGA Bank 34 | | Power | 4 Single ended | 3.3V, V_CFG | | User LEDs | 2 Single ended | Red, Green | | SoM control signals | 1 Single ended | 'BOOTMODE' | | J3 | JTAG | 4 Single ended |

| | UART | 2 Single ended | B14_L25, B14_L0 | | ADC | 2 Single ended |

| | Clock | 2 Single ended, 1 Differential |

| | Power | 4 Single ended | 3.3V, V_CFG | | Control Signals | 2 Single ended | BOOTMODE, PROG_B | | J4 | User I/O | 6 Single ended or 3 differential |

| | Power | 2 Single ended | 3.3V, 3.3V_OUT |

|

...

| Scroll Title |

|---|

| anchor | Table_SIP_JTG |

|---|

| title | JTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| XMOD Header Pin | Schematic | B2B Connector |

|---|

Connected to| Pin Header | Note |

|---|

| A | B14_L25 | JM2-97 |

B14_L25| J3-4 | UART Transfer | | B | B14_L0 | JM2-99 |

B14_L0| J3-7 | UART Receive | | E | BOOTMODE | JM2-100 |

BOOTMODEPROG_BTCKTDITDOTMS3.3V | J3,J4,J17,J20 | Nominal Input Voltage | | VIO |

JM2-53 | | V_CFG | - | J17-45 | Configuration Voltage |

|

The DIP-switch S2 on Xmod XMOD Adapter TE0790 must be set as the following table.

| Scroll Title |

|---|

| anchor | Table_SIP_XMODS2 |

|---|

| title | JTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

ON| OFF | Default | 1 | Normal mode | Adapter board CPLD update mode | | Notes |

|---|

| 1 | ON | Update Mode JTAG access to SC CPLD only |

| | 2 |

Do not use (illegal setting)Normal mode | | OFF | Must be in OFF state always |

.| 3 | VIO connected to 3.3V | Power VIO from pin header J2 | OFF | User I/O Voltage | | 4 | Power 3.3V from USB | Power 3.3V from pin header J2 | OFF | Power on-board peripherals (FTDI chip & SC CPLD, ...) | |

The voltages 3.3V (VCC) and VIO (variable SC CPLD I/O-voltage) should be configured by the DIP-switches S2-3 and S2-4 as the following.

|

| | 3 | OFF | 3.3V is input | supplied from pin headers externally | | 4 | OFF | VIO is input | supplied from pin header externally |

|

| Scroll Title |

|---|

| anchor | Table_SIP_XMODS3/4 |

|---|

| title | JTAG pins connection |

|---|

|

| Scroll Table Layout |

|---|

|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

style | widths | | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

| S2-3 | S2-4 | 3.3V (VCC) Pin 5 | VIO Pin 6 | Description |

|---|

| OFF | OFF | 3.3V from base (input**) | VIO from base (input**) | 3.3V (pin 5) and VIO (pin 6) sourced from base |

| OFF | ON | 3.3V from USB* (output**) | VIO from base (input**) | VIO sourced from base by Pin 6 |

| ON | OFF | 3.3V from base (input**) | 3.3V from base (input**) | VIO and 3.3V source by base (Pin 5 and Pin 6 are shorted and both must be sourced by 3.3V) |

ON | ON | 3.3V from USB* (output**) | 3.3V from USB* (output**) | 3.3V (pin 5) and VIO (pin 6) sourced USB (Pin 5 and Pin 6 are shorted and both are 3.3V)

SFP+ Connector

| Scroll Title |

|---|

| anchor | Table_SIP_SFP+ |

|---|

| title | SFP+ Connector Information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Pin | Connected to | Notes |

|---|

| VCCR | 3.3V |

| | VCCT | 3.3V |

| | VREF | GND |

| | TD+/TD- | MGT TX | MGT Lane | | RD+/RD- | MGT RX | MGT Lane | | TX/FAULT | SFP0_TX_FAUL | SFP_CTRL | | TX/DISABLE | SFP0_TX_DIS | SFP_CTRL | | MOD-DEF2 | SFP0_SDA | SFP_CTRL | | MOD-DEF1 | SFP0_SCL | SFP_CTRL | | MOD-DEF0 | SFP0_MT_DEF0 | SFP_CTRL | | RS0/RS1 | SFP0_RS0_1 | SFP_CTRL | | LOS | SFP0_LOS | SFP_CTRL |

|

...

| Scroll Title |

|---|

| anchor | Table_SIP_SMD |

|---|

| title | SMD Connector Information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| SMT Pin Header | VCCIO/VCC | Voltage Level | Notes |

|---|

| J26 | VCCIO34

| 1.8V |

| | 2. |

5V| 5V |

| | 3.3V | 3.3V_OUT | | J27 | V_CFG

| 1.8V |

| | 2.5V | V_CFG0 | | 3.3V | 3.3V_OUT |

|

On-board Peripherals

| Page properties |

|---|

|

Notes :- add subsection for every component which is important for design, for example:

- Two 100 Mbit Ethernet Transciever PHY

- USB PHY

- Programmable Clock Generator

- Oscillators

- eMMCs

- RTC

- FTDI

- ...

- DIP-Switches

- Buttons

- LEDs

|

...

| Scroll Title |

|---|

| anchor | Table_OBP_LED |

|---|

| title | On-board LEDs |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Designator | Color | Connected to | Active Level | Note |

|---|

| D1 | Green | GLED | Active High |

| | D2 | Red | RLED | Active High |

| | D3 | Red | DONE | Active Low | DONE pin |

|

Power and Power-On Sequence

...

| Scroll Title |

|---|

| anchor | Table_PWR_PC |

|---|

| title | Power Consumption |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Power Input Pin | Typical Current |

|---|

| VIN3.3V | * TBD |

|

* TBD - To Be Determined

Power Distribution Dependencies

3.3V can be supplied through Pin Headers on specific pins.

| Scroll Title |

|---|

| anchor | Figure_PWR_PD |

|---|

| title | Power Distribution |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 79 |

|---|

| diagramName | TEBA0714_PWR_PD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 640 |

|---|

|

|

| Scroll Only |

|---|

|

|

...

There is no specific power-on sequence, after power up . After power on, the module and carrier will be powered on.

...

| Scroll Title |

|---|

| anchor | Table_PWR_PR |

|---|

| title | Module power rails. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

ConnectorJM1 Pin , JM1 Pin | B2B JM2 Pin | Pin Header J17 | Pin Header J20 | Pin Header J3 | Pin Header J4 |

|---|

B2B Connector JM2 Pin,97-| ,97 | - | 5, 46 | 5, 46 | 5 | 5 | Input |

| | 1.8V | - | 18 | - | - | - | - | Input | Comes from Module | | 3.3V_OUT | 83 | 54 | - | - | - | 6 | Output |

| | VCCIO34 | 61 | - | - | 45 | - | - | Output | Variable voltage level | | V_ |

CFG0| CFG | 53 | - | - | - | - | - | Input | Variable voltage level |

|

Board to Board Connectors

| Page properties |

|---|

|

- This section is optional and only for modules.

- use "include page" macro and link to the general B2B connector page of the module series,For example: 6 x 6 SoM LSHM B2B Connectors

| Include Page |

|---|

| PD:6 x 6 SoM LSHM B2B ConnectorsPD: |

|---|

| 6 x 6 SoM LSHM B2B Connectors |

|---|

|

|

TEBA0714 carrier use two Samtec Razor Beam LSHM Connectors on the bottom side.

| Include Page |

|---|

| PD:4 x 5 SoM LSHM B2B ConnectorsPD: |

|---|

| 4 x 5 SoM LSHM B2B Connectors |

|---|

|

...

| Scroll Title |

|---|

| anchor | Table_TS_AMR |

|---|

| title | PS absolute maximum ratings |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Symbols | Description | Min | Max | Unit |

|---|

| VIN | Input Supply Voltage | -0.3 | 6 | V | | T_STR | Storage Temperature | -40 | 85125 | °C |

|

Recommended Operating Conditions

...

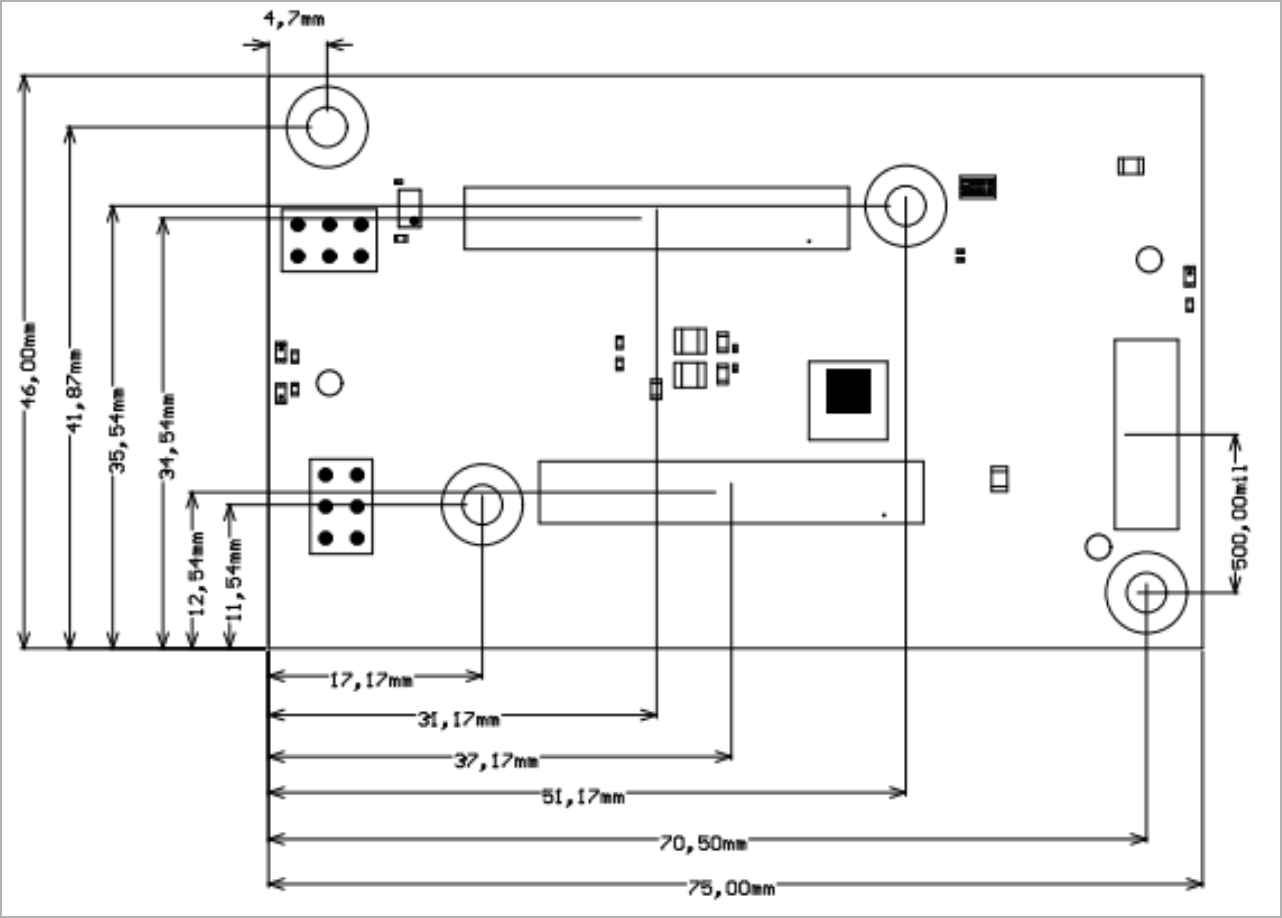

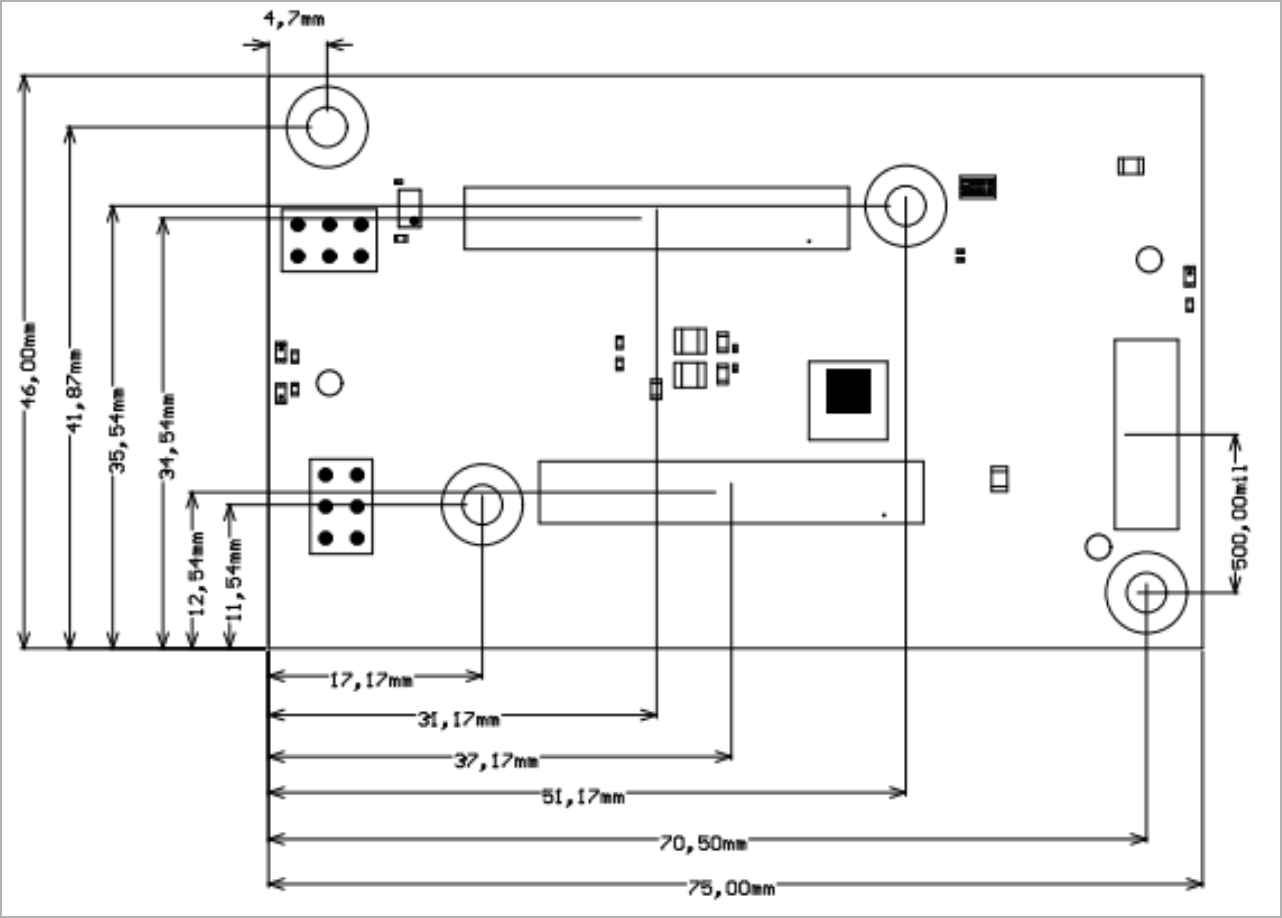

| Scroll Title |

|---|

| anchor | Figure_TS_PD |

|---|

| title | Physical Dimension |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | truefalse |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 1 |

|---|

| diagramName | TEBA0714_TS_PD |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 | revision | 1 |

|---|

|

|

| Scroll Only |

|---|

| scroll-pdf | true |

|---|

| scroll-office | true |

|---|

| scroll-chm | true |

|---|

| scroll-docbook | true |

|---|

| scroll-eclipsehelp | true |

|---|

| scroll-epub | true |

|---|

| scroll-html | true |

|---|

|  |

|

...

| Scroll Title |

|---|

| anchor | Table_RH_HRH |

|---|

| title | Hardware Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Changes | Documentation Link |

|---|

| 2016-06-15 | 01 | | REV01 |

|

Hardware revision number can be found on the PCB board together with the module model number separated by the dash.

...