Page History

...

| Scroll pdf ignore | |

|---|---|

|

Introduction

This User Manual describes the The Electronic Drive Development Platform (EDDP) provides all necessary software and hardware components for development and evaluation of motor control applications. While these components (both software and hardware) can also be used separately, this manual describes EDDP usage with default reference hardware platform (EDDP Kit) only.

| Note |

|---|

None of the EDDP components are Hardware components/boards delivered in EDDP Kit are not intended to be used in finished final products. All the software and hardware parts of the Platform EDDP are intended for Developers developers evaluating Motor Control Applications with Xilinx FPGA and/or SoC Devices. |

Requirements

The following is required in addition to what is supplied in the EDDP Kit:

devices. |

Use of Terms

The terms and acronyms used in the EDDP User Manual and EDPS User Manual are listed in the Table 1.

| Term | Description |

|---|---|

| Adapter Board | Adapts the Reference Motor to the EDPS Board. |

| Control Board | An electronic board for controlling the EDPS Board, a Digilent board Arty Z7. |

| EDDP | Electronic Drive Development Platform. |

| EDDP Kit | A kit consisting of the EDPS Board, the Reference Motor, the Adapter board and. |

| EDPS Board | An Electric Drive Power Stage Board, a Trenz Electronic GmbH board TEC0053. |

| Host PC | A computer capable of running a web browser in order to run the Web UI. |

| Reference Motor | The motor included in the EDDP Kit. This motor is of brushless type and is already mated with an encoder. |

| Web UI | A user interface in the form of a web page permitting operating the EDDP. |

Table 1: Terms and acronyms used.

Requirements for the Functional Test

The purpose of the Functional Test is to verify the functionality of the hardware by using the default firmware supplied.

Following items are required in addition to the EDDP Kit:

- Micro-USB Cable for the USB console of the Controller Board.

- Ethernet-based LAN with a DHCP server.

- RJ45 ethernet Cable.

- Computer with web browser to access the Web UI.

- Card reader supporting micro-SD Cards.

- Access to internet (to download SD Card images).

| Note |

|---|

In order to pass EMC radiated emission (EN 55011) class B requirements option "Spread Spectrum" must be activated (standard setting). |

| Note |

|---|

Software version that was used in EMC test: (Visible in the GUI main screen) 2017-7-31 (SVN Tag 5745). |

| Scroll Pagebreak |

|---|

Requirements for the Development

Requirements for the development with SDSoC:

- All items listed under the Requirements for Functional Test.

- Basic knowledge of Xilinx All Programmable FPGA and/or SoC devices, basic knowledge of Xilinx SDK and C/C++ programming in order to be able to adapt the firmware to your requirements.

- A PC capable of running Xilinx SDSoC 2017.1 development environment.

- A valid Xilinx SDSoC license or voucher.

Requirements for the development with HLS:

- All items listed under Requirements for Functional Test.

- A PC capable of running the Xilinx SDSoC 2017.1.

- Basic knowledge of Xilinx All Programmable FPGA and/or SoC devices, basic knowledge of Xilinx SDK and C/C++ programming in order to be able to adapt the firmware to your requirements.

- A PC capable of running Xilinx Vivado 2017.1

Installation

| Note |

|---|

Micro |

...

-SD is delivered without Linux images to avoid any issues related to US export control regulations. |

Hardware Assembly

When delivered as full EDDP Kit several components are pre-assembled.

Motor Adapter Board

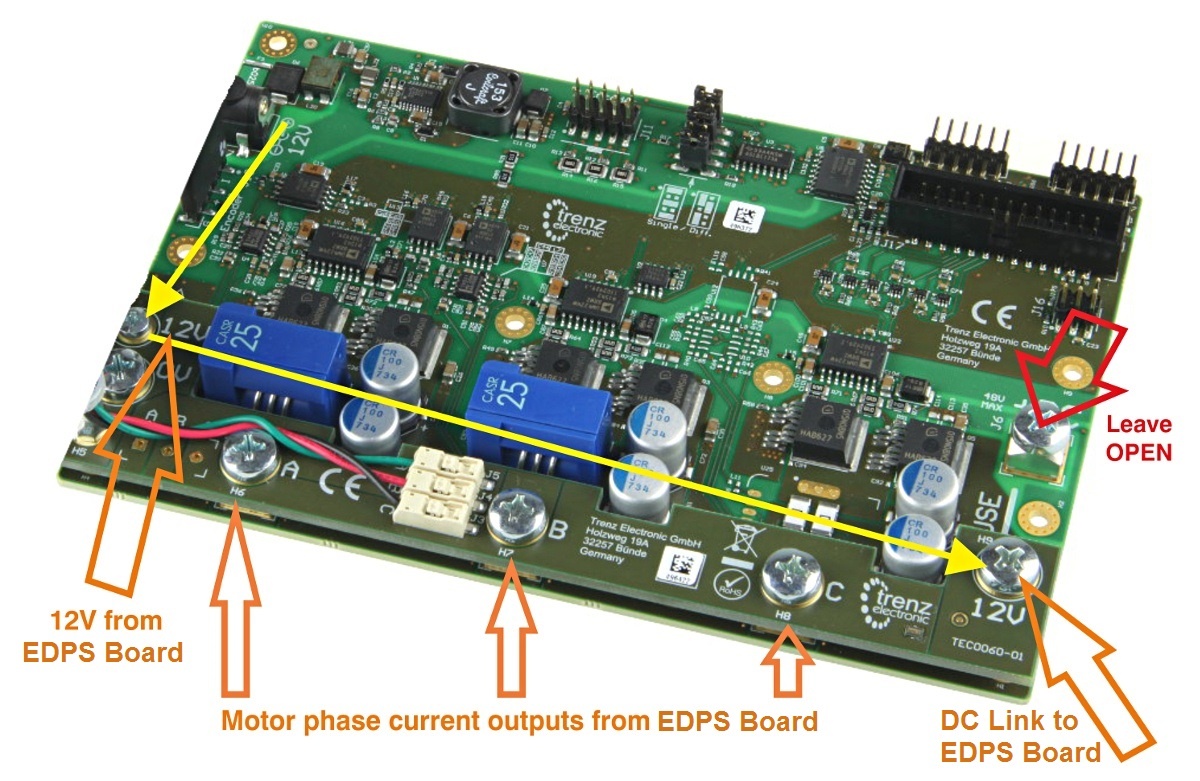

The Reference Motor with Encoder is connected to the EDPS Board using the Adapter Board (see Figure 1). In the EDDP Kit the Reference Motor is pre-assembled.

Figure 1: Top view of the EDPS Board with the Adapter Board mounted.

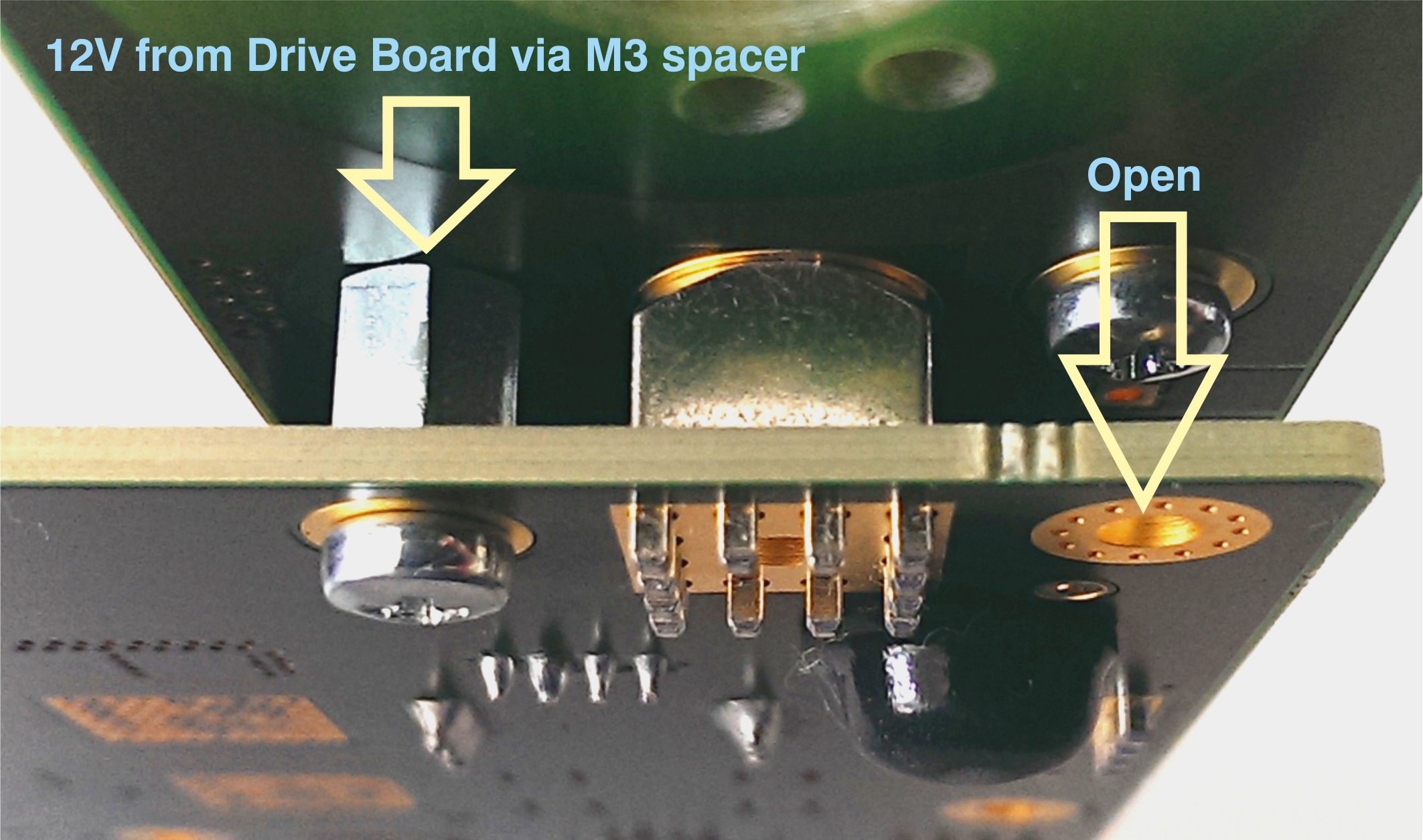

The Adapter Board is mounted to the EDPS Board using 5 x M6 screws (Labels 0V, A, B, C, 12V on Adapter Board) and with M3 screws and spacer - marked 12V at the left. This Adapter Board "forwards" (the yellow arrow) the EDPS Board pre-driver supply (12V) to the DC Link main terminal on the EDPS board, so that separate DC Link power supply is not needed allowing easy evaluation of the complete system.

| Scroll Pagebreak |

|---|

Note terminal marked+DC must be left open when using the Adapter Board!

Figure 2: M3 spacer and two M3 screws connect 12V from the EDPS board to the Adapter Board.

Motor Connection

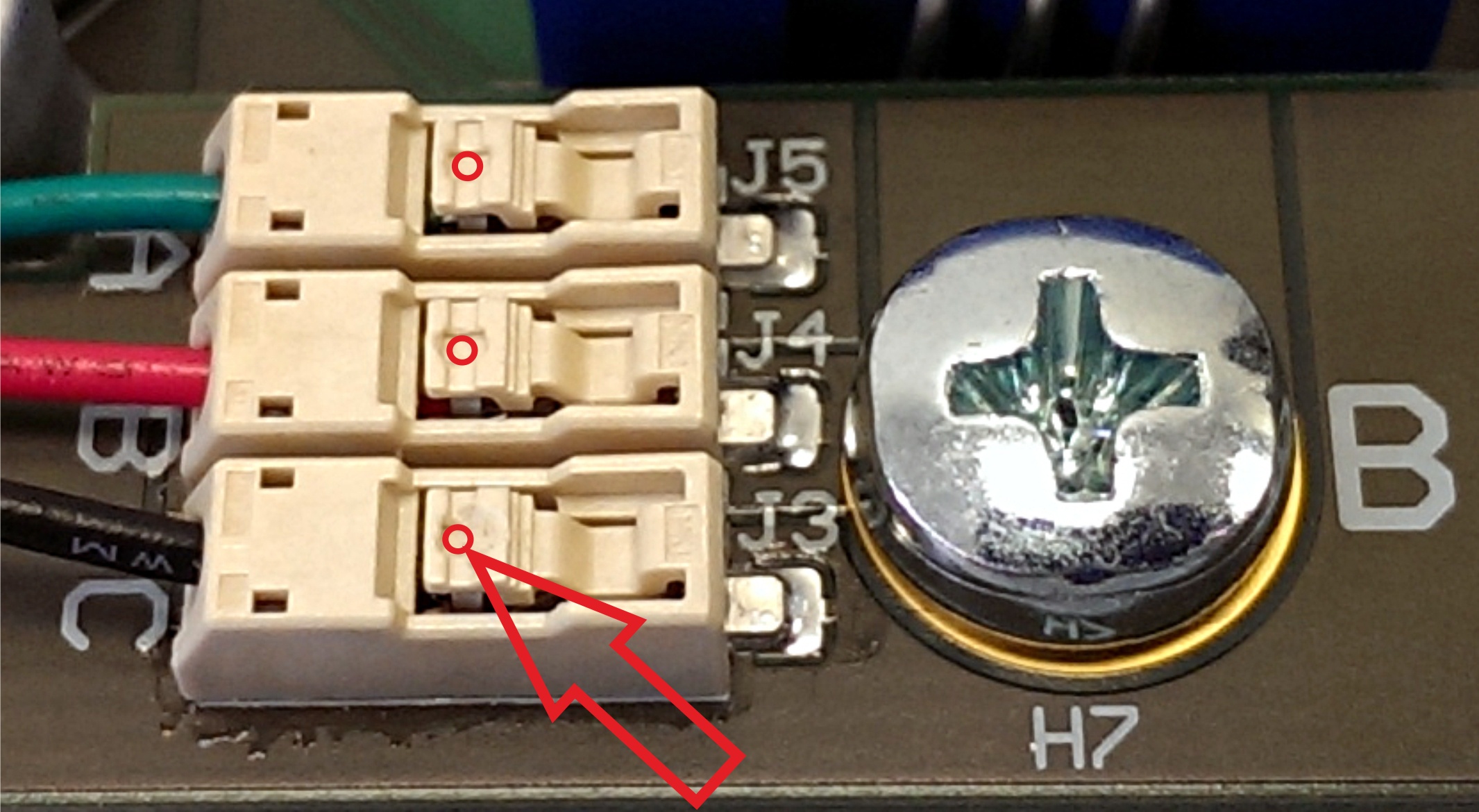

In the EDDP Kit the Reference Motor stator wires for all three phases are already connected to the Adapter Board. Instructions for manual assembly below:

Figure 3: Red dots and arrow mark the place where wire terminal can be released for insertion or removal.

Use a ball-point pen or similar tool to apply gentle force at the dot to release the wires. Do not try to remove the wires by simply pulling them out without releasing them first! Do not apply force in any other region of the white plastic except as marked, because it is easy to damage the plastic.

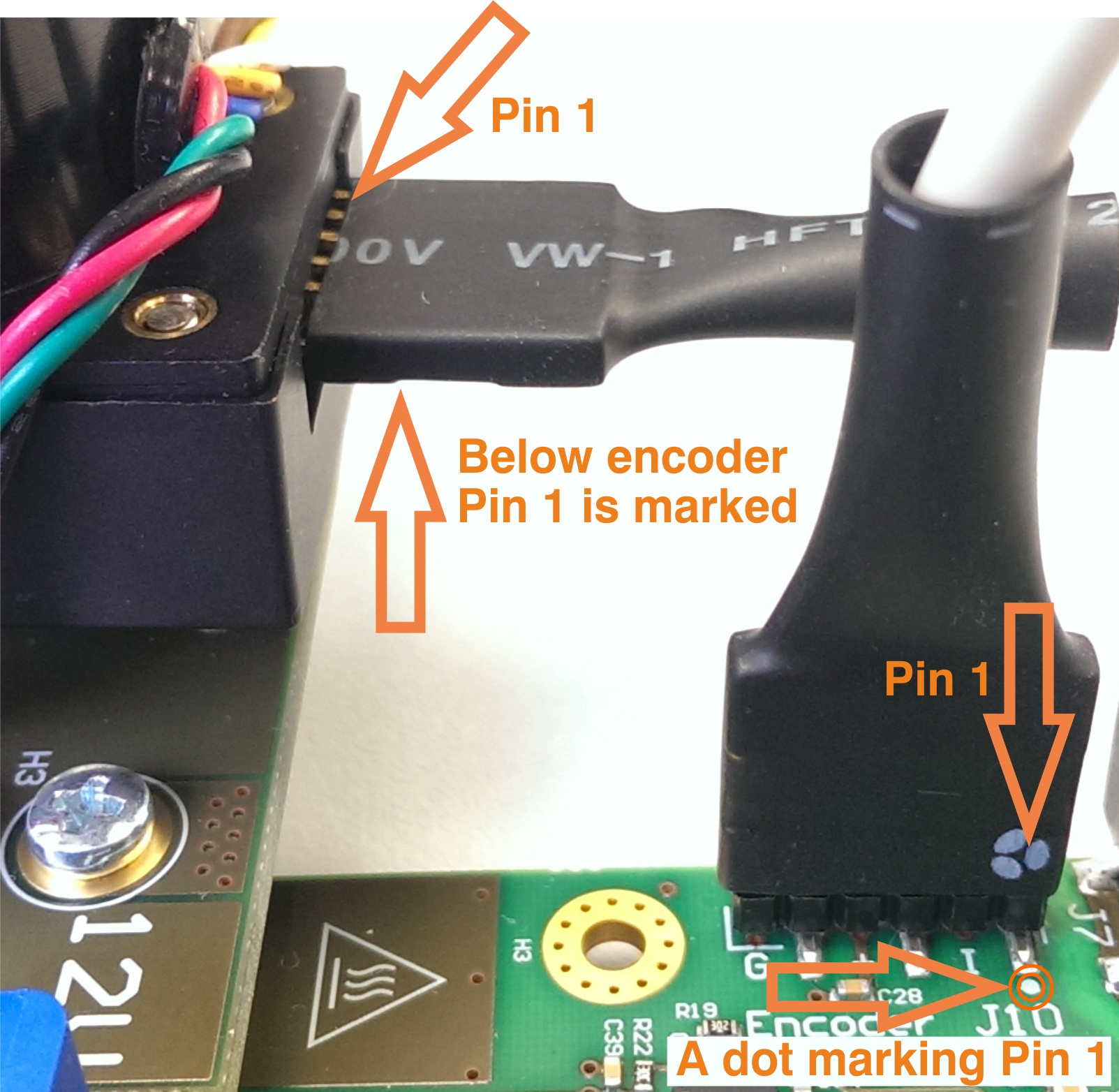

Encoder Connection

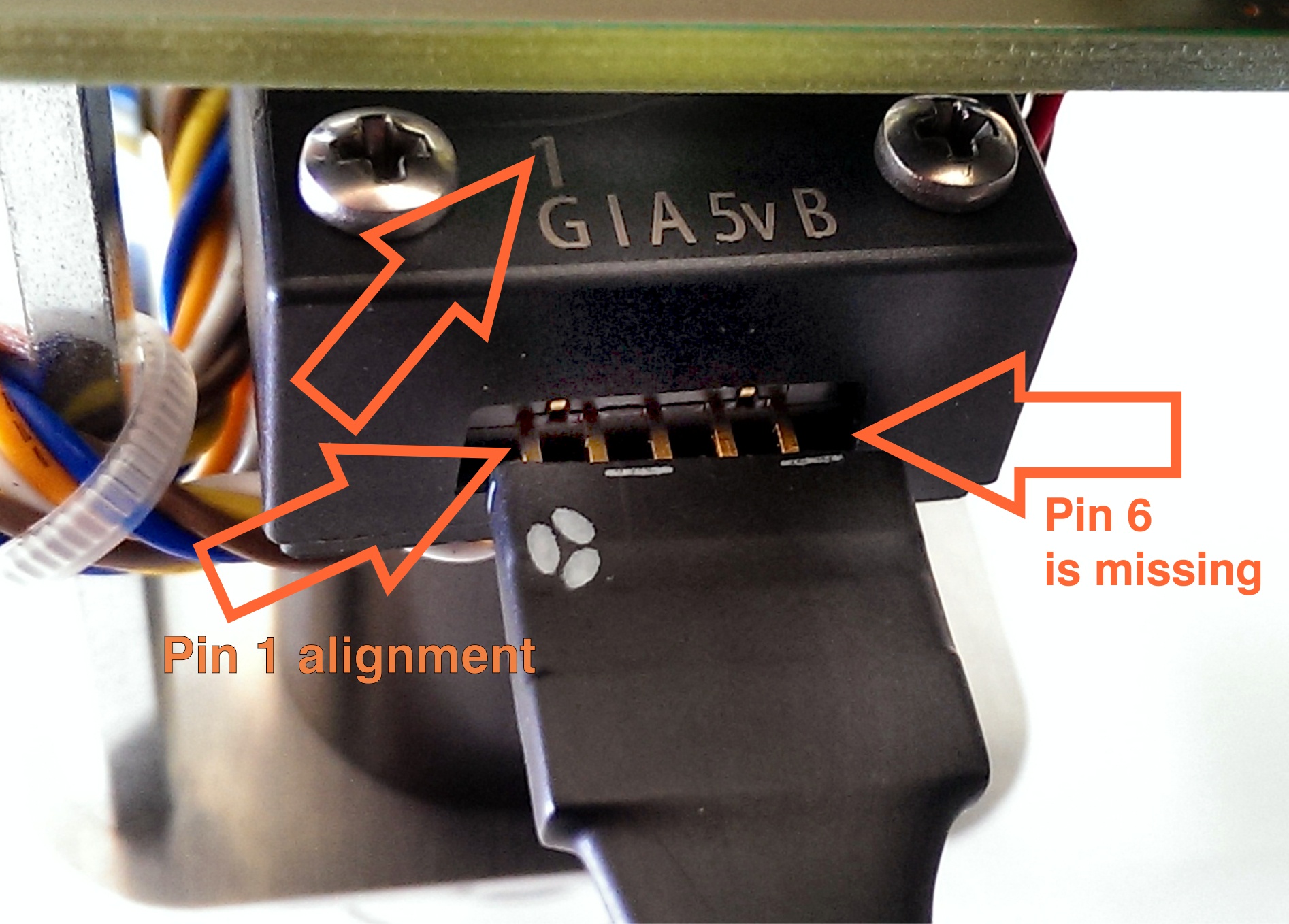

One 6-pin Pmod cable is included with the EDDP Kit. It is already assembled between the encoder and the EDPS Board. Instructions for manual assembly are below:

Figure 4: Pmod cable alignment to the Encoder connector.

Notice that there are 5 pins in the Encoder header while the PMoD female connector has 6 terminals. Red Arrow marks the "empty" terminal at the PMoD Cable.

Figure 5: Pmod cable installation.

Pin 1 markings are indicated with the arrows, on the EDPS Board a white dot marks 6-pin Pmod header pin 1. This pin should be aligned to the Encoder Pin marked "G" and "1" visible when looking from the bottom up. Please note that Encoder header has 5 terminals while the driver board and Pmod cable have 6 terminals.

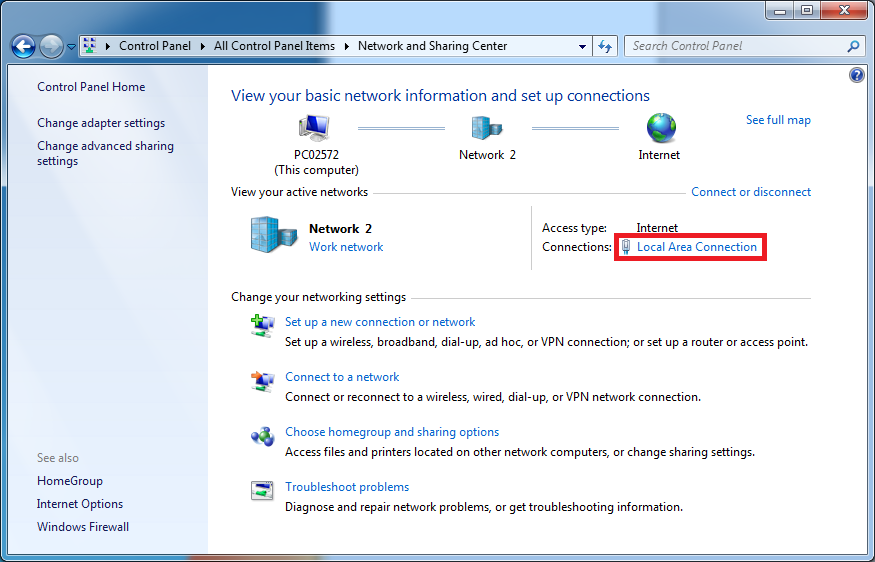

Network configuration on the Host PC (Optional)

An overview of network configuration and some methods for network troubleshooting are given.

It is assumed that the operating system on the Host PC is Microsoft Windows 7 or newer. For other operating systems, the basic network principles are the same, but the means of configuration are different; consult the corresponding user guides.

Open the Control Panel and click on the Network and Sharing Center. The following window appears:

Figure 6: The Network and Sharing Centre, with the network connection used for communication with the Control Board highlighted.

Viewing network connection status

Locate the network connection that is to be used for communication with the Control Board and click on it. The network connection status dialog appears (Figure 7).

Figure 7: A network connection status dialog, with the media status and number of bytes sent and received highlighted.

For normal operation, the media state should read "Enabled".

During normal operation, the number of bytes sent and received should increase when there is network traffic, for example, when pinging the Control Board, when operating the Web UI, when pinging, etc.

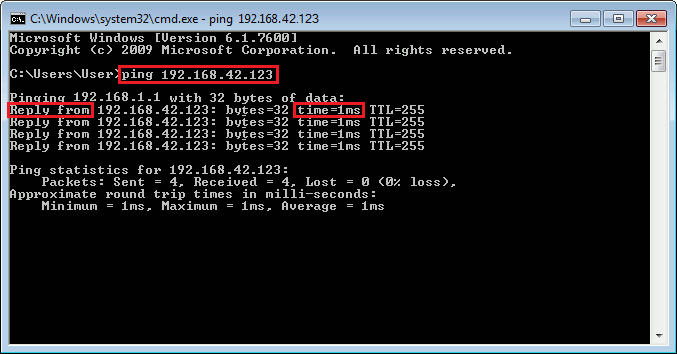

Checking network connectivity to the Control Board

On the Start Menu, select "All Programs" → "Accessories" → "Command Prompt. A command prompt window appears. Enter the command

ping IPwhere IP is the IP address of the Control Board. The result should be similar to the one on the following figure (Figure 8):

Figure 8: Successful check of network connectivity to the Control Board. The command entered by the user is highlighted, as are the important keywords that should be present in the output of the command "ping".

Note: After a recent change of network settings, it can happen that the ping is not successful because the changes haven't propagated to the other participiants on the network yet. It can be sometimes remedied by running the command "ping" on the other computer, in this case, on the Control Board, pinging the IP address of the Host PC.

Verifying network adapter settings

In the network connection status dialog (Figure 7), click "Details". A Network Connection Details dialog appears:

Figure 8: A Network Connection Details dialog, with the important IP settings highlighted.

The network settings should be such that the Control Board is reachable from the Host PC. In the case when they are in the same network segment (gateway is not involved), the following conditions should hold:

- The subnet mask should be the same for the Control Board and the Host PC.

- The IP addresses for the Control Board and Host PC must be different.

- The subnet mask divides the IP address into two parts according to the the bits set in the binary notation (255 in decimal = 11111111 in binary):

- The network address, which corresponds to the the bits set in the subnet mask. This should be the same for the Control Board and the Host PC.

- The host address, which corresponds to the bits not set in the subnet mask. This should be different for the Control Board and the Host PC. Additional constraint: it cannot be neither null nor the maximum value.

On the example of settings shown on Figure 8 and the default configuration in the default firmware, the conditions are fulfilled as follows:

- The subnet mask, 255.255.255.0, is the same for both.

- The IP addresses, 192.168.42.100 for the Host PC and 192.168.42.123 for the Control Board, differ.

- The subnet mask checks out as follows:

- The network address, 192.168.42.0, is the same for the Host PC and the Control Board.

- The host addresses, 0.0.0.100 for the Host PC and 0.0.0.123 for the Control Board, are different. In addition, neither is 0 nor the maximum value, 255 in this case.

Alternative method of viewing network settings: Open command prompt (see Figure 8) and execute the following command:

ipconfigIt will list all network connections and their associated IP addresses.

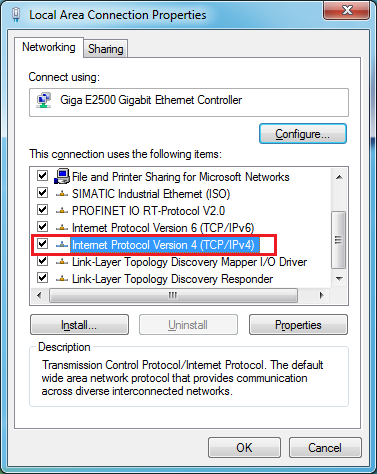

Changing the IP settings of a network connection

On the network connection status dialog (Figure 7), click "Properties". The following dialog (Figure 9) appears:

Figure 9: A network connection properties dialog. The item "Internet Protocol Version 4 (TCP/IPv4)" is selected and highlighted.

In the list of items used, select "Internet Protocol Version 4 (TCP/IPv4)" and click "Properties". The following dialog appears:

Figure 10: A TCP/IPv4 Properties dialog.

The settings on this dialog have to match the actual network settings.

In most network setups, settings are as follows:

- Checked: Obtain an IP address automatically.

- Checked: Obtain DNS server address automatically.

In the case when using an network adapter dedicated solely for nothing else but communication with the Control Board, a static IP configuration (as shown on Figure 10) is to be used as follows:

- Checked: Use the following IP address:

- IP address: 192.168.42.100

- Subnet mask: 255.255.255.0

- Default gateway: not configured.

Other cases are not considered here; consultation with network administration and/or appropriate handbooks is recommended.

| Page break |

|---|

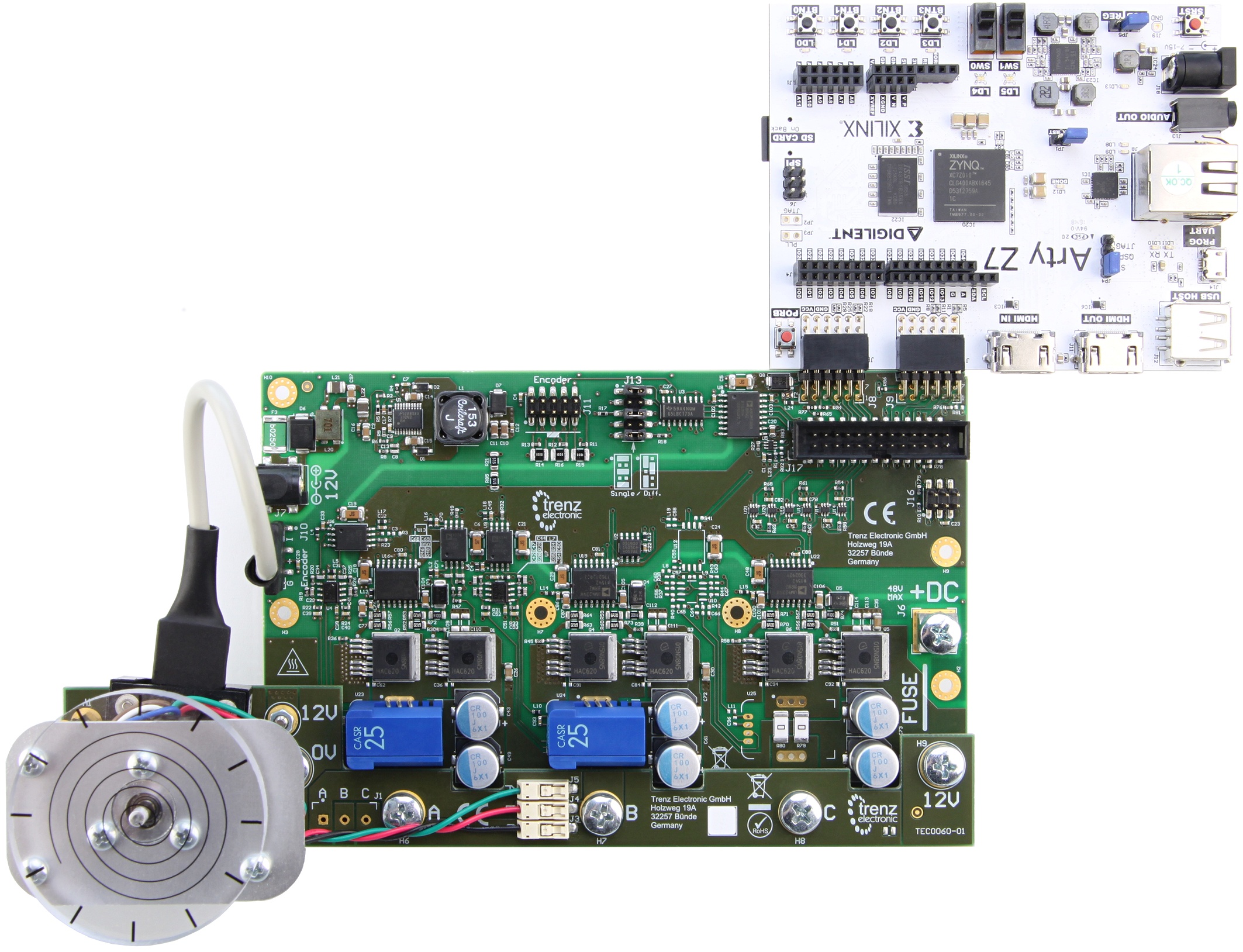

EDDP System Components

Figure 11: EDDP Kit assembly.

EDDP Kit Content

- Control Board: ARTY-Z-7010

- EDPS Board: TEC0053

- Adapter Board: TEC0060

- Reference Motor with Encoder: BLRW-111D-24V-10000-1000-SI

- Plastic DEMO load for Motor

- One 6 Pin PMoD cable

- Two 12V Power Supplies

- Screws and other accessories used to mount the motor

- One spare M6 Screw

- Plastic cover for Driver Board use without TEC0060

- 30A Fuse for Driver Board use without TEC0060

- Micro SD Card

- Quickstart Guide

| Note |

|---|

The Motor is pre-mounted to the EDPS Board using the Adapter Board and accessories. |

The following is optional:

- Custom Controller Board.

- Custom motor and encoder.

- Power supply DC 5..48V to suit the custom motor power requirements.

Installation

todo

EDDP System - TODO

Hardware - TODO

Software

The software consists of the following parts:

- A Linux operating system.

- Kernel driver for providing access to the IP cores and buffer memory for the data capture

- A user-space program that provides access to the motor control IP cores through the Network API and simultaneously serves as a Web server.

- A user interface in the form of a Web UI to the Network API.

The Web UI lets one to operate the motor in one of the following modes:

- Speed control.

- Stator current Iq control.

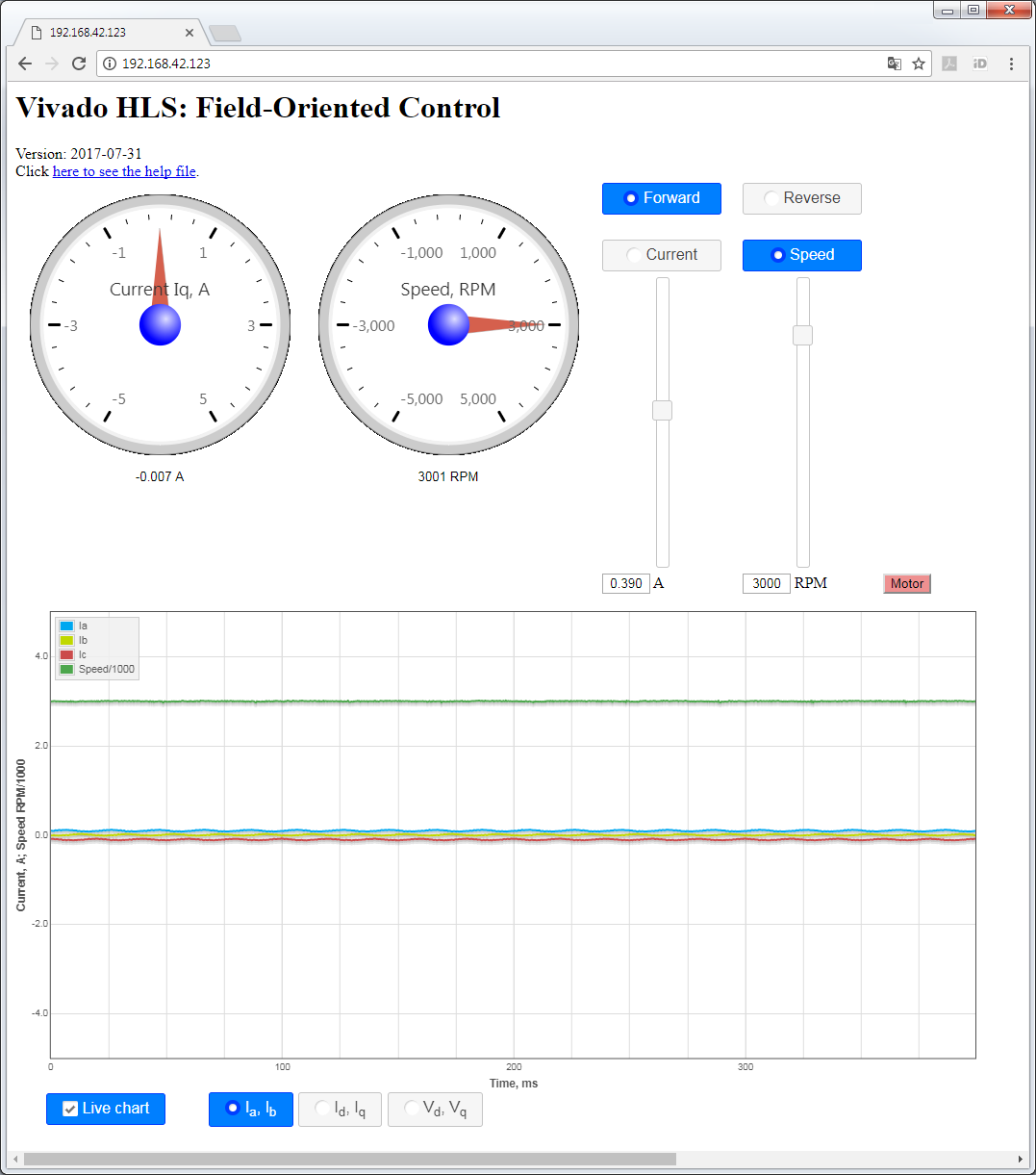

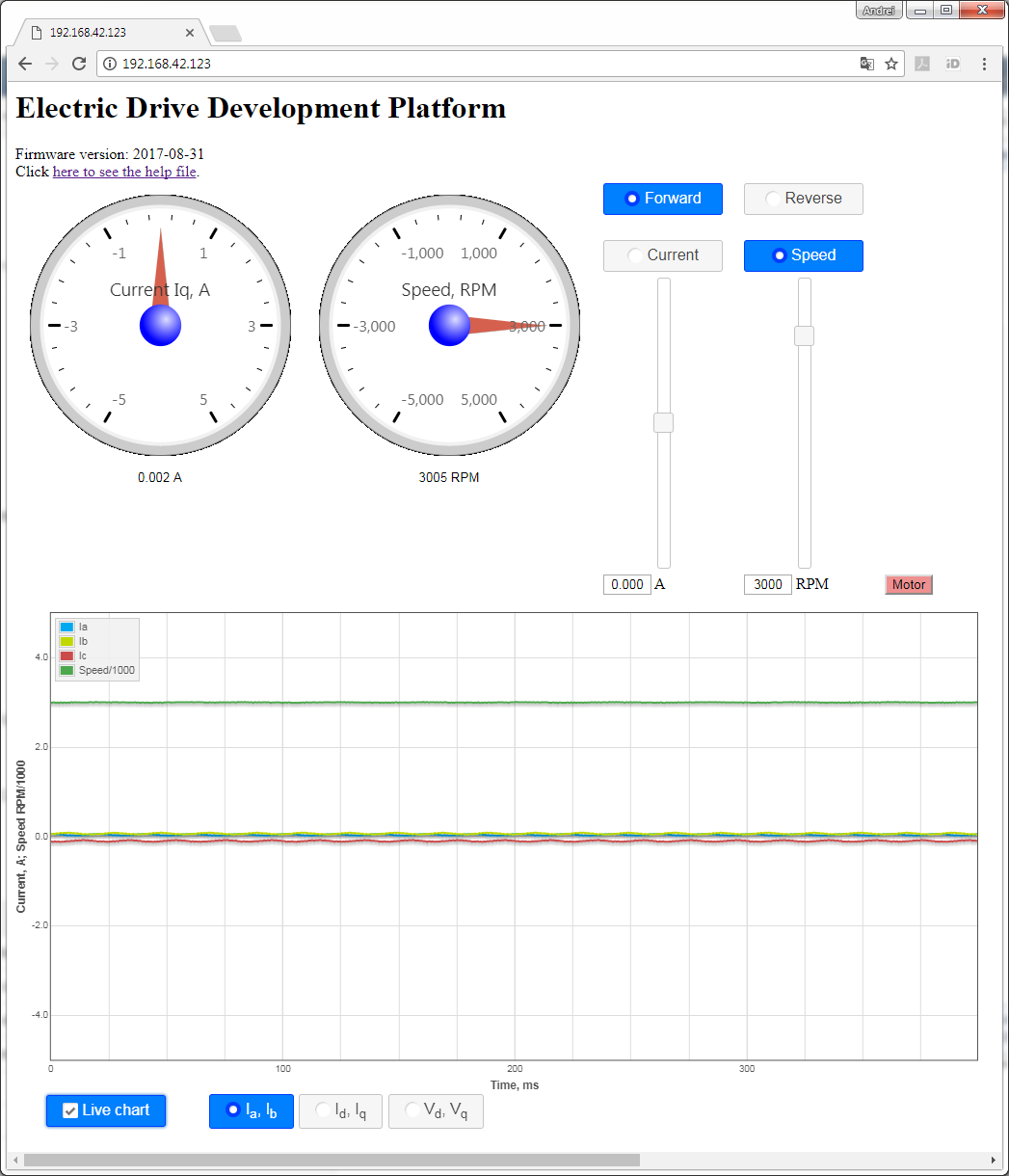

To access the Web UI, point a web browser to the IP of the Controller Board. The following web site appears:

Motor

The default motor is supplied in the EDDP Kit; see the chapter Reference Motor for details

A custom motor must be a three-phase synchronous motor with a quadrature encoder (either single-ended or differential outputs) in order to be able to controlled with the default firmware supplied.

Block Diagram - TODO

Functional description - TODO

...

Control Board

The default Control Board is the Digilent ARTY-Z 7010, which is delivered as part of the EDDP Kit. This manual contains information relevent to the actual use of the ARTY-Z as a Control Board within the EDDP only; all technical data and user guides and manuals for the Controller Board are provided by the controller board manufacturer (Digilent Inc.). Use of the other Control boards with the EDPS Board is also outside the scope of this manual. Primary support for other control boards is currently provided by QDESYS.

| Scroll Pagebreak |

|---|

Software

The software delivered on the SD card configures the FPGA on the ARTY-Z board with the Field-Oriented Control algorithm and starts the web server to serve the Web UI.

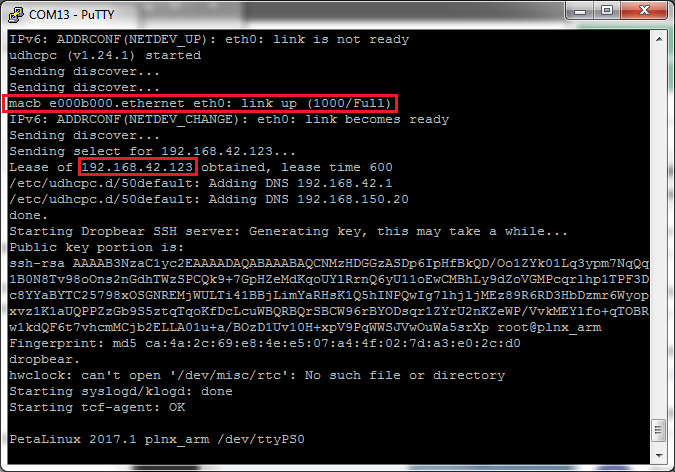

To observe the IP address of the Control Board, open the USB serial console at the baud rate of 115200 shortly after powering up the Control Board. There should be boot messages on the console and they should contain the IP address shown on the following Figure:

Figure 12: USB serial console log, with the network status message and IP address obtained via DHCP highlighted.

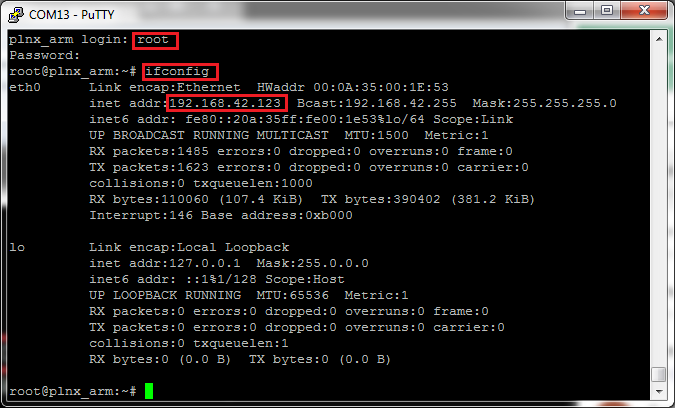

In the case the boot message was not seen for any reason, the network configuration can be seen by logging in as "root" with the password "root" and executing the command "ifconfig" as shown on the following figure:

Figure 13: USB serial console, with login dialog, command "ifconfig" and the IP address highlighted.

To access the EDDP Web UI, enter IP address of the Control Board to the web browser address field. The following page appears:

Figure 14: The Web UI.

To start the motor, click the button "Motor". The motor will make 3 rotations in order to make sure that encoder finds the initial position before starting in correct mode and the button will turn red. To stop the motor, click the button "Motor" again; the button will turn green.

The gauges show the stator current Iq and the motor speed in RPM.

To see the charts live, enable checkbox "Live charts". The following charts are available:

- Ia,Ib - shows stator currents Ia,Ib, the calculated current Ic and motor speed.

- Id,Iq - shows stator currents Id, Iq and motor speed.

- Vd,Vq - shows stator voltages Vd and Vq.

The radio buttons "Current" and "Speed" permit switching the control modes.

The sliders permit selecting the target speed and target current when in the appropriate mode. The direction radio buttons "Forward" and "Reverse" will be changed accordingly when the sign of the value is changed.

The radio buttons "Forward" and "Reverse" can be used to change the direction; the target slider will be changed accordingly.

Motor/Encoder

The Reference Motor is supplied in the EDDP Kit; see the chapter Reference Motor in the EDPS User Manual for details. Use of custom motors is outside the scope of this manual.

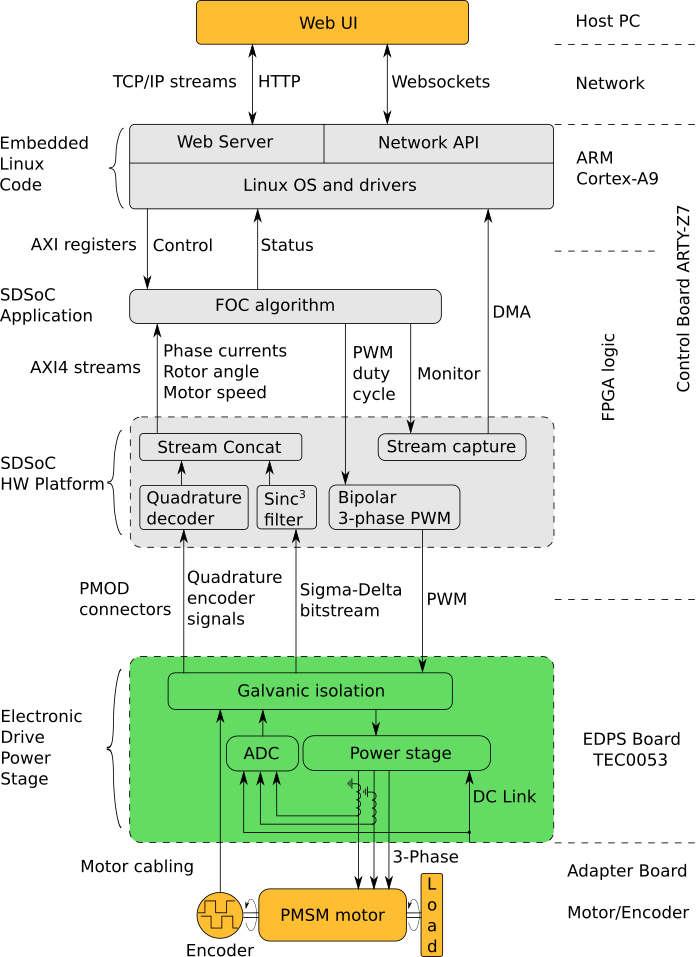

Functional description

- The data stream to the FOC algorithm consists of the concatenated stream of rotor angle and motor speeds and the stream of discrete ADC samples.

- The stream of PWM duty cycles from the FOC algorithm, which are converted to the PWM signals for the power stage.

- The stream of monitor data from the FOC algorithm, which is captured and written to the DMA buffer in the main memory. This monitor data stream consists either of phase current data, stator current data or stator voltage data.

The SDSoC Application provides the FOC algorithm. The FOC algorithm operates on the AXI4 Stream to and from the SDSoC Hardware Platform and provides a set of AXI registers to control and monitor the status of the FOC algorithm. The control registers determine the FOC algorithm operating parameters and the source of the monitor data stream.

- The Linux OS, that manages the hardware and provides execution environment for the programs to run in, which includes a TCP/IP network stack. The drivers included provide access to the control and status registers of the FOC algorithm and to the DMA buffer of the monitor data stream.

- The Network API, a server program, which provides an API built on top of Websockets protocol to control and monitor the FOC algorithm and to capture the monitor data stream.

- The Web Server, which is used to host the Web UI.

The Web UI running in a web browser on the Host PC enables use of the EDDP Kit from anywhere in the network.

Block Diagram

Figure 15: Block diagram of the EDDP.

| Page break |

|---|

FPGA resources utilization

An excerpt of the FPGA resource utilization by the FOC SDSoC Application Project is shown in the Table 2. The FPGA used on the Controller Board is Xilinx 7z010clg400-1.

The power draw of the design is about 220mW as measured by the increase of the power draw of the Control Board after configuring the FPGA.

| Type | Used | Available | Util% |

|---|---|---|---|

| Slice LUTs | 5758 | 17600 | 32.72 |

| Slice Registers | 7277 | 35200 | 20.67 |

| F7 Muxes | 33 | 8800 | 0.38 |

| RAMB36/FIFO | 21 | 60 | 35 |

| RAMB18 | 4 | 120 | 3.33 |

| DSP48E1 | 34 | 80 | 42.50 |

| BUFGCTRL | 4 | 32 | 12.50 |

| MMCME2_ADV | 1 | 2 | 50 |

Table 2: FPGA resources utilization.

List of additional documents

The additional documents, listed in the Table 3, can be downloaded from Trenz EDDP Web Hub:

| Title | Description |

|---|---|

| FOC SDSoC | Implementation of a Field-Oriented Control algorithm in C++ with Vivado SDSoC |

| SDSoC Hardware Platform ARTY-Z7 | A basis for building Vivado SDSoC applications running on an Arty-Z7 board connected to a TEC0053 |

...

| board | |

| AXI4-Stream AD7403 | An IP core for filtering the delta-sigma bitstream read from one or more ADC-s of type of AD7403 to an AXI4-Stream of samples |

| AXI4-Stream Encoder | An IP core for converting impulses from a relative index encoder with an index signal to an AXI4-Stream of position and speed data |

| AXI4-Stream PWM | An IP core for generating PWM signals according to the input AXI4-Stream |

| AXI4-Stream Concat | An IP core for concatenating AXI4-Streams |

| Web GUI | A Web UI to control and monitor an EDPS Board over the Network API |

| Network API | A communication protocol, based on Websockets, to control an EDPS board |

| Embedded Linux Code | A server program interfacing to an EDPS board and implementing the Network API and the functions of a Web Server |

Table 3: List of additional documents.

References

All resource links for other relevant documents and websites are available from Trenz EDDP Web Hub:

Document Change History

Date | Revision | Contributors | Description | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Jan Kumann | General formatting changes and small corrections. | |||||||||

2017-08-14 | v.10 | Antti Lukats, Andrei Errapart | Initial document. |

Table 4: Document change history.Include Page

| Include Page | ||||

|---|---|---|---|---|

|