...

| Scroll Title |

|---|

| anchor | Table_DRH |

|---|

| title | Design Revision History |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Vivado | Project Built | Authors | Description |

|---|

| 2020-05-08 | 2019.2 | TE0803-SK_DEMO1_noprebuilt-vivado_2019.2-build_11_ |

2020050808324620200508143345.zip

TE0803-SK_DEMO1-vivado_2019.2-build_11_ |

2020050808322920200508143327.zip | Mohsen Chamanbaz | |

|

Release Notes and Know Issues

...

| Scroll Title |

|---|

| anchor | Table_SW |

|---|

| title | Software |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Software | Version | Note |

|---|

| Vitis | 2019.2 | needed, Vivado is included into Vitis installation | | PetaLinux | 2019.2 | needed | SD Card Formatter |

| format SD Card | Win32 DiskImager |

| burn generated image on SD | | SI ClockBuilder Pro | ---- | optionialoptional |

|

Hardware

| Page properties |

|---|

|

Notes : - list of software which was used to generate the design

|

...

| Scroll Title |

|---|

| anchor | Table_AHW |

|---|

| title | Additional Hardware |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Additional Hardware | Notes |

|---|

| Cooler | It's recommended to use cooler on ZynqMP device | | USB Cable | Connect to USB2 or better USB3 Hub for proper power supply over USB | | DP Monitor | Optional HW

Not all monitors are supported, also Adapter to other Standard can make drouble.

Design was testet with DELL U2412M | | Micro USB to USB A Adapter | Adapter for USB Hub | | USB HUB | To connnect Mouse and Keyboard simultaneously | | USB Keyboard | need for Ubuntu/Debian GUI | | USB Mouse | need for Ubuntu/Debian GUI | | DP Cable | -- | | Sata Disk | Optional HW | | SATA Cable | Optional HW | | PCIe Card | Optional HW | | ETH Cable | Optional HW

Ethernet works with DHCP, but can be setup also manually | | SD Card | 16GB |

|

Content

For general structure and of the reference design, see Project Delivery - Xilinx AMD devices

Design Sources

| Scroll Title |

|---|

| anchor | Table_DS |

|---|

| title | Design sources |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Type | Location | Notes |

|---|

| Vivado | <design name>/block_design

<design name>/constraints

<design name>/ip_lib | Vivado Project will be generated by TE Scripts | | Vitis | <design name>/sw_lib | Additional Software Template for Vitis and apps_list.csv with settings automatically for Vitis app generation | | PetaLinux | <design name>/os/petalinux | PetaLinux template with current configuration |

|

...

| Page properties |

|---|

|

Notes : - prebuilt files

- Template Table:

| Scroll Title |

|---|

| anchor | Table_PF |

|---|

| title | Prebuilt files |

|---|

| | Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

File | File-Extension | Description |

|---|

| BIF-File | *.bif | File with description to generate Bin-File | | BIN-File | *.bin | Flash Configuration File with Boot-Image (Zynq-FPGAs) | | BIT-File | *.bit | FPGA (PL Part) Configuration File | | DebugProbes-File | *.ltx | Definition File for Vivado/Vivado Labtools Debugging Interface | Debian SD-Image | *.img | Debian Image for SD-Card | | Diverse Reports | --- | Report files in different formats | | Hardware-Platform-Specification-Files | *.xsa | Exported Vivado Hardware Specification for Vitis and PetaLinux | | LabTools Project-File | *.lpr | Vivado Labtools Project File | MCS-File | *.mcs | Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only) | MMI-File | *.mmi | File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only) | | OS-Image | *.ub | Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) | | Image | --- | Generic Linux kernel binary image file | | Software-Application-File | *.elf | Software Application for Zynq or MicroBlaze Processor Systems | SREC-File | *.srec | Converted Software Application for MicroBlaze Processor Systems | | Device Tree Blob File | *.dtb | Contains a Device Tree Blob |

|

|

...

| Scroll Title |

|---|

| anchor | Table_PF |

|---|

| title | Prebuilt files (only on ZIP with prebult content) |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

File | File-Extension | Description |

|---|

| BIF-File | *.bif | File with description to generate Bin-File | | BIN-File | *.bin | Flash Configuration File with Boot-Image (Zynq-FPGAs) | | BIT-File | *.bit | FPGA (PL Part) Configuration File | | DebugProbes-File | *.ltx | Definition File for Vivado/Vivado Labtools Debugging Interface | Debian SD-Image | *.img | Debian Image for SD-Card | | Diverse Reports | --- | Report files in different formats | | Hardware-Platform-Specification-Files | *.xsa | Exported Vivado Hardware Specification for Vitis and PetaLinux | | LabTools Project-File | *.lpr | Vivado Labtools Project File | | OS-Image | *.ub | Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) | | Image | --- | Generic Linux kernel binary image file | | Software-Application-File | *.elf | Software Application for Zynq or MicroBlaze Processor Systems | | Device Tree Blob File | *.dtb | Contains a Device Tree Blob |

|

...

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

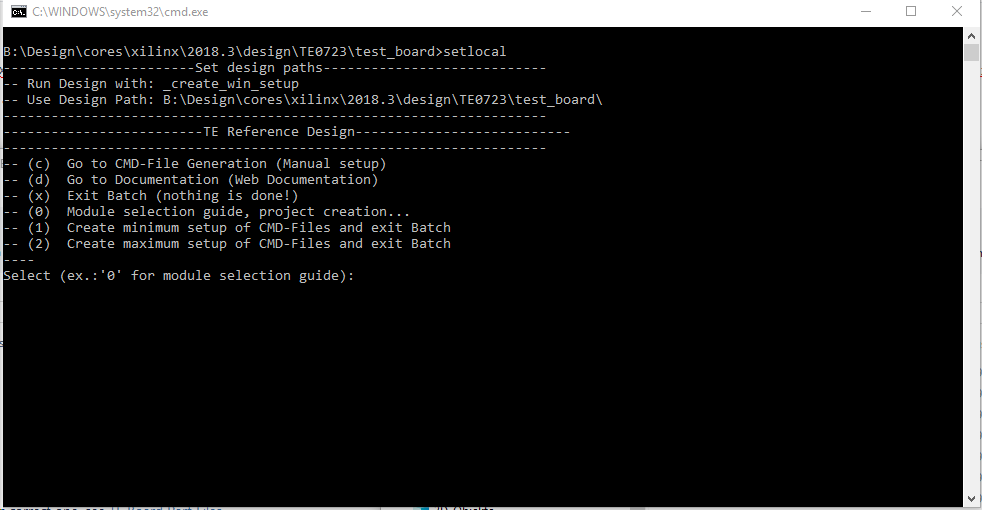

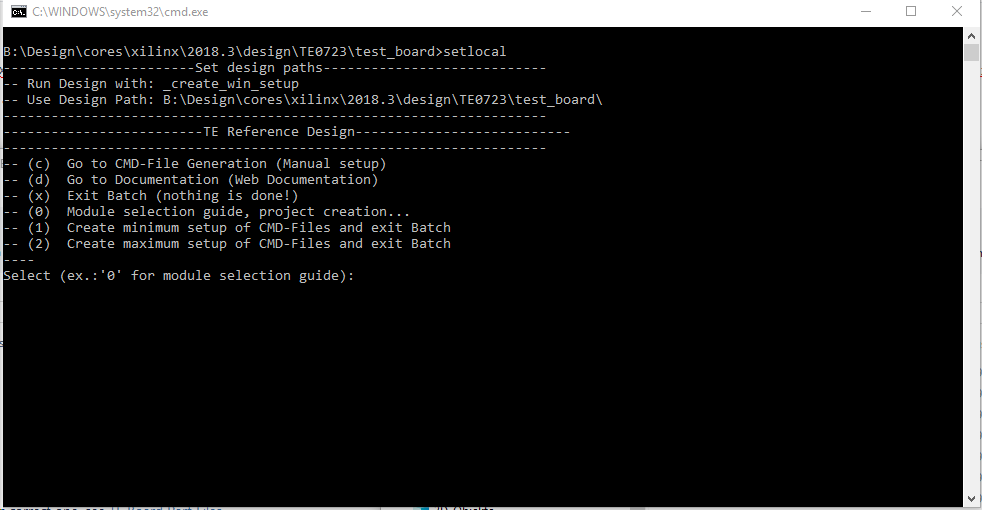

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter to start "Module Selection Guide"

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process)

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see alsoTE Board Part Files- Important: Use Board Part Files, which ends with *_tebf0808

- Create XSA and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Create Linux (bl31.elf, uboot.elf , image and Image and system.dtb) with exported XSA

- XSA is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux/

- Script für debian/ubuntu ausführenExecute the script file for Debian/Ubuntu

- Add Linux files (bl31.elf, uboot.elf , image and Image and system.dtb) to prebuilt folder

- "prebuilt\os\petalinux\<ddr size>" or "prebuilt\os\petalinux\<short name>"

- Generate Programming Files with Vitis

- Run on Vivado TCL: TE::sw_run_vitis -all

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_vitis

Note: TCL scripts generate also platform project, this must be done manuelly in case GUI is used. See Vitis

- Vorbereiten Preparing SD für card for SD Filesystem und and hard disk for HD Filesystem → siehe See Programming section

Launch

...

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

Get prebuilt boot binaries

...

| Code Block |

|---|

|

/include/ "system-conf.dtsi"

/ {

chosen {

xlnx,eeprom = &eeprom;

bootargs= "console=ttyPS0,115200 earlycon clk_ignore_unused earlyprintk root=/dev/mmcblk1p2 rootfstype=ext4 rw rootwait cma=1024M";

/* notes: root=/dev/mmcblk1p2 fürfor SD undand root=/dev/sda für Harddisk wird überfor hard disk will be changed automatically by executing debian/ubuntu script passend erstellt */

};

};

/* notes:

serdes: // PHY TYP see: dt-bindings/phy/phy.h

*/

/* default */

/* SD */

&sdhci1 {

disable-wp;

no-1-8-v;

};

/* USB */

&dwc3_0 {

status = "okay";

dr_mode = "host";

snps,usb3_lpm_capable;

snps,dis_u3_susphy_quirk;

snps,dis_u2_susphy_quirk;

phy-names = "usb2-phy","usb3-phy";

phys = <&lane1 4 0 2 100000000>;

maximum-speed = "super-speed";

};

/* ETH PHY */

&gem3 {

phy-handle = <&phy0>;

phy0: phy0@1 {

device_type = "ethernet-phy";

reg = <1>;

};

};

/* QSPI */

&qspi {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

flash0: flash@0 {

compatible = "jedec,spi-nor";

reg = <0x0>;

#address-cells = <1>;

#size-cells = <1>;

};

};

/* I2C */

&i2c0 {

i2cswitch@73 { // u

compatible = "nxp,pca9548";

#address-cells = <1>;

#size-cells = <0>;

reg = <0x73>;

i2c-mux-idle-disconnect;

i2c@0 { // MCLK TEBF0808 SI5338A, 570FBB000290DG_unassembled

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

};

i2c@1 { // SFP TEBF0808 PCF8574DWR

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

};

i2c@2 { // PCIe

#address-cells = <1>;

#size-cells = <0>;

reg = <2>;

};

i2c@3 { // SFP1 TEBF0808

#address-cells = <1>;

#size-cells = <0>;

reg = <3>;

};

i2c@4 {// SFP2 TEBF0808

#address-cells = <1>;

#size-cells = <0>;

reg = <4>;

};

i2c@5 { // TEBF0808 EEPROM

#address-cells = <1>;

#size-cells = <0>;

reg = <5>;

eeprom: eeprom@50 {

compatible = "atmel,24c08";

reg = <0x50>;

};

};

i2c@6 { // TEBF0808 FMC

#address-cells = <1>;

#size-cells = <0>;

reg = <6>;

};

i2c@7 { // TEBF0808 USB HUB

#address-cells = <1>;

#size-cells = <0>;

reg = <7>;

};

};

i2cswitch@77 { // u

compatible = "nxp,pca9548";

#address-cells = <1>;

#size-cells = <0>;

reg = <0x77>;

i2c-mux-idle-disconnect;

i2c@0 { // TEBF0808 PMOD P1

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

};

i2c@1 { // i2c Audio Codec

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

/*

adau1761: adau1761@38 {

compatible = "adi,adau1761";

reg = <0x38>;

};

*/

};

i2c@2 { // TEBF0808 Firefly A

#address-cells = <1>;

#size-cells = <0>;

reg = <2>;

};

i2c@3 { // TEBF0808 Firefly B

#address-cells = <1>;

#size-cells = <0>;

reg = <3>;

};

i2c@4 { //Module PLL Si5338 or SI5345

#address-cells = <1>;

#size-cells = <0>;

reg = <4>;

};

i2c@5 { //TEBF0808 CPLD

#address-cells = <1>;

#size-cells = <0>;

reg = <5>;

};

i2c@6 { //TEBF0808 Firefly PCF8574DWR

#address-cells = <1>;

#size-cells = <0>;

reg = <6>;

};

i2c@7 { // TEBF0808 PMOD P3

#address-cells = <1>;

#size-cells = <0>;

reg = <7>;

};

};

};

|

...