...

| Scroll Title |

|---|

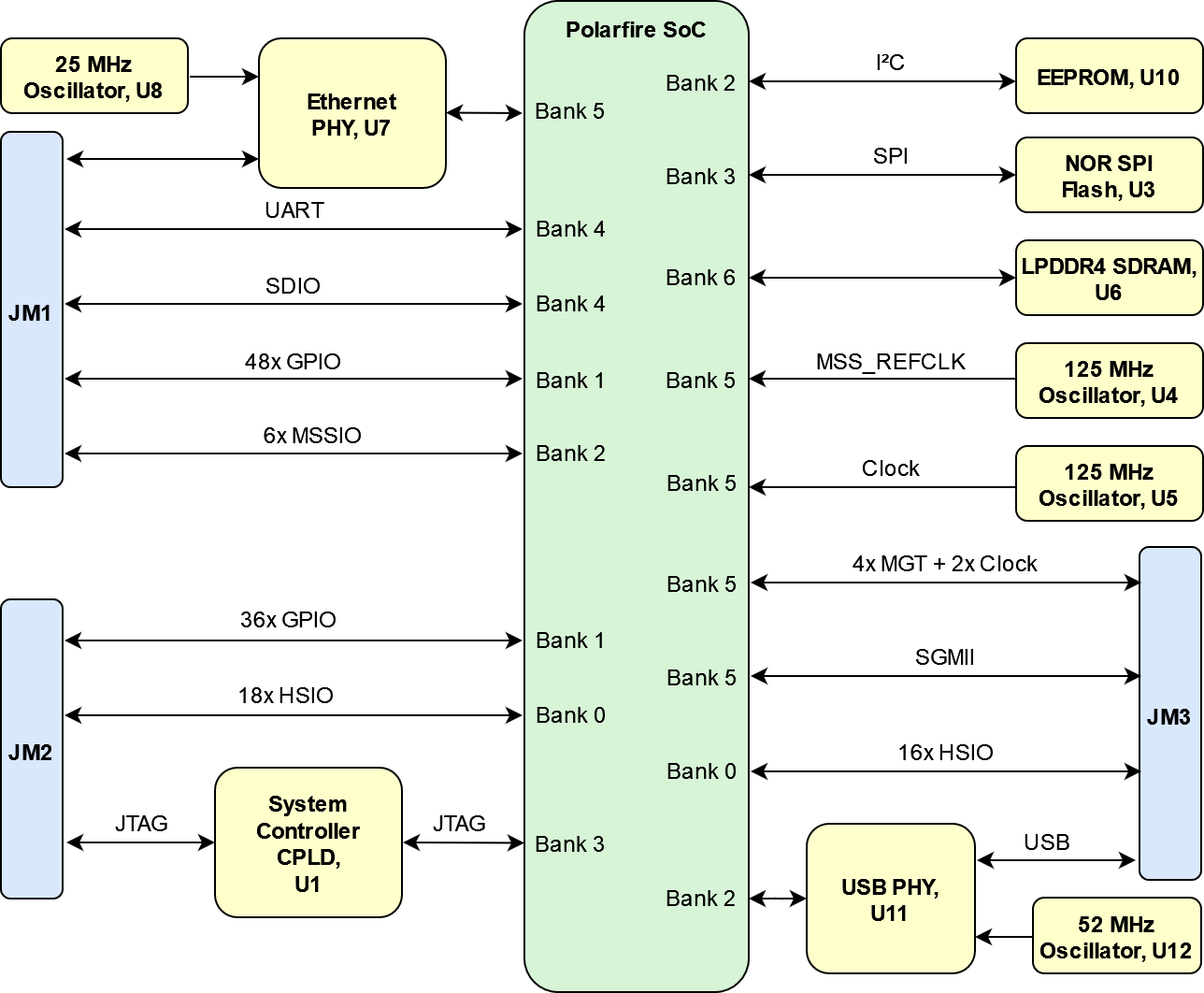

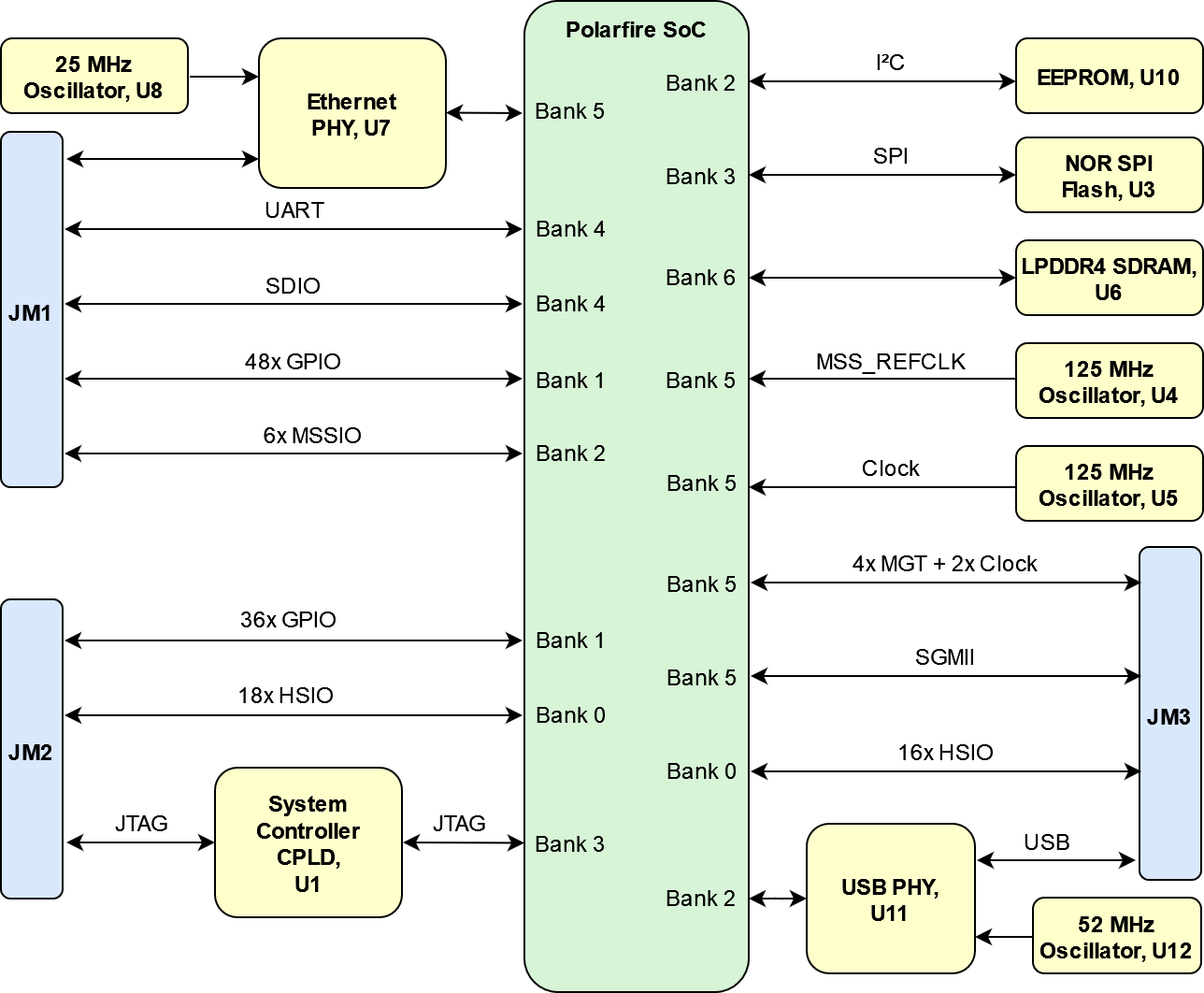

| anchor | Figure_OV_BD |

|---|

| title | TExxxx block diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | true |

|---|

| |

|---|

| diagramName | Figure_OV_BD |

|---|

| simpleViewer | true |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | top |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| diagramWidth | 1427644 |

|---|

| revision | 1114 |

|---|

|

|

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed Image Added Image Added |

|

Main Components

...

| Scroll Title |

|---|

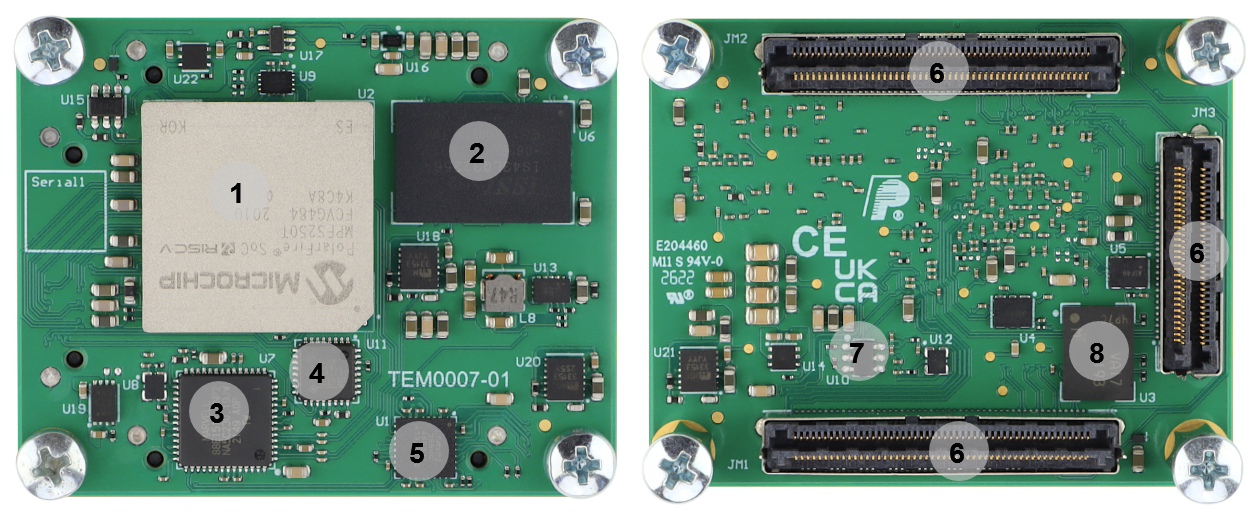

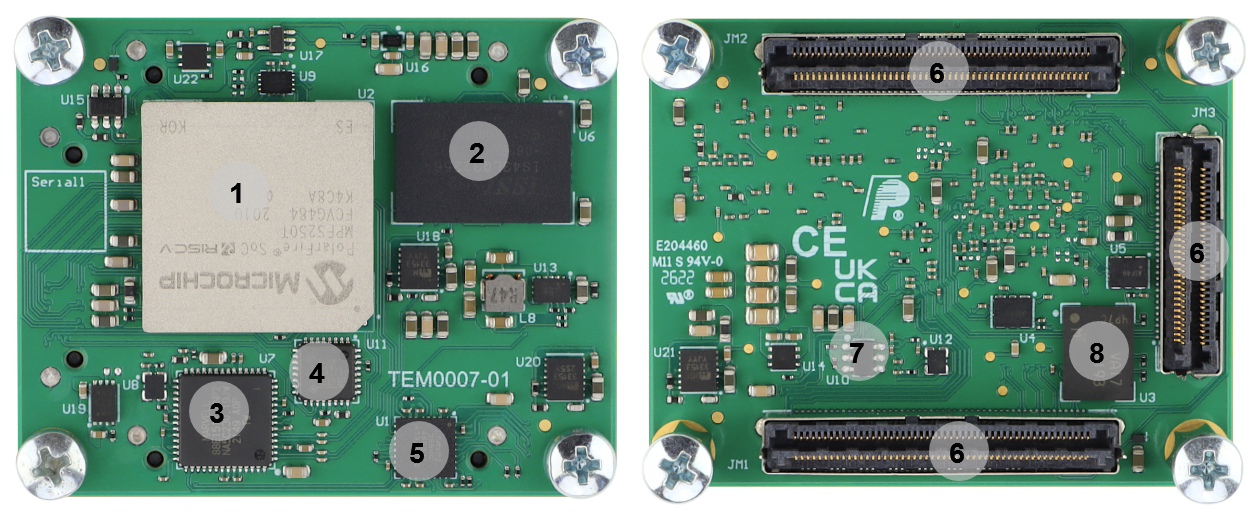

| anchor | Figure_OV_MC |

|---|

| title | TExxxx main components |

|---|

|

| Scroll Ignore |

|---|

Create DrawIO object here: Attention if you copy from other page, objects are only linked. |

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

|

- ...

- ...

- ...

|

|---|

| draw.io Diagram |

|---|

| border | true |

|---|

| |

|---|

| diagramName | TEM0007_OV_MC |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | top |

|---|

| lbox | true |

|---|

| diagramWidth | 641 |

|---|

| revision | 4 |

|---|

|

|

| Scroll Only |

|---|

Image Added Image Added

|

|

- Microsemi Polarfire SoC MPFS250T, U2

- 1 GByte LPDDR4 SDRAM, U6

- Integrated 10/100/1000 Mbps Energy Efficient Ethernet Transceiver, U7

- Highly Integrated Full Featured Hi-Speed USB 2.0 ULPI Transceiver, U11

- Lattice Semiconductor MachXO2 System Controller CPLD, U1

- B2B Connector Samtec Razor Beam, JM1...3

- EEPROM, U10

- Serial NOR Flash, U3

Initial Delivery State

| Page properties |

|---|

|

Notes : Only components like EEPROM, QSPI flash can be initialized by default at manufacture. If there is no components which might have initial data ( possible on carrier) you must keep the table empty |

...

| Scroll Title |

|---|

| anchor | Table_OV_IDS |

|---|

| title | Initial delivery state of programmable devices on the module |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Storage device name | Content | Notes |

|---|

SPI NOR Flash, U4U3 | Not programmed | - | | EEPROM, U17U10 | Pre-programmed globally unique MAC | - | | System Controller CPLD, U1 | Standard firmware | - |

|

...

| Scroll Title |

|---|

| anchor | Table_SIP_B2B |

|---|

| title | General PL SoC I/O to B2B connectors information |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| FPGA Bank | B2B Connector | I/O Signal Count | Voltage Level | Notes |

|---|

| 0 | JM2 |

50 | 18 | 1.2 V / 1.35 V / 1.5 V / 1.8 V | HSIO dependent on VCCIOD | | 0 | JM3 | 16 | 1.2 V / 1.35 V / 1.5 V / 1.8 V | HSIO dependent on VCCIOD | | 1 |

JM218| 48 | 1.2 V / 1.5 V / 1.8 V / 2.5 V / 3.3 V |

HSIO | GPIO dependent on VCCIOB | | 1 |

JM320| 36 | 1.2 V / 1.5 V / 1.8 V / 2.5 V / 3.3 V |

HSIO 262GPIO | | MSSIO (14 signals including UART and SDIO) | | 5 | JM3 | 4 | - | SGMII (1 pairs for TX / 1 pairs for RX) | | 5 |

SERDES | JM3 | 16 | - | SERDES (4 pairs for TX / 4 pairs for RX) | | 5 | JM3 | 4 | - | SERDES CLK (2 pairs for RX) |

|

JTAG Interface

JTAG access to the TEM0006 SoM through B2B connector JM2.

...