Page History

...

| Scroll Title | ||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||

|

Requirements

...

| Scroll Title | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||

|

Download

The Trenz Electronic Reference Designs and Demos are usable with the specified Microsemi Libero / SoftConsole version. Usage of a different Microsemi / Libero / SoftConsole software versions is not recommended.

...

The Hardware and Software Reference / Demo -Designs Projects are available as a prebuild zip archive. The archive contains at least a Libero Hardware Project and a SoftConsole Workspace folder, they were created and tested in windows environment.

This SoftConsole Workspace contains the Software Reference Design Project Hello World and the Demo Webserver, the demo is offered in two variants. For software development via the IDE SoftConsole a The board configuration file "microsemi-smartfusion2-smartberry-ddr.cfg" is included.required for the usage of the Software projects via the IDE SoftConsole.

Board configuration file

Copy the board configuration file "microsemi-smartfusion2-smartberry-ddr.cfg" along the following (default installation) path inside you Microsemi / SoftConsole installation into the folder board:

...

Only necessary for running the Demo Webserver:

The demo is configured to establish a network connection via the DHCP protocol, therefore, if a a free router port is used, no further port setup is required.

If a "direct Ethernet Connection" between Host PC and module is used, the user must know how to setup this connection type. Further down in this chapter is explained how to setup the Demo Webserver and recompile it, so that it uses a static IP.

...

The Device Manager is accessible via "Right mouse click context menu" from the Windows Start Menu Button. When these devices are not visible, the driver installation through libero could be faulty.

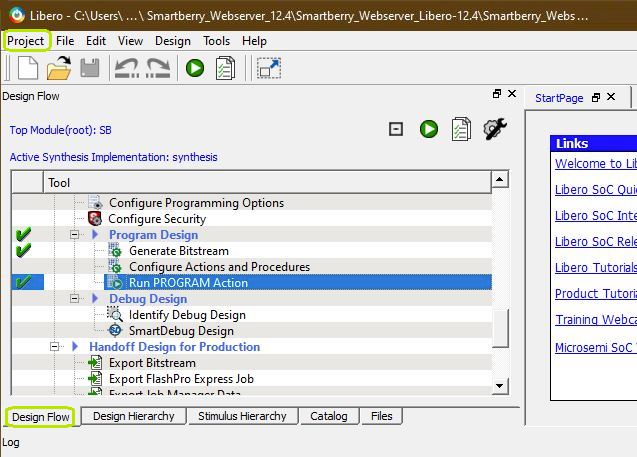

Programming the Hardware design

Programming of the Hardware reference Design requires to open the FPGA Design IDE Libero.

Open Libero 12.4, in the to left corner, open the Webserver Demo hardware project inside the extracted ZIP download via "Project > Open Project" and point the file dialogue to the demo archives hardware project:The Hardware Reference Design can be opened via "Project > Open Project" in the top right corner of Libero (picture above - upper green rectangle). A file dialogue opens, point the dialogue along the extracted download to the folder containing the Hardware Reference Design.

Disk :\ Path-to-the-Demo-archive \ Extracted ZIP-archive \ Libero-X.y_Referenz-Design\

double Double left mouse click onto the project file "Referenz-Design_XY .prjx" to open it. The board is automatically selected and setup to be flashed by Libero.

In the upper left section of Libero, select the tab "Design Flow" (picture above - lover green rectangle) and flash it to the board via "Program Design > and double left mouse click onto "Run PROGRAM Action" (picture above - row with blue background).

...

UART connection

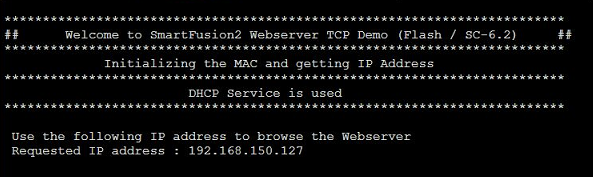

Before flashing the Webserver Demo server application any Software Project to the module, open a comport terminal to the boards comport, so that it's messages about the used IP Address and executed Demo-Variant can be captured.

demo into the module is a three fold process, programming the FPGA Design, establishing a COM-port terminal connection to the module and programming the web server program code into the modules FPGA's embedded flash or it's external DDR memory.

...

can be captured.

Programming a Software project

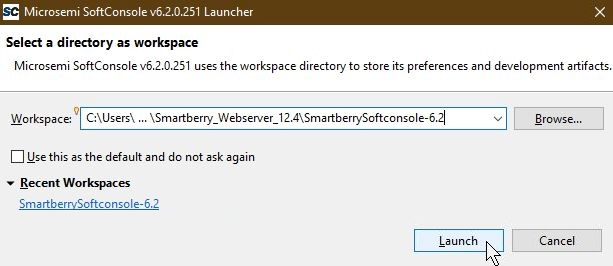

Open SoftConsole 6.2 and press "Browse..." to point the "Workspace: " to the folder "Softconsole-6.2-Workspace" inside the demo foldernear the right edge. A file dialogue opens, point the dialogue along the extracted download to the folder containing the SoftConsole Workspace.

Disk :\ Path-to-the-Demo_-archive \ Extracted ZIP-archive \ Softconsole-6X.2y-Workspace \

Confirm your selectioin by pressing "Ok" , the dialogue closes, and open The SoftConsole by pressing "Launch" .

Subsequently the program opens and shows the software Subsequently the program opens and shows the software project's who are contained inside the workspace to the left, under "Project Explorer".

The demo is offered in two variants:

- Smartberry_Webserver_6.2 - Application code is stored to the FPGA's embedded non-volatile memory (eNVM)

- Smartberry_Webserver_DDR_6.2 - Application code is stored to the FPGA's external volatile memory (DDR3/L SDRAM) and lost during power down

Before flashing the demo, open a comport terminal to the boards comport, so that its messages about the used IP Address and executed Demo-Variant can be captured.

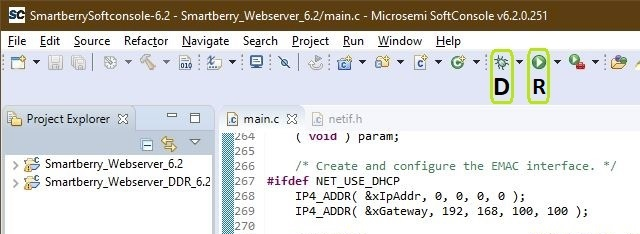

To simply run the demo press the triangle right to the button marked with a "R" in the picture above and select a variant of the demo.

MOVE up to beginning!!!!!:------------------------

Pressing the triangle next to the button marked with "D" let you select which variant to be executed in debug mode.

Debug controls - Resume - Pause - Stop

Switch between Debug and Run perspective (upper right corner program window)

Demo Variants

The two demo projects "Smartberry_Webserver_6.2" and "Smartberry_Webserver_DDR_6.2" are identical variants of the demo, they only differ in their memory location. The first one is stored in embedded non volatile memory (eNVM) and the later is stored volatile in the external DDR ram and therefore lost during power down.

Static IP configuration

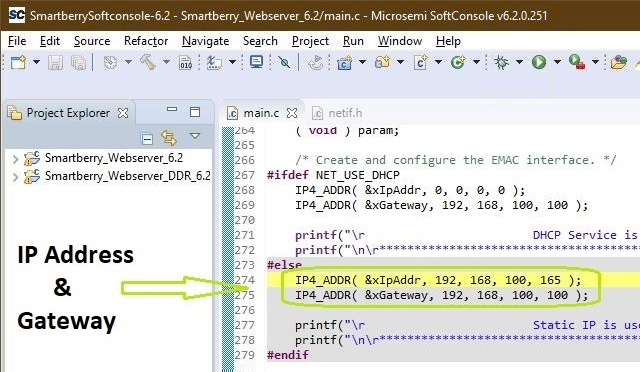

To disengaging the DHCP mode one has to setup up an IP and Gateway Address in the code unit "main.c" line 274. Alternativly, the demo hosts IP Address can be changed.

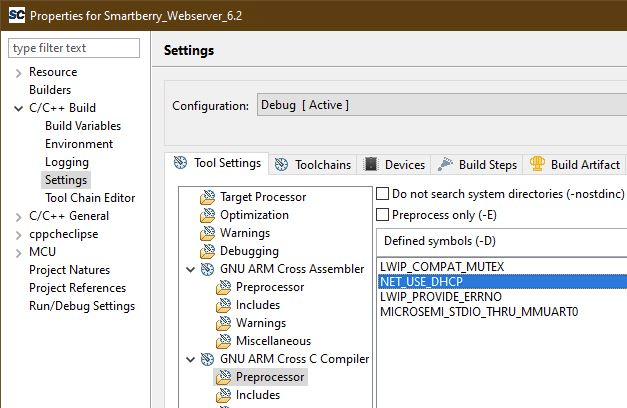

Furthermore the corresponding compiler flag needs to be deleted in the project setting. To do so, in the "Project Explorer" tab, right mouse click onto the project and select Properties in the appearing menu.

In the left section of the properties window select "C/C++ Build > Settings" in the right section select the tab "Tool Settings > GNU ARM Cross C Compiler > Preprocessor" under "Defined symbols (-D)" delete the compiler flag "NET_USE_DHCP" and press "Apply". Confirm the following dialogue and press "Cancel".

Lastly, the project needs to be recompiled. In the top menu of the SoftConsole select "Project > Build ALL / Build Project".

Warnings should not affect the demo. can be ignored.

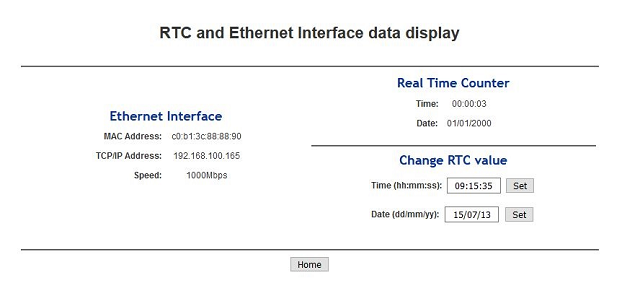

Pictures of the Webserver pages

Open a new tab in a web browser and enter the IP Address from the comport terminal. The start page, picture below, should appear immediately.

...

To simply run a Project, press the triangle right to the button marked with a "R" in the picture above and select a variant of the demo.

Pressing the triangle next to the button marked with "D" let you select which variant to be executed in debug mode.

Debug controls - Resume - Pause - Stop

Switch between Debug and Run perspective (upper right corner program window)

System Design - Libero

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

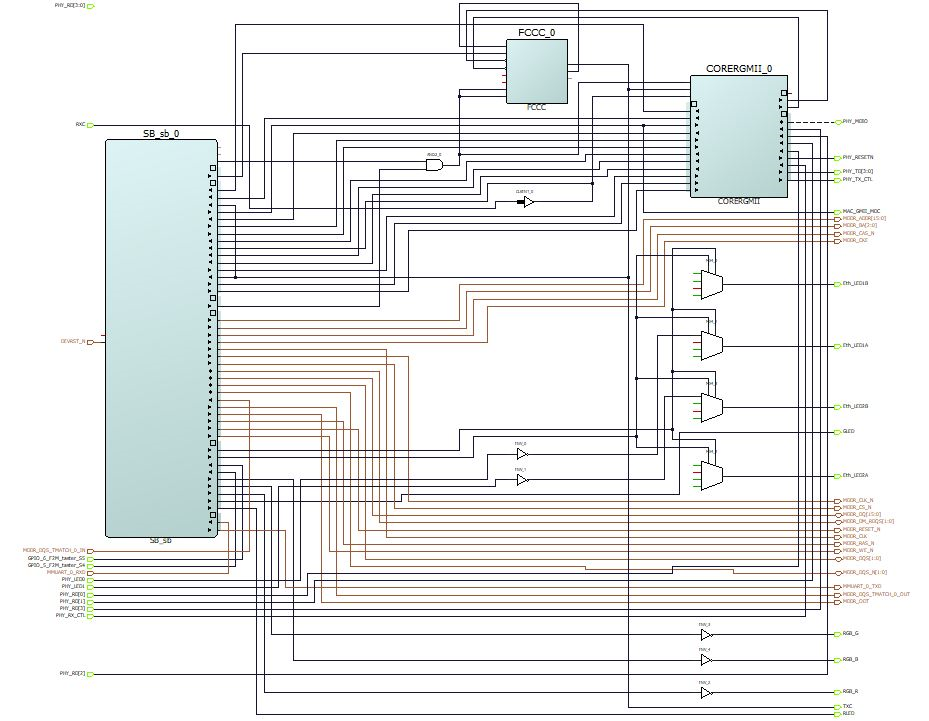

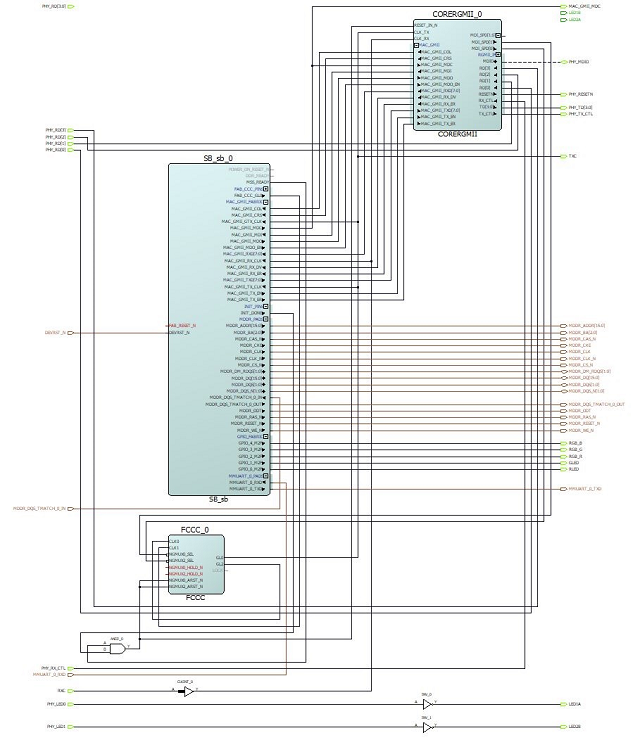

Smart Design

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

Constrains

All LED Pins ( R/G -LED , Eth_LED-X-A/B , RGB_R/G/B ) are configured as "Outputs" and the voltage standard is selected to be "LVCMOS33".

The user tasters ( GPIO_5/6_F2M_taster_S4/5 ) are configured as "Inputs" and the voltage standard is selected to be "LVCMOS33".

Software Design - SoftConsole

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Application

| Page properties | ||||

|---|---|---|---|---|

|

...

System Design - Libero

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Smart Design

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

Constrains

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLNONE [current_design]

|

Software Design - SoftConsole

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

Application

| Page properties | ||||

|---|---|---|---|---|

| ||||

---------------------------------------------------------- FPGA Example scuMCS Firmware to configure SI5338 and Reset System. srec_spi_bootloaderTE modified 2019.2 SREC Bootloader to load app or second bootloader from flash into DDR Descriptions:

xilisf_v5_11TE modified 2019.2 xilisf_v5_11

---------------------------------------------------------- Zynq Example: zynq_fsblTE modified 2019.2 FSBL General:

Module Specific:

zynq_fsbl_flashTE modified 2019.2 FSBL General:

ZynqMP Example: | ||||

---------------------------------------------------------- FPGA Example scuMCS Firmware to configure SI5338 and Reset System. srec_spi_bootloaderzynqmp_fsblTE modified 2019.2 SREC Bootloader to load app or second bootloader from flash into DDR Descriptions:

FSBL General:

Module Specific:

zynqmp_fsbl_flashTE modified 2019.2 xilisf_v5_11

FSBL General:

zynqmp_pmufwXilinx default PMU firmware. ---------------------------------------------------------- Zynq General Example: zynqhello_fsblTE modified 2019.2 FSBL General:

Module Specific:

zynq_fsbl_flashTE modified 2019.2 FSBL General:

ZynqMP Example: ---------------------------------------------------------- zynqmp_fsblTE modified 2019.2 FSBL General:

Module Specific:

zynqmp_fsbl_flashTE modified 2019.2 FSBL General:

zynqmp_pmufwXilinx default PMU firmware. ---------------------------------------------------------- General Example: hello_te0820Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output. u-bootU-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin. |

SDK template in ./sw_lib/sw_apps/ available.

zynqmp_fsbl

TE modified 2019.2 FSBL

General:

- Modified Files: xfsbl_main.c, xfsbl_hooks.h/.c, xfsbl_board.h/.c(search for 'TE Mod' on source code)

- Add Files: te_xfsbl_hooks.h/.c (for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device Name

Module Specific:

- Add Files: all TE Files start with te_*

- Si5345 Configuration

- OTG+PCIe Reset over MIO

- I2C MUX for EEPROM MAC

zynqmp_fsbl_flash

TE modified 2019.2 FSBL

General:

- Modified Files: xfsbl_initialisation.c, xfsbl_hw.h, xfsbl_handoff.c, xfsbl_main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

zynqmp_pmufw

Xilinx default PMU firmware.

hello_te0808

te0820Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output. u-bootU-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin. |

Smartberry_Webserver_...

The demo projects "Smartberry_Webserver_X.y" and "Smartberry_Webserver_DDR_X.y" are identical variants of the demo, they only differ in their memory location:

- Smartberry_Webserver_X.y - Application code is stored to the FPGA's embedded non-volatile memory (eNVM)

- Smartberry_Webserver_DDR_X.y - Application code is stored to the FPGA's external volatile memory (DDR3/L SDRAM) and lost during power down

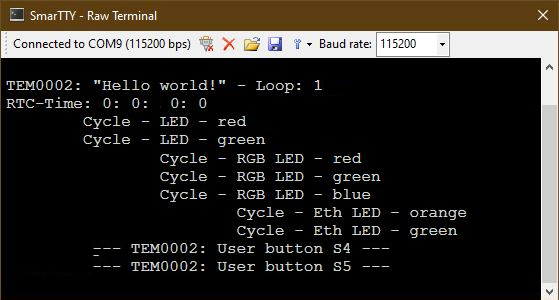

UART output:

Static IP configuration

To disengaging the DHCP mode one has to setup up an IP and Gateway Address in the code unit "main.c" roughly at line 270. Alternativly, the demo hosts IP Address can be changed.

Furthermore the corresponding compiler flag needs to be deleted in the project setting. To do so, in the "Project Explorer" tab, right mouse click onto the project and select Properties in the appearing menu.

In the left section of the properties window select "C/C++ Build > Settings" in the right section select the tab "Tool Settings > GNU ARM Cross C Compiler > Preprocessor" under "Defined symbols (-D)" delete the compiler flag "NET_USE_DHCP" and press "Apply". Confirm the following dialogue and press "Cancel".

Lastly, the project needs to be recompiled. In the top menu of the SoftConsole select "Project > Build ALL / Build Project".

Warnings should not affect the demo. can be ignored.

Smartberry_HelloWorld_...

Hello Hello TE0808 is a Xilinx Hello World example as endless loop instead of one console output. Each loop lights up each LED. The user buttons respond with a message at any time.

UART output:

Appx. A: Change History and Legal Notices

...