Page History

...

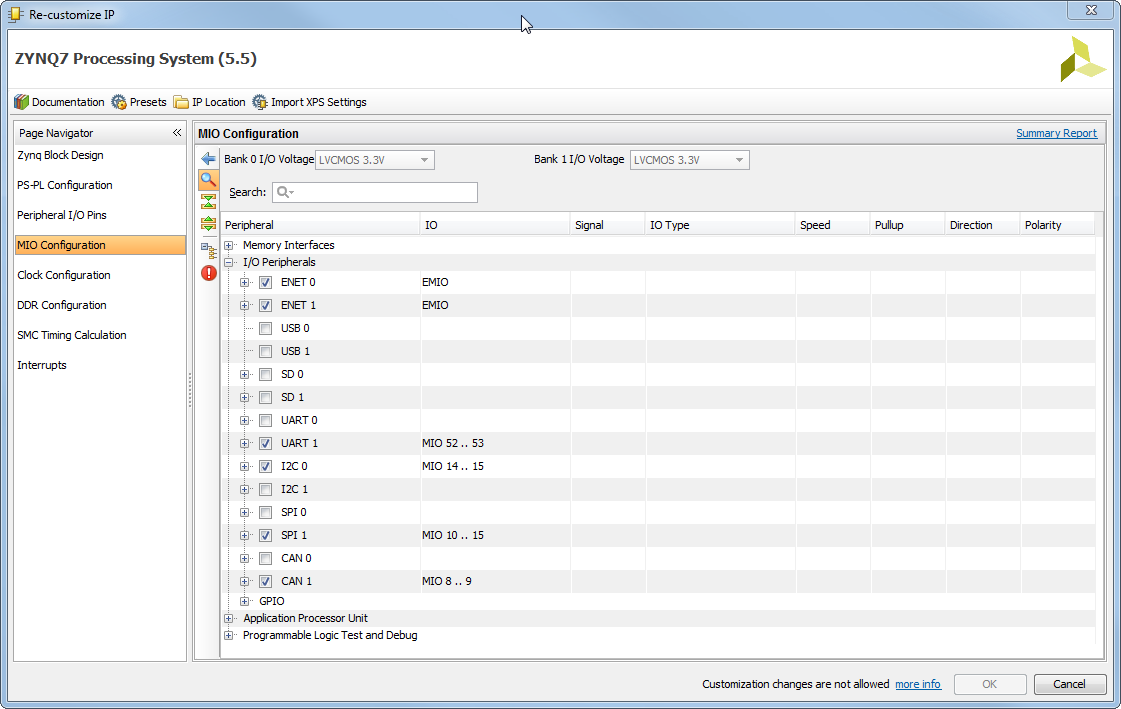

Recommended Peripheral mapping for MIO Voltage bank 0.

Mapping of on-board peripherals.

Note: UART must not be on MIO52,53 different mapping is possible.

PL Peripherals

Both Ethernet PHY IC's are connected to PL pins in Bank 34, all PHY IC pins are connected to FPGA pins, there is no sharing of signals for the two PHY's. PHY's must be operated in MII Mode, other modes are not supported. It is possible to use PS ENET0 or ENET1 via EMIO routing or Ethernet IP Cores implemented in PL Fabric.

...

Note: the availability LIN depends on the Module version and assembly option.

Ethernet

| ETH1 | ETH2 | Pullup | Notes | |

|---|---|---|---|---|

| TD+ | J3.58 | J3. | on-board | |

| TD- | J3.56 | J3. | on-board | |

| RD+ | J3.52 | J3. | on-board | |

| RD- | J3.50 | J3. | on-board | |

| LED1 | J3.55 | J3.23 | on-board | |

| LED2 | J3.53 | J3.21 | on-board | |

| LED3 | J3.51 | J3.19 | on-board |

Overview

Content Tools