Page History

...

Labtools can be used if pre-built images for FPGA are available, for debugging also the debug netlist files is needed.

Example Debug Session

TE0715-xx-15 Micromodule with "VIO only" labtools pre-built design. This design does not depend on the PS subsystem being initialized by the Zynq Bootrom.

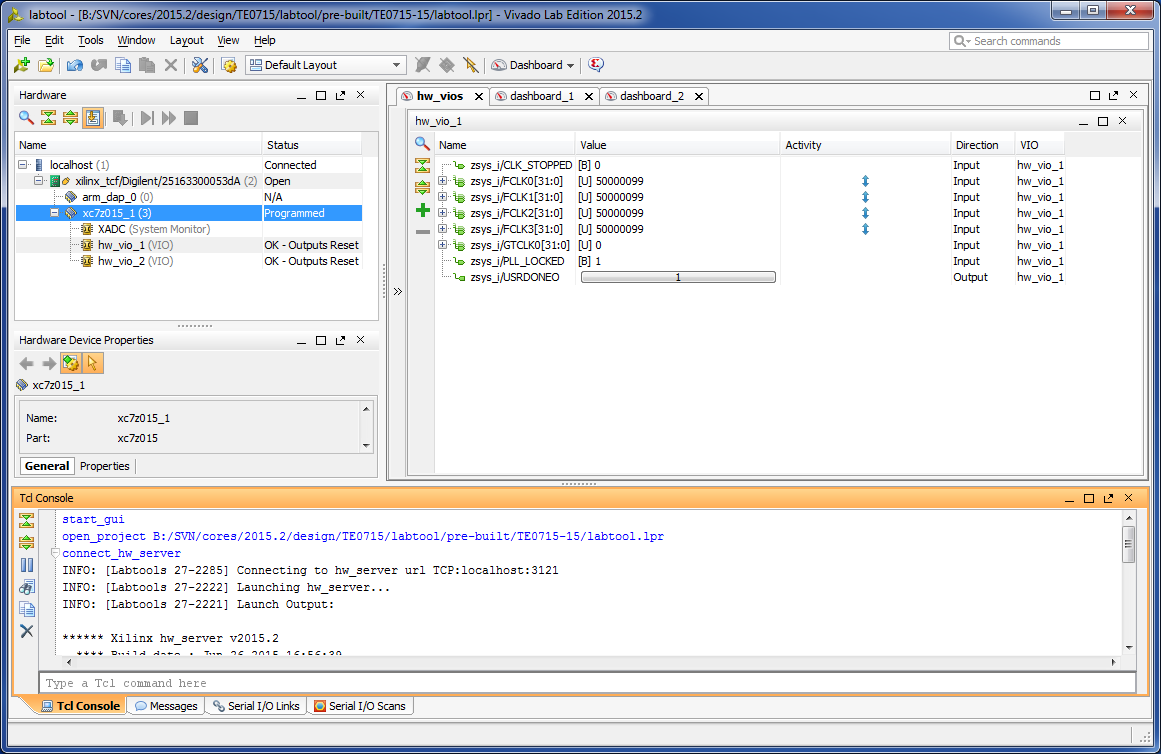

ZYNQ PS Fabric clocks can be monitored (the frequency depends on the FSBL settings). Frequency measurement reference is taken from Si5338 PLL supplied 125MHz clock. If this is not running then the PL fabric PLL flags would show clock stopped. In this dashboard it is also possible to toggle the output of DONE pin, setting it low would lit the DONE LED on TE0715.

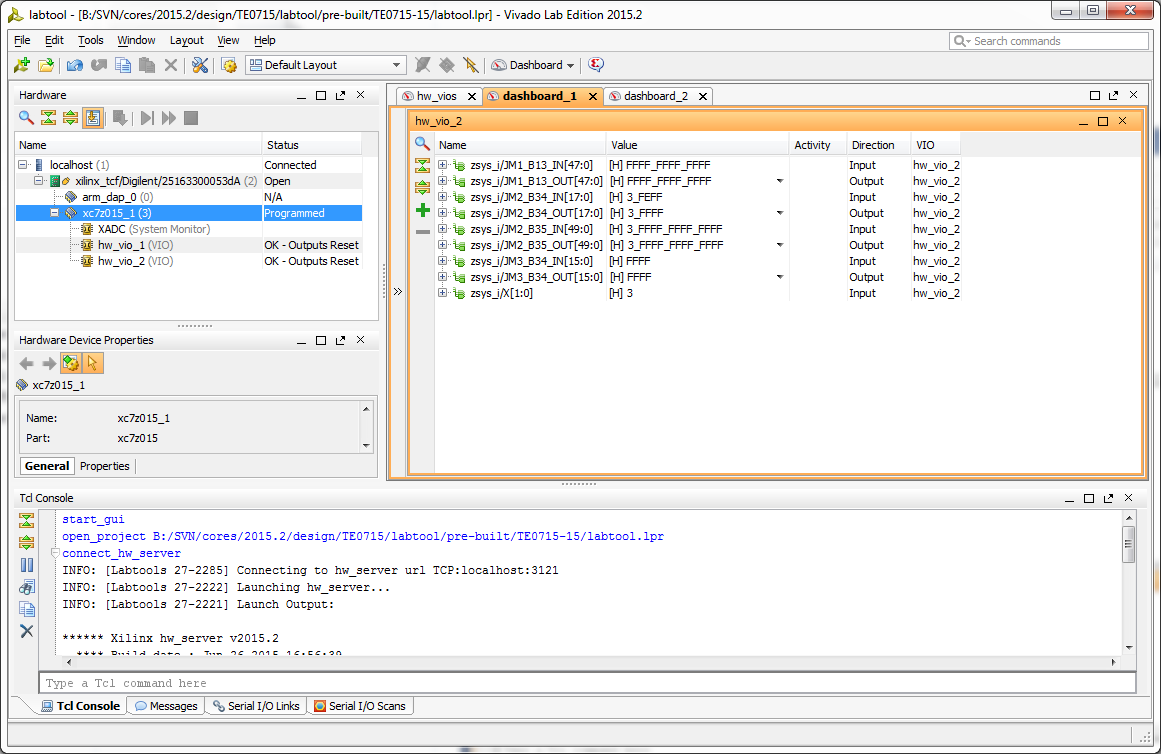

B2B I/O Pins can be monitored in this dashboard, if no external peripherals drive the I/O then all pins would show 1 as input value. It is also possible to force I/O pins to low by writing 0 into VIO OUT port.

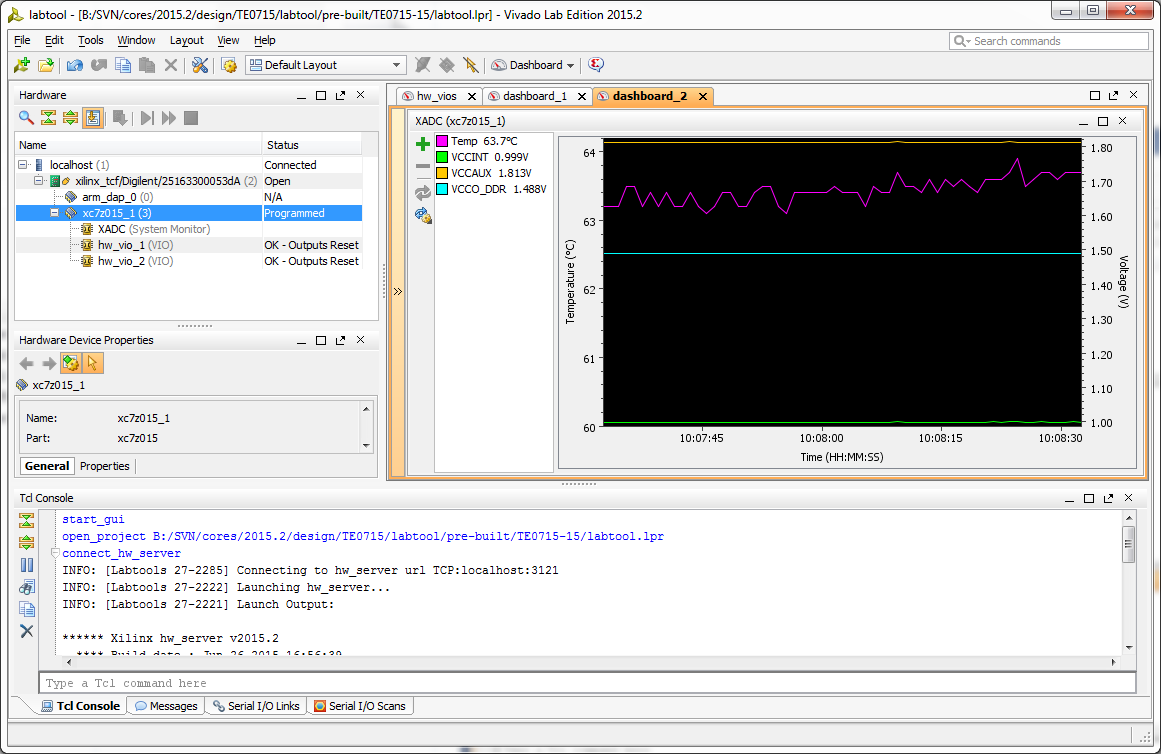

XADC can also be monitored to check the temperature and voltage sensor values.