Page History

This is simple demo for DC (Direction Conversion) SDR function use in FPGA, for analog input XADC is used (Zynqberry mic input).

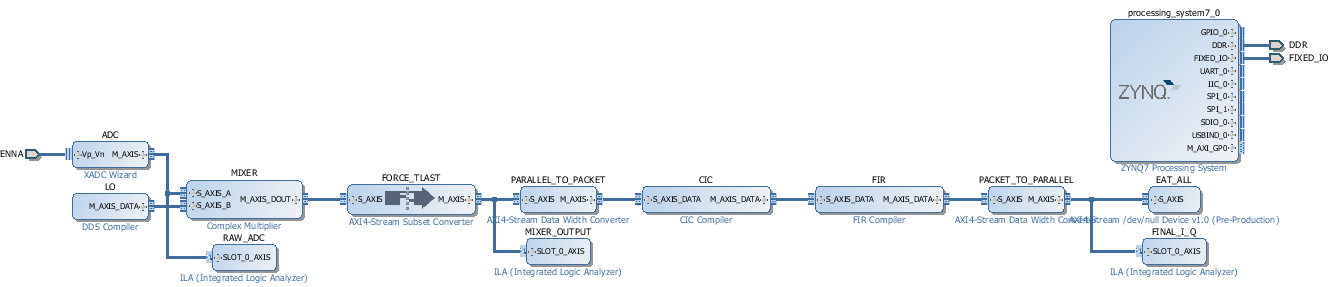

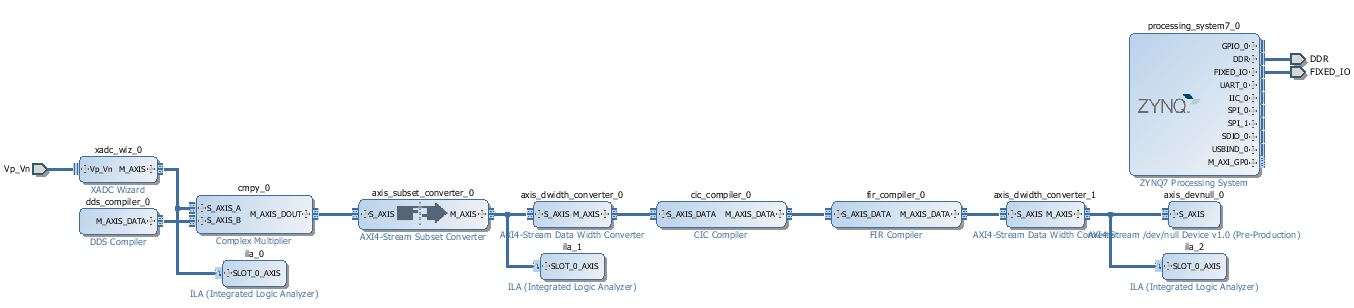

IPI BD for the SDR demo.

...

DDS Compiler Wizard is used to generate LO (local oscillator) Sinus and Cosinus outputs. LO output is multiplied with the input from XADC. All AXI4-Streaming components run from single system clock (130MHz). XADC asserts TVALID with the rate of ADC sampling, that is 1 MHz. To make DDS to work at 130MHz TREADY input of the DDS Output stream must be tied to 1.

...

After FIR filter AXI stream datawidht converter is used again to get convert the interleaved samples of I and Q as single AXIS stream TDATA word. The processing is terminated by AXI stream DEVNULL that eats all. For visualization and data capture ILA Logic Analyzer IP cores are inserted. For test purposes the LO frequency was set to 134KHz (this is close to WSPR band where beacons are expected to be present in frequency band).

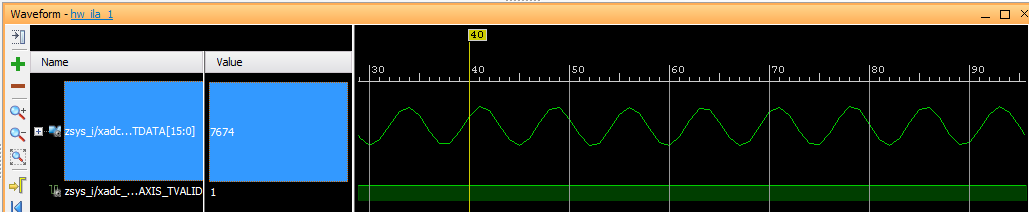

XADC Raw data, capturing 135MHz 135KHz signal from Zynqberry mic input.

...