Page History

...

| HTML |

|---|

<!-- Link to the base folder of the module (remove de/ or en/ from the URL): for example: https://shop.trenz-electronic.de/Download/?path=Trenz_Electronic/Modules_and_Module_Carriers/4x5/4x5_Carriers/TE0703/ --> |

| Scroll Ignore |

|---|

| Scroll pdf ignore | |

|---|---|

Table of Contents

|

...

| Scroll Title | ||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||

|

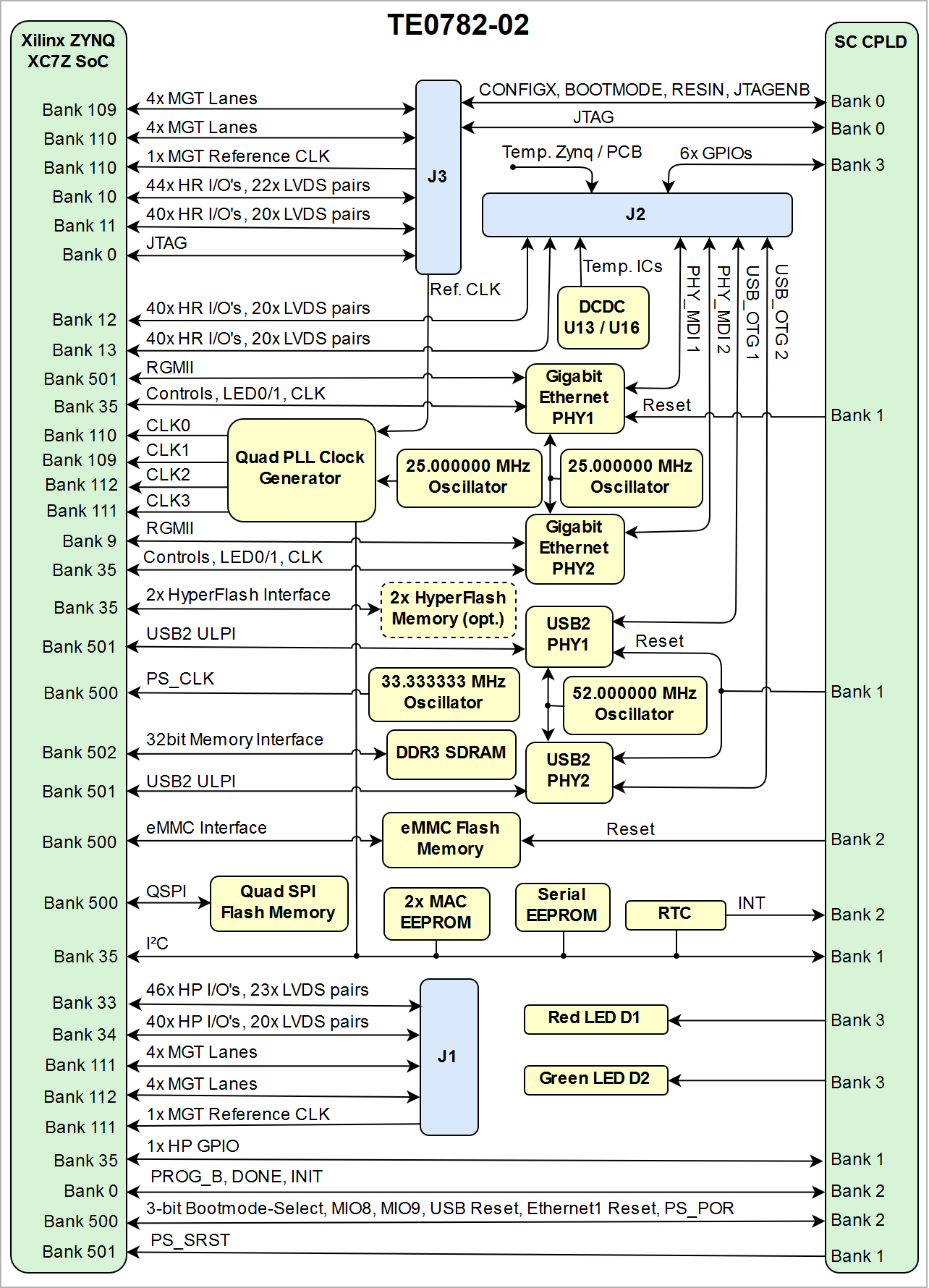

Main Components

...

The Xilinx Zynq-7000 SoC used on the TE0782 module has 16 MGT transceiver lanes. All of them are wired directly to B2B connectors J1 and J3. MGT (Multi Gigabit Transceiver) lane consists of one transmit and one receive (TX/RX) differential pairs, four signals total per one MGT lane with data transmission rates up to 12.5Gb/s per lane (Xilinx GTX transceiver). Following table lists lane number, FPGA bank number, transceiver type, signal schematic name, board-to-board pin connection and FPGA pins connection:

Board to

| Bank | Type | Lane | Signal Name | B2B Pin | FPGA Pin |

|---|---|---|---|---|---|

| 109 | GTX | 0 |

|

|

|

| 1 |

|

|

| ||

| 2 |

|

|

| ||

| 3 |

|

|

| ||

| 110 | GTX | 0 |

|

|

|

| 1 |

|

|

| ||

| 2 |

|

|

| ||

| 3 |

|

|

| ||

| 111 | GTX | 0 |

|

|

|

| 1 |

|

|

| ||

| 2 |

|

|

| ||

| 3 |

|

|

| ||

| 112 | GTX | 0 |

|

|

|

| 1 |

|

|

| ||

| 2 |

|

|

| ||

| 3 |

|

|

|

...

eMMC Flash memory device (U15) is connected to the Zynq PS MIO bank 500 pins MIO10..MIO15. eMMC chips MTFC4GMVEA-4M IT (Flash NAND-IC 2x 16 Gbit) is used with 4 GByte of memory density.

...

DDR3L Memory

By default TE0782-02 module has two 16-bit wide IM (Intelligent Memory) IM4G16D3FABG-125I DDR3L SDRAM (DDR3-1600 Speedgrade) chips (U10, U19) arranged into 32-bit wide memory bus providing total of 1 GBytes of on-board RAM.

...

Two quad SPI compatible serial bus flash memory for FPGA configuration file storage is provided by Spansion S25FL256SAGBHI20 (U38) with 256 Mbit (32 MByte) memory density. After configuration completes the remaining free memory can be used for application data storage. All four SPI data lines are connected to the FPGA allowing x1, x2 or x4 data bus widths to be used. The maximum data transfer rate depends on the bus width and clock frequency.

...

Board to Board Connectors

The TE0782 SoM has three 160-pin double-row ASP-122952-01 Samtec connectors on the bottom side which mate with ASP-122953-01 Samtec connectors on the baseboard. Mating height is 5 mm.Include Page 8.5 x 8.5 SoM QSH and QTH B2B Connectors 8.5 x 8.5 SoM QSH and QTH B2B Connectors

Variants Currently In Production

...

| Date | Revision | Contributors | Description | ||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||||||

| 2018-07-20 | v.33 | John Hartfiel |

| ||||||||||||||||||||||||||

2018-07-19 Jul 2018 | v.32 | Ali Naseri |

| ||||||||||||||||||||||||||

| 2018-05-15 | v.22 | Ali Naseri |

| ||||||||||||||||||||||||||

| 2018-01-31 | Ali Naseri |

| |||||||||||||||||||||||||||

| 2017-06-07 | Jan Kumann |

| |||||||||||||||||||||||||||

| 2017-05-23 | v.13 | Jan Kumann |

| ||||||||||||||||||||||||||

| 2017-01-24 | v.12 | Ali Naseri |

| ||||||||||||||||||||||||||

| 2016-06-27 | v.10 | Ali Naseri, Jan Kumann |

| ||||||||||||||||||||||||||

| -- | all |

|

|

Disclaimer

| Include Page | ||||

|---|---|---|---|---|

|