...

| Scroll Title |

|---|

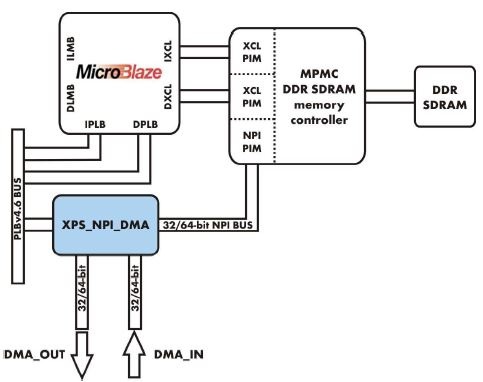

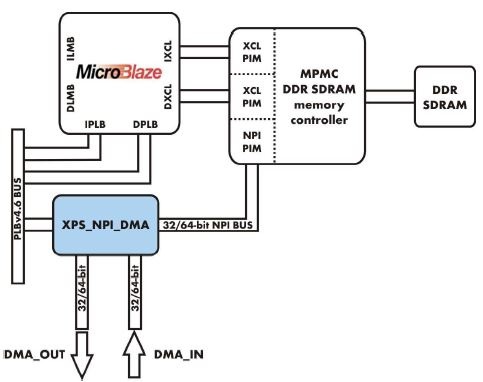

| title | System integration block scheme |

|---|

|

Image Added Image Added Image Removed Image Removed

|

The XPS_NPI_DMA has 4 interfaces:

...

| Scroll Title |

|---|

| title | XPS_NPI_DMA Core Design Parameters |

|---|

|

| Feature/Description | Parameter Name | Allowable Values | Default Value | VHDL Type |

|---|

| System Parameters | | Target FPGA family | C_FAMILY | spartan3, spartan3e,

spartan3a,

spartan3adsp,

spartan3an, virtex2p,

virtex4, qvirtex4,

qrvirtex4, virtex5 | virtex5 | string | | PLB Parameters | | PLB base address | C_BASEADDR | Valid Address | None | std_logic_vector | | PLB high address | C_HIGHADDR | Valid Address | None | std_logic_vector | PLB least significant

address bus width | C_SPLB_AWIDTH | 32 | 32 | integer | | PLB data width | C_SPLB_DWIDTH | 32, 64, 128 | 32 | integer | | Shared bus topology | C_SPLB_P2P | 0 = Shared bus

topology

| 0 | integer | PLB master ID bus

Width | C_SPLB_MID_WIDTH | log2(C_SPLB_NUM_

MASTERS) with a

minimum value of 1

| 1 | integer | | Number of PLB masters | C_SPLB_NUM_MASTERS | 1 - 16 | 1 | integer | Width of the slave data

bus | C_SPLB_NATIVE_DWIDTH | 32 | 32 | integer | | Burst support | C_SPLB_SUPPORT_BURSTS | 0 = No burst support | 0 | integer | | XPS_NPI_DMA Parameters | | NPI bus data width | C_NPI_DATA_WIDTH | 32, 64 | 32 | integer | | Byte swap input data | C_SWAP_INPUT | 0, 1 | 0 | integer | | Byte swap output data | C_SWAP_OUTPUT | 0, 1 | 0 | integer | Writing padding value

if number of bytes does

not match multiple of

packet size | C_PADDING_BE | 0, 1 (zeros, ones) | 0 | integer |

|

XPS_NPI_DMA I/O Signal Descriptions

| Scroll Title |

|---|

| title | XPS_NPI_DMA I/O Signal Descriptions |

|---|

|

Name

| Interface | I/O | Initial State | Description |

|---|

| NPI_Clk | - | I | - | Memory clock | | ChipScope[0:63] | - | O | - | Debug port | | IP2INTC_Irpt | - | O | 0 | Interrupt request

LEVEL_HIGH | | Capture_data[(C_NPI_DATA_WIDTH-1):0] | DMA_IN | I | - | Sync DMA Input data | | Capture_valid | DMA_IN | I | - | Sync DMA Input valid strobe | | Capture_ready | DMA_IN | O | 0 | DMA Input is ready flag | | Output_data[(C_NPI_DATA_WIDTH-1):0] | DMA_OUT | O | - | DMA Output data,

Sync to NPI_Clk | | Output_valid | DMA_OUT | O | 0 | DMA Output valid strobe,

sync to NPI_Clk | | Output_ready | DMA_OUT | I | 1 | External Output ready | | NPI_Addr[31:0] | MPMC_PIM | O | zeros | NPI address data | | NPI_AddrReq | MPMC_PIM | O | 0 | NPI address request | | NPI_AddrAck | MPMC_PIM | I | - | NPI address acknowledge | | NPI_RNW | MPMC_PIM | O | 0 | NPI read now write | | NPI_Size[3:0] | MPMC_PIM | O | 0 | NPI packet size

See below for info | | NPI_RdModWr | MPMC_PIM | O | 0 | NPI read mod write

(not used) | | NPI_WrFIFO_Data[(C_NPI_DATA_WIDTH-1):0] | MPMC_PIM | O | zeros | NPI write FIFO data vector | | NPI_WrFIFO_BE[(C_NPI_DATA_WIDTH/8-1):0] | MPMC_PIM | O | ones | NPI write FIFO byte enable mask

(alway ones) | | NPI_WrFIFO_Push | MPMC_PIM | O | 0 | NPI write FIFO data valid strobe | | NPI_RdFIFO_Data[(C_NPI_DATA_WIDTH-1):0] | MPMC_PIM | I | - | NPI read FIFO data vector | | NPI_RdFIFO_Pop | MPMC_PIM | O | 0 | NPI read FIFO data read strobe | | NPI_RdFIFO_RdWdAddr[3:0] | MPMC_PIM | I | - | NPI read FIFO read write addr

(not used) | | NPI_WrFIFO_Empty | MPMC_PIM | I | - | NPI write FIFO empty flag | | NPI_WrFIFO_AlmostFull | MPMC_PIM | I | - | NPI write FIFO almost full flag | | NPI_WrFIFO_Flush | MPMC_PIM | O | 0 | NPI write FIFO reset | | NPI_RdFIFO_Empty | MPMC_PIM | I | - | NPI read FIFO empty flag | | NPI_RdFIFO_Flush | MPMC_PIM | O | 0 | NPI read FIFO reset | | NPI_RdFIFO_Latency[1:0] | MPMC_PIM | O | ‘’01’’ | NPI read FIFO latency | | NPI_InitDone | MPMC_PIM | I | - | MPMC init done flag | | OTHERS ARE PLBv4.6 SIGNALS | PLBv4.6 | - | - | - |

|

Writing and reading to/from DMA_IN and DMA_OUT ports

...

| Scroll Title |

|---|

| title | XPS_NPI_DMA I/O Signal Descriptions |

|---|

|

| BUS | DMA_IN | DMA_OUT |

|---|

| Bus width | 32 or 64 bit | 32 or 64 bit | | Clock synchronous to | NPI_Clk | NPI_Clk | | “valid” width | Multiple cycles possible | Multiple cycles possible |

|

| Scroll Title |

|---|

| title | DMA high speed communication ports principle of operation |

|---|

|

|

...

| Scroll Title |

|---|

| title | XPS_NPI_DMA Core Registers |

|---|

|

Base Address + Offset (hex) | Register Name | Access Type | Default Value (hex) | Description |

|---|

| NPI_DMA_CORE IP Core Grouping | C_BASEADDR + 00 | CR | R/W | 0x00000000 | Control Register | | C_BASEADDR + 04 | WSA | R/W | 0x00000000 | Write Start Address Register | | C_BASEADDR + 08 | WBR | R/W | 0x00000000 | Write Bytes Register | | C_BASEADDR + 0C | RSA | R/W | 0x00000000 | Read Start Address Register | | C_BASEADDR + 10 | RBR | R/W | 0x00000000 | Read Bytes Register | | C_BASEADDR + 14 | RJR | R/W | 0x00000000 | Read Jumps Register | | C_BASEADDR + 18 | SR | Read | 0x00000000 | Status Register | | C_BASEADDR + 1C | WCR | Read | WSA | Write Address Counter Register | C_BASEADDR + 20 | RCR | Read | WBR | Read Address Counter Register | | IPIF Interrupt Controller Core Grouping | C_BASEADDR + 200 | INTR_DISR | Read | 0x00000000 | interrupt status register | C_BASEADDR + 204 | INTR_DIPR | Read | 0x00000000 | interrupt pending register | C_BASEADDR + 208 | INTR_DIER | Write | 0x00000000 | interrupt enable register | C_BASEADDR + 218 | INTR_DIIR | Write | 0x00000000 | interrupt id (priority encoder) register | C_BASEADDR + 21C | INTR_DGIER | Write | 0x00000000 | global interrupt enable register | C_BASEADDR + 220 | INTR_IPISR | Read | 0x00000000 | ip (user logic) interrupt status register | | C_BASEADDR + 228 | INTR_IPIER | Write | 0x00000000 | ip (user logic) interrupt enable register |

|

| Note |

|---|

| The First (LSB) interrupt from user_logic is masked on the left!! |

...

| Scroll Title |

|---|

| title | Control Register bits |

|---|

|

| Bits | Name | Description Reset | Value |

|---|

31 | rst | Peripheral soft reset (not self resettable) | 0 | | 30 | wr_fifo_rst | Write FIFO reset (not self resettable) | 0 | | 29 | rd_fifo_rst | Read FIFO reset (not self resettable) | 0 | | 28 | wr_loop | Write loop – continuous transfer | 0 | | 27 | rd_loop | Read loop – continuous transfer | 0 | 26 | wr_test | Write test – writes 32bit counter to memory | 0 | | 25 | xfer_write | Write data flag (starts/stops xfer) | 0 | | 24 | xfer_read | Read data flag (starts/stops xfer) | 0 | | 20-23 | wr_block_size | Write block size | 0x0 | | 16-19 | rd_block_size | Read block size | 0x0 | | 15 | use_rd_jump | Enables transpose | 0 |

|

Write Start Address Register (WSA)

...

| Scroll Title |

|---|

| title | Status Register (SR) |

|---|

|

| Bits | Name | Description | Reset Value |

|---|

| 31 | wr_xfer_done | Write xfer done flag (always 0 if wr_loop = '1') | 1 | | 30 | rd_xfer_done | Read xfer done flag (always 0 if wr_loop = 1) | 1 | | 24-27 | xfer_status | Write xfer status (bit 27 = wr_fifo_full) | 0 |

|

Write Address Counter Register (WCR)

...

| Scroll Title |

|---|

| title | Write block size available |

|---|

|

| Write block size | wr_block_size | C_NPI_DATA_WIDTH | type of transfer | Implemented |

|---|

| 4 bytes | X”0” | 32 | 1 word xfer |  | | 8 bytes | X”0” | 64 | 2 words xfer |  | | 16 bytes | X”1” | 32-64 | 4-word cache-line burst |  | | 32 bytes | X”2” | 32-64 | 8-word cache-line burst |  | | 64 bytes | X”3” | 32-64 | 16-word burst |  | | 128 bytes | X”4” | 32-64 | 32-word burst |  | | 256 bytes | X”5” | 64 | 64-word burst |  |

|

| Scroll Title |

|---|

| title | Read block size available |

|---|

|

| Read block size | rd_block_size | C_NPI_DATA_WIDTH | type of transfer | Implemented |

|---|

| 4 bytes | X”0” | 32 | 1 word xfer |  | | 8 bytes | X”0” | 64 | 2 words xfer |  | | 16 bytes | X”1” | 32-64 | 4-word cache-line burst |  , not tested , not tested | | 32 bytes | X”2” | 32-64 | 8-word cache-line burst |  , not tested , not tested | | 64 bytes | X”3” | 32-64 | 16-word burst |  | | 128 bytes | X”4” | 32-64 | 32-word burst |  | | 256 bytes | X”5” | 64 | 64-word burst |  |

|

Example 1

Example of single write transfer from address 0x1C000000 to 0x1C00FFFF using 32-word burst

...