Page History

...

| Scroll Only (inline) |

|---|

Refer to https://wiki.trenz-electronic.de/display/PD/TE0741 for downloadableonline version of this manual and the rest of available documentation. |

...

The TE0741 module is available in four different logic densities (70T, 160T, 325T and 410T). The 70T and 160T devices can be programmed with the free Xilinx Vivado WebPACK software. Further information about the Kintex-7 FPGA can be found in the Xilinx document 7 Series FPGA's Overview (DS180).

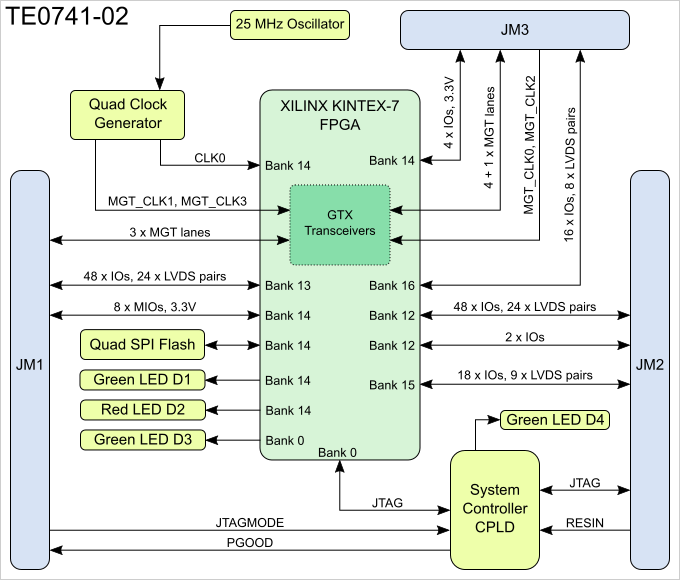

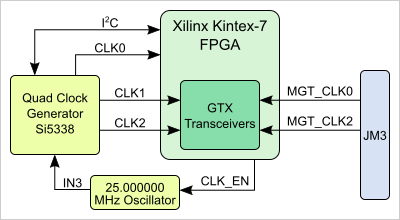

Block Diagram

Figure 1: TE0741 Block diagram.

Main Components

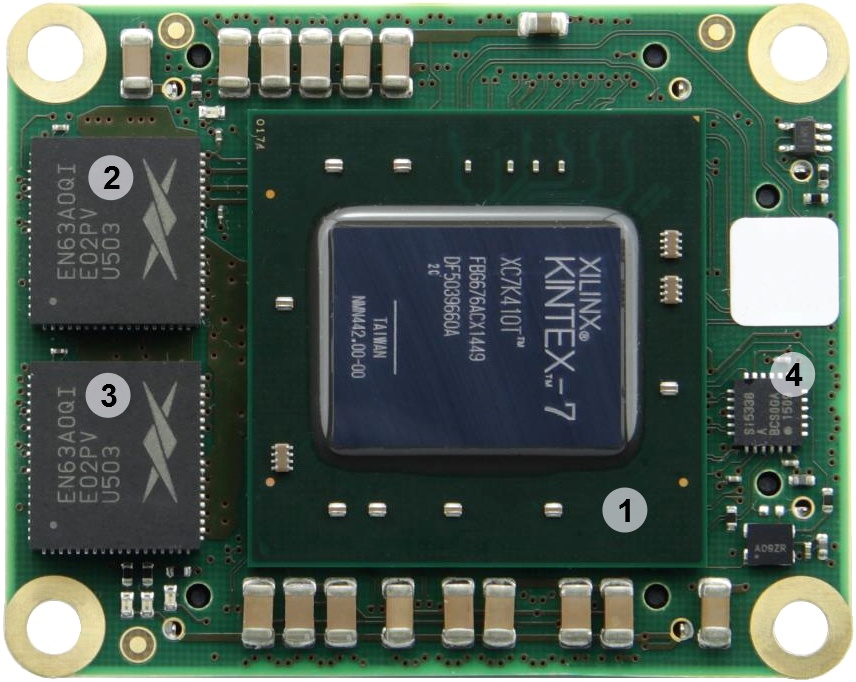

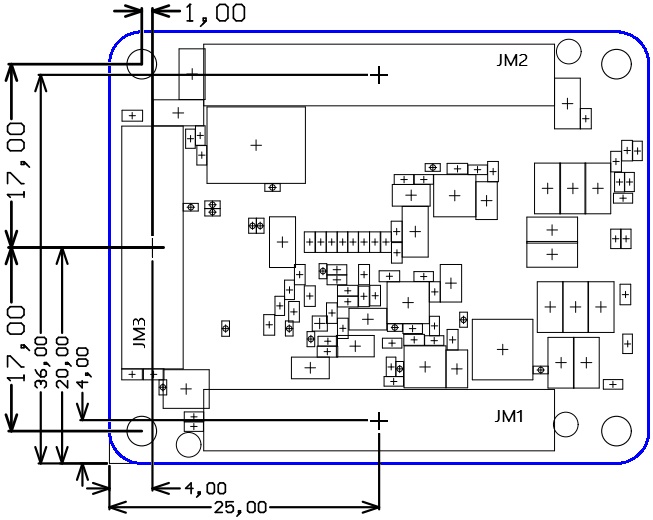

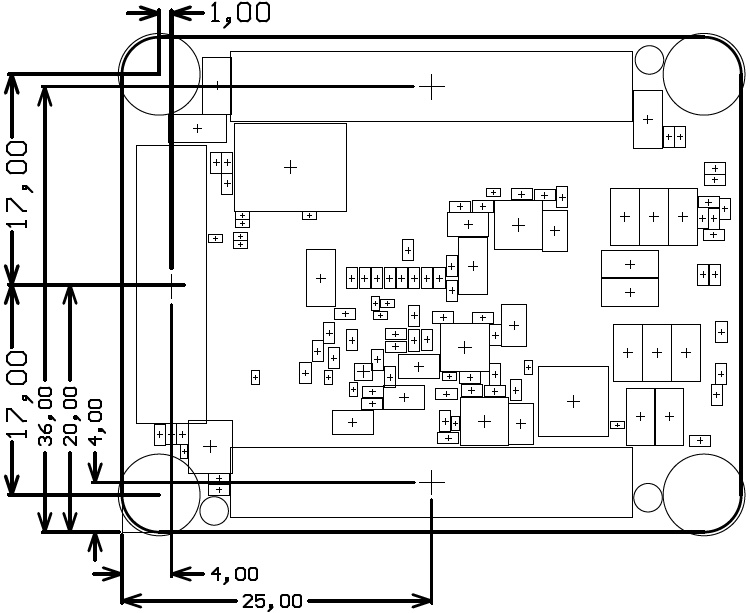

Figure 2: TE0741-02 module.

Key Features

- Industrial-grade Xilinx Kintex-7 FPGA

...

Key Features

- Industrial-grade Xilinx Kintex-7 FPGA module (70T*, 160T*, 325T, 410T)

* Devices supported by the free Xilinx Vivado WebPACK software. - 256-Mbit (32-MByte) Quad SPI Flash memory (for configuration and operation) accessible through:

- FPGA

- JTAG port (SPI indirect (Bus width x4))

- 8 GTX transceivers

- FPGA configuration through:

- JTAG (B2B connector)

- SPI Flash memory

- 25 MHz low jitter oscillator with shutdown control

- Programmable quad PLL clock generator

- On-board high-efficiency DC-DC converters

- GTX voltage regulators with control enable

- Core voltage regulator: 20A (2 x Enpirion DC-DC regulators with load-sharing)

- Supply voltages: either 3.3V or 3.3V and 5V

- Plug-on module with two 100-pin and one 60-pin high-speed hermaphroditic stacking strips

- Up to 144 (94 for 70T) FPGA I/O pins available on B2B strips (up to 65 LVDS pairs possible)

- 2 user LED's, 1 DONE FPGA pin LED, 1 System Controller status LED

- System management and power sequencing

- AES bit-stream encryption

- eFUSE bit-stream encryption

- Evenly spread supply pins for good signal integrity

- Assembly options for cost or performance optimization available on request

...

- module (70T*, 160T*, 325T, 410T)

* Devices supported by the free Xilinx Vivado WebPACK software. - 256-Mbit (32-MByte) Quad SPI Flash memory (for configuration and operation) accessible through:

- FPGA

- JTAG port (SPI indirect (Bus width x4))

- 8 GTX transceivers

- FPGA configuration through:

- JTAG (B2B connector)

- SPI Flash memory

- 25 MHz low jitter oscillator with shutdown control

- Programmable quad PLL clock generator

- On-board high-efficiency DC-DC converters

- GTX voltage regulators with control enable

- Core voltage regulator: 20A (2 x Enpirion DC-DC regulators with load-sharing)

- Supply voltages: either 3.3V or 3.3V and 5V

- Plug-on module with two 100-pin and one 60-pin high-speed hermaphroditic stacking strips

- Up to 144 (94 for 70T) FPGA I/O pins are available on B2B strips (up to 65 LVDS pairs possible)

- 2 user LED's, 1x DONE FPGA pin LED, 1 System Controller status LED

- System management and power sequencing

- AES bit-stream encryption

- eFUSE bit-stream encryption

- Evenly spread supply pins for good signal integrity

- Assembly options for cost or performance optimization available on request

Additional assembly options are available for cost or performance optimization upon request.

| Page break |

|---|

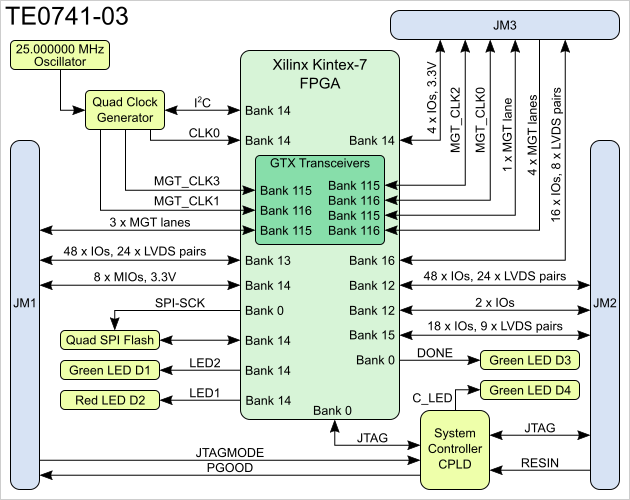

Block Diagram

Figure 1: TE0741 block diagram.

| Page break |

|---|

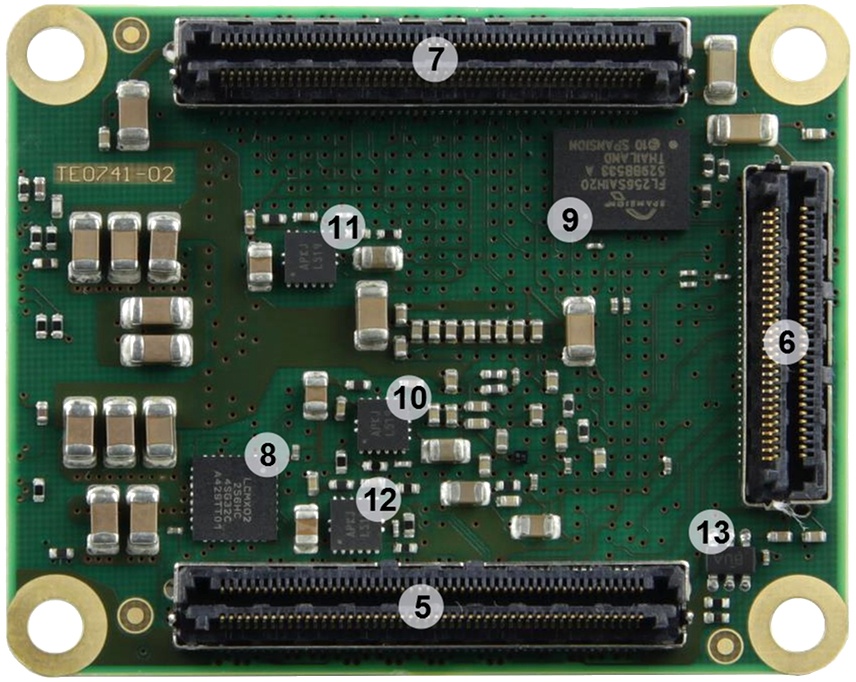

Main Components

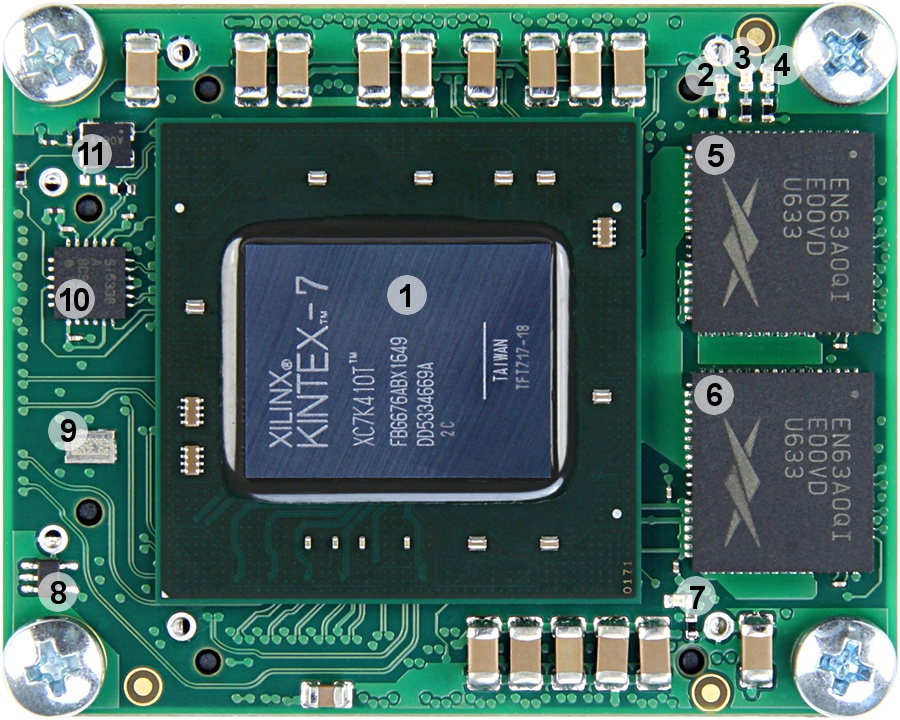

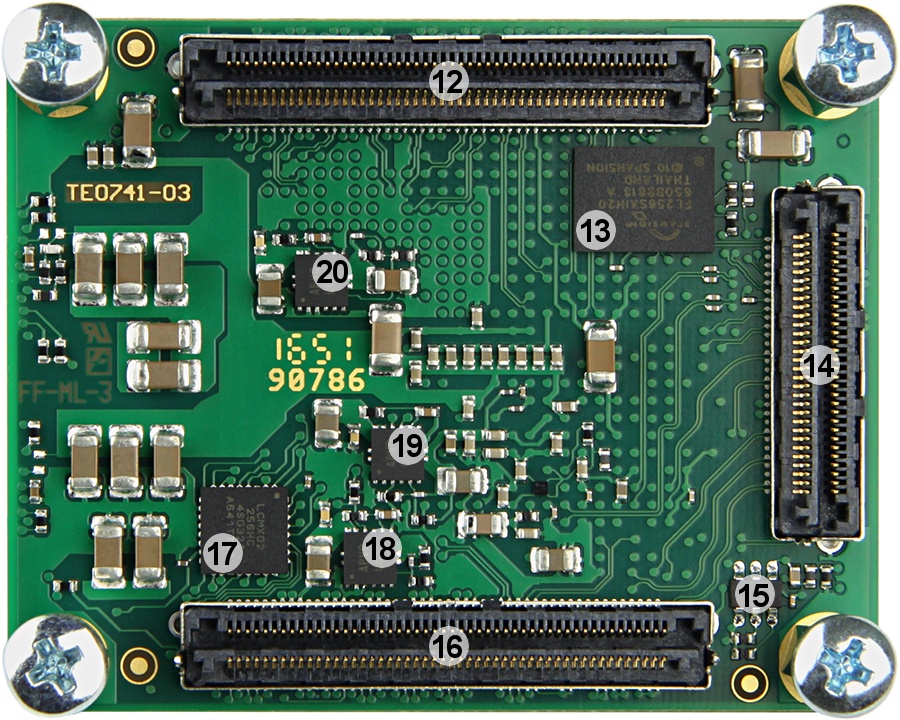

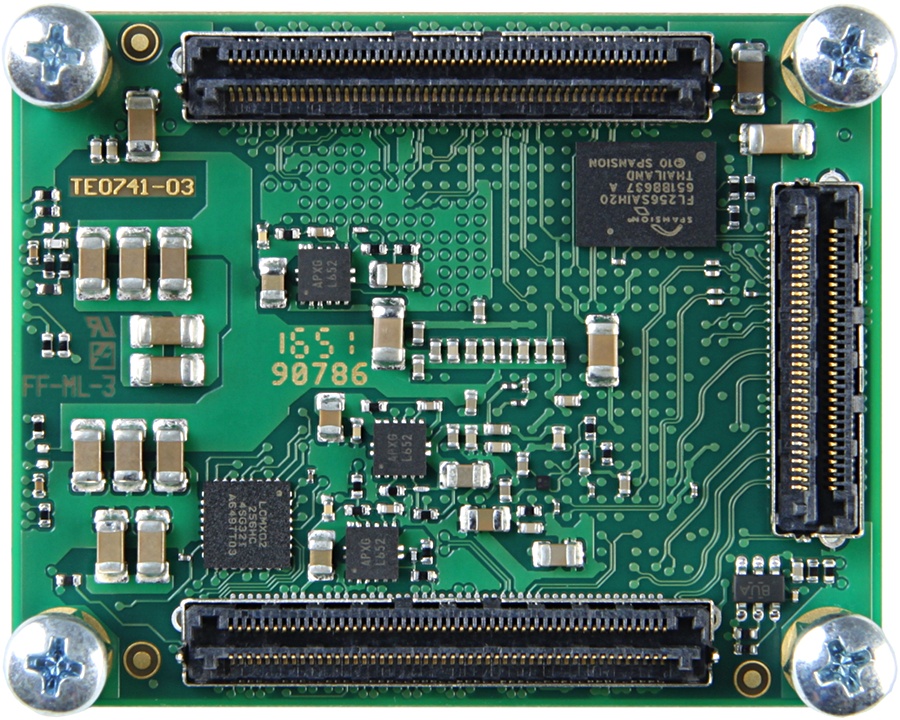

Figure 2.1: TE0741--03-410-2CF module.

Figure 2.2: TE0741-03-160-2C1 module.

- Xilinx Kintex-7 FPGA, U1

- Green LED (DONE), D3

- Red LED (LED1), D2

- Green LED (LED2), D1

- EN63A0QI Voltage Regulator 1.0V (Master), U14

- EN63A0QI Voltage Regulator 1.0V (Slave), U15

- Green LED (C_LED), D4

Voltage detector, U11

- Serial number (traceability) pad

- I2C-programmable any-frequency, any-output quad clock generator, U2

- Low-power programmable oscillator @ 25.000000 MHz, U3

- Samtec Razor Beam™ LSHM-150 B2B connector, JM2

- 32 MByte quad SPI Flash memory, U4

- Samtec Razor Beam™ LSHM-130 B2B connector, JM3

- 3A PFET load switch with configurable slew rate (3.3V), Q1

- Samtec Razor Beam™ LSHM-150 B2B connector, JM1

- System Controller CPLD, U7

- EP53F8QI Voltage Regulator (1.2V_MGT), U6

- EP53F8QI Voltage Regulator (1.8V), U8

- EP53F8QI Voltage Regulator (1V_MGT), U16

Initial Delivery State

| Storage device name | Content | Notes |

|---|---|---|

SPI Flash OTP Area | Empty, not programmed | Except serial number programmed by flash vendor. |

SPI Flash Quad Enable bit | Programmed | - |

SPI Flash main array | Demo design | - |

eFUSE USER | Not programmed | - |

eFUSE Security | Not programmed | - |

...

JTAG access to the Xilinx Kintex7 Kintex-7 and to the System Controller CPLD is provided through B2B connector JM2.

...

Table 3: Pin-mapping of JTAG Interface on B2B connector.

| Note |

|---|

| Select by JTAGMODE pin on 89 in B2B connector JM1 -89 either to access FPGA Artix7 (JTAGMODE pin driven low or open) or System Controller via JTAG (JTAGMODE pin driven high)is used to select which device is accessible, low - Xilinx Kintex-7, high - System Controller CPLD. |

System Controller I/O Pins

...

Table 4: Pin-description of System Controller CPLD.

On-board LEDs

There are four LED's available on TE0741 SoM. Two status LED's (D3 and D4) and two user configurable LED's (D1 and D2).

...

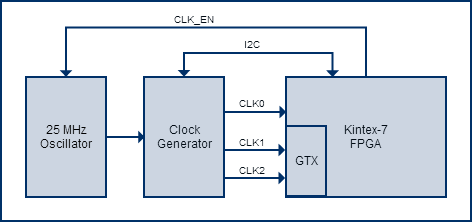

Once running, the frequency and other parameters can be changed by programming the device using the I2C bus connected between the FPGA (master) and clock generator (slave). Logic needs to be generated inside the FPGA to utilize I2C bus correctly.

Figure 3: Clock Generator Clocking block diagram.

| I/O Si5338A (U2) | Default Frequency | Notes |

|---|---|---|

IN1/IN2 | - | Not used (external clock signal supply). |

IN3 | 25MHz | Fixed input clock signal from. reference clock generator SiT8208AI (U3). |

IN4 | - | LSB of the default I2C-Adress 0x70. |

IN5/IN6 | - | Not used (external clock signal supply). |

CLK0 A/B | 100 MHz | Bank 14 clock input, Pins: B14_L12_P, B14_L12_N |

CLK1 A/B | 125MHz | MGT reference clock 1 to FPGA Bank 116 MGT |

CLK2 A/B | 125MHz | MGT reference clock 3 to FPGA Bank 115 MGT |

| CLK3 | - | not used |

Table 7: Pin description of Si5338A PLL clock generator Si5338A.

32 MByte Quad SPI Flash Memory

...

To enable the voltage supply for the GTX transceivers, namely the Enpirion EP53F8QI voltage regulators U6 and U16, which serve the voltages MGTAVCC (1.0 V) and MGTAVTT (1.2 V), the signal EN_MGT (bank 14, pin H22) have to be set high. The voltage regulators will indicate "Power OK" with signals PG_MGT_1V and PG_MGT_1V2, when reaching stable state.

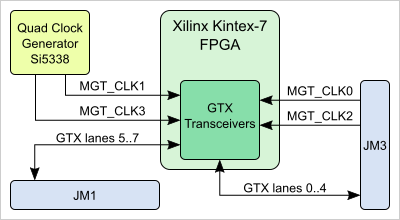

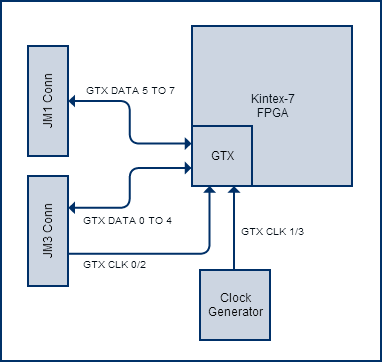

Figure 4: GTX Transceiver transceiver block diagram.

Page break

System Controller CPLD

...

See Xilinx Kintex-7 datasheet (DS182) for the voltage ranges allowed.

...

Variants Currently In Production

Module Variant | FPGA | U15 | FPGA Junction Temperature | Operating Temperature Range |

|---|---|---|---|---|

| TE0741-03-070-2CF | XC7K70T-2FBG676C | - | 0°C to 85°C | commercial grade |

| TE0741-03-070-2IF | XC7K70T-2FBG676I | - | -40°C to 100°C | industrial grade |

| TE0741-03- |

| 160-2CF |

|---|

| XC7K160T-2FBG676C |

| - | 0°C to 85°C | commercial grade |

| TE0741-03- |

|---|

| 160- |

|---|

| 2C1 |

|---|

| XC7K160T- |

| 2FFG676C |

| - | 0°C to 85°C | commercial grade |

| TE0741-03- |

|---|

| 160-2IF |

|---|

| XC7K160T-2FBG676I | - | -40°C to 100°C | industrial grade |

| TE0741-03- |

|---|

| 325- |

|---|

| 2CF |

|---|

| XC7K325T- |

| 2FBG676C |

| EN63A0QI |

| 0°C to |

| 85°C |

| commercial grade | ||||

| TE0741-03-325-2IF | XC7K325T-2FBG676I | EN63A0QI | -40°C to 100°C | industrial grade |

|---|---|---|---|---|

| TE0741-03- |

| 410- |

|---|

| 2CF |

|---|

| XC7K325T- |

| 2FBG676C |

| EN63A0QI | 0°C to 85°C | commercial grade |

Table 11: Differences between variants of Module TE0741-03 variants.

Technical Specifications

...

| Parameter | Min | Max | Units | Notes |

|---|---|---|---|---|

VIN supply voltage | -0.3 | 6.5 | V | - |

| 3.3VIN supply voltage | -0.1 | 3.6 | V | - |

| PL IO bank supply voltage for HR I/O Banks banks (VCCO) | -0.5 | 3.6 | V | - |

| I/O input voltage for HR I/O banks | -0.4 | VCCO_X+0.55 | V | - |

| GT receiver (RXP/RXN) and transmitter (TXP/TXN) | -0.5 | 1.26 | V | Xilinx datasheet DS182 |

| Voltage on module JTAG pins | -0.5 | VCCO_0+0.45 | V | VCCO_0 is 3.3V nominal. |

| Storage temperature | -55 | +125 | °C | - |

...

| Parameter | Min | Max | Units | Notes | Reference Document |

|---|---|---|---|---|---|

| VIN supply voltage | 2.4 | 5.5 | V | - | EP53F8QI data sheet |

| 3.3VIN supply voltage | 3.135 | 3.465 | V | 3,3V ± 5% | - |

| PL I/O bank supply voltage for HR I/O banks (VCCO) | 1.14 | 3.465 | V | - | Xilinx datasheet DS182 |

| I/O input voltage for HR I/O Banksbanks | -0.20 | VCCO+0.2 | V | - | Xilinx datasheet DS182 |

| GT receiver (RXP/RXN) and transmitter (TXP/TXN) | (*) | (*) | - | - | * See datasheet DS182 |

| Voltage on Module module JTAG pins | 3.135 | 3.465 | V | - | - |

Table 13: Recommended operation conditions.

...

.

Operating Temperature Ranges

...

The module operating temperature range depends also on customer design and cooling solution. Please contact us for options.page-break

| Note |

|---|

| Check Xilinx datasheet DS182 for complete list of absolute maximum and recommended operating ratings. |

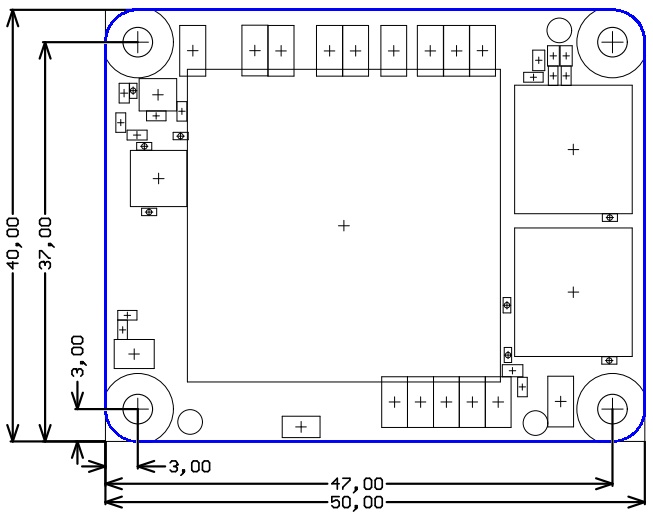

Physical Dimensions

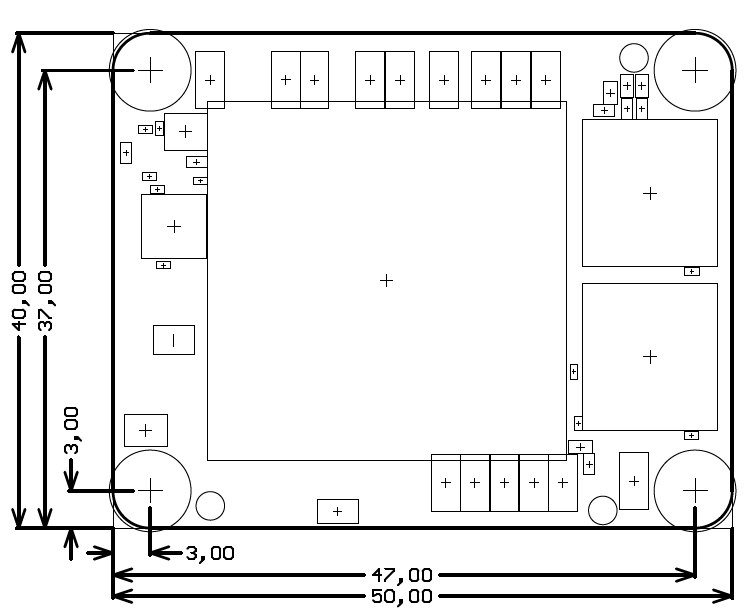

- Module size: 50 mm × 40 mm

- Mating height with standard connectors: 8mm

- PCB thickness: 1.6mm

Figure 7: Physical dimensions of the TE0741-02 module. All dimensions are shown in millimeters.

Weight

19 g - Plain module.

8.8 g - Set of nuts and bolts.

Revision History

Hardware Revision History

- : 8mm

- PCB thickness: 1.6mm

Figure 7: Physical dimensions of the TE0741 module. All dimensions are shown in millimeters.

Weight

19 g - Plain module.

8.8 g - Set of nuts and bolts.

Revision History

Hardware Revision History

| Date | Revision | Notes | PCN | Documentation | |||||

|---|---|---|---|---|---|---|---|---|---|

| 2016-10-25 | 03 | 1) Fixed DC-DC connection for parallel operation 2) Samtec Razor Beam connectors updated 3) Serial number (traceability) pad added 4) Changed ferrite beads L1..L4 size 0402 to BKP0603HS121-T 5) Thermal vias added to mounting holes | PCN-20170106 | TE0741-03 | Date | Revision | Notes | PCN | Documentation|

| 2013-11-06 | 02 |

| TE0741-02 | ||||||

| 01 | First production release |

Hardware revision number is written on the PCB board together with the module model number separated by the dash.

Document Change History

| Date | Revision | Contributors | Description | |

|---|---|---|---|---|

| 2017-06-02 |

| REV03 specific update. | ||

| 2017-01-22 | V42 | Jan Kumann | New block diagram added. | |

| 2017-01-13 | V38 | Jan Kumann | New product images and physical dimension drawings. Formatting improvements and small corrections. | |

| 2017-01-12 | V21 | John Hartfiel | Correction: B2B and FPGA bank location. | |

| 2016-12-14 | V19 | Ali Naseri | TRM revision. | |

| 2013-12-02 | V1 | Antti Lukats, Jon Bean | Initial version. |

...

| Include Page | ||||

|---|---|---|---|---|

|