Page History

...

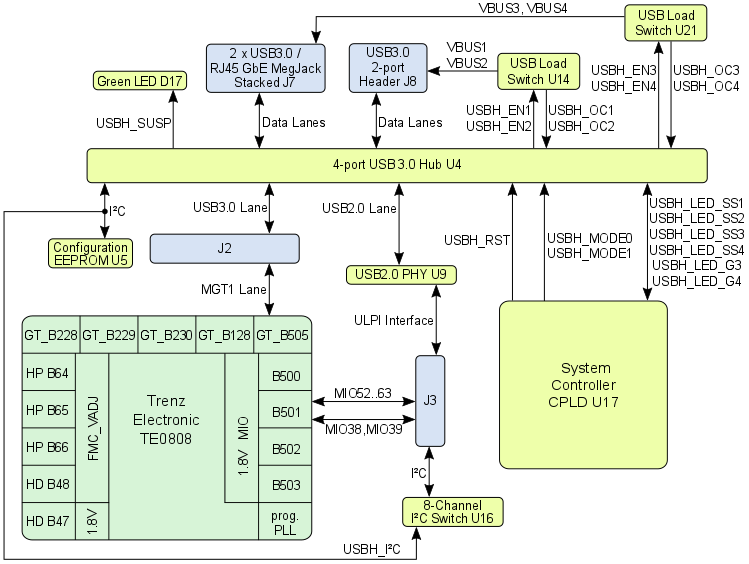

The TEBF0808 Carrier Board offers up to 4 USB3.0 superspeed ports, which are also downward compatible to USB2.0 highspeed ports. The USB3.0 ports are provided by the IC U4, Cypress Semiconductor CYUSB3324 4-port USB3.0 Hub. The pin-strap configuration option of the USB3.0 Hub U4 is disabled, so the Hub will only be configurable over the configuration EEPROM U5. The I²C interface of the EEPROM is also accessible by the MPSoC through I²C switch U16.

On the Upstream-side, this chip is connected to the MGT1-lane of MPSoC's PG GT bank 505 to establish the USB3.0 lane. For the USB2.0 interface, the USB3.0 HUB U4 is connected to the on-board USB2.0 PHY U9. The USB2.0 PHY U9 is connected per ULPI interface through MIO pins 52..63 to MPSoC's MIO bank 501.

Following block-diagram clarifies the wiring of the USB interface with the MPSoC.

Figure 23: TEBF0808 USB3.0 interface

MPSoC's PS GT Bank 505 Peripheral Interfaces

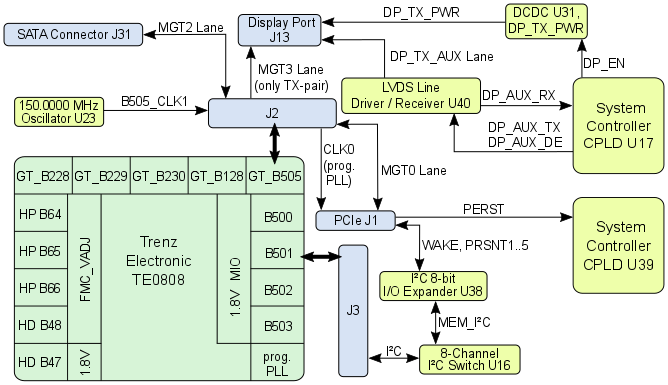

On the PS GT Bank 505 is beside the USB3.0 Lane also the interface SATA, Display-Port and PCI Express connected.

Figure 4: TEBF0808 USB3.0 interface