Page History

...

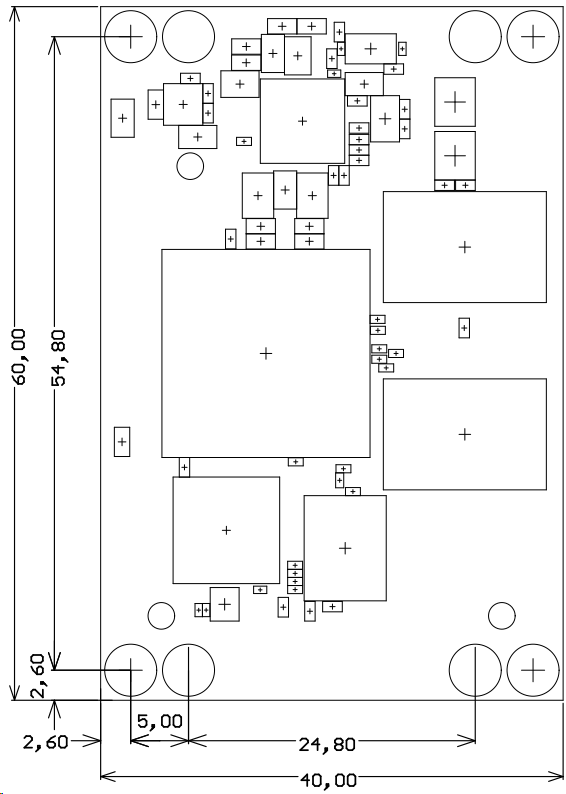

The Trenz Electronic TE0724 is an industrial-grade SoC module based on Xilinx Zynq - 7010/7020, which provides a dual core ARM Cortex A9 and a 7-series FPGA logic. It provides a gigabit ethernet transceiver, 1GByte 1 GByte of DDR3L SDRAM, 32 64 MByte Flash memory as configration and data storage. It includes strong powerregulators power regulators for all needed voltages and a robust high-speed connector for in- and outputs. It has a 6 x 4 cm form factor.

...

- Xilinx Zynq XC7Z010-1CLG400I or XC7Z020-1CLG400I

- Dual-core ARM Cortex-A9 MPCore

- Max. 667 MHz

- Shock proof and vibration resistant

- Size 6 x 4 cm

- Plug-On-Modul with 1 × 160 Pin High-Speed connector

- 1 GByte DDR3L SDRAM

- 32 64 MByte QSPI Flash Speicher

- 1 x GBit Ethernet PHY

- 1 x MAC-Address EEPROM

- 128 KBit EEPROM

- 1 x CAN Transceiver

- On-Board DC/DC-regulators

- Excellent signal integrity due to well dirstributed evenly-spread supply pins

Additional assembly options are available for cost or performance optimization upon request.

...

- XILINX ZYNQ XC7Z020-2CLG400C, U1

- Gigabit Ethernet Transceiver Alaska 88E1512, U7

- Power Manager Dialog DA9062, U4

- 1GByte - 2x 4Gbit DDR3L RAM, U3, U5

- 32MByte Spansion 64MByte ISSI SPI Flash S25FL256IS25LP512M, U13

- 128KByte Serial EEPROM Microchip 24AA, U10

- CAN Transceiver MCP2542FDT, U2

- 160 Pin Samtec B2B Connector ST5-80-1.50-L-D-P-TR, J1

...

Storage device name | Content | Notes |

|---|---|---|

| Spansion ISSI SPI Flash S25FL256IS25LP512M, U13 | Empty | |

| DA9062, U4 | Programmed | |

| Microchip 24AA128T, U10 | Empty | USER EEPROM |

| Microchip 24AA025E48T, U23 | MAC write protected preprogrammed, User area empty | EEPROM for MAC-Address. |

...

On-board QSPI flash memory (U13) on the TE0724-02 04 is a SPANSION S25FL256S ISSI IS25LP512M with 256 512 Mbit (32 64 MByte) storage capacity. This non volatile memory is used to store initial FPGA configuration. Besides FPGA configuration, remaining free flash memory can be used for user application and data storage. All four SPI data lines are connected to the FPGA allowing x1, x2 or x4 data bus widths. Maximum data rate depends on the selected bus width and clock frequency used.

...

A Microchip 24AA128T serial EEPROM (U10) is availabe available for e.g. module idetification identification and user Data. The device has 128Kbit memory with max 64 bytes page write capability. It is accessible over I2C bus with slave device address 0x50.

...

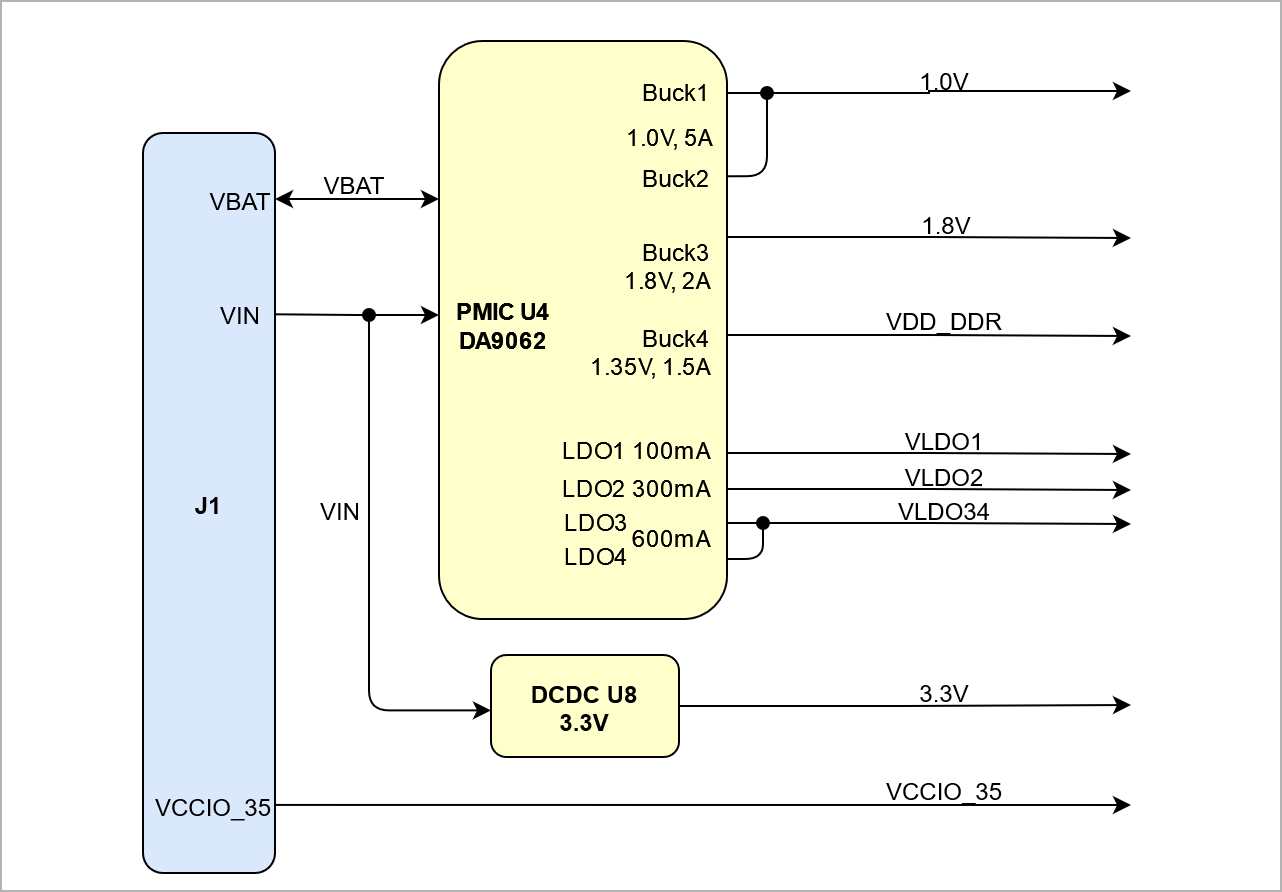

Power Distribution Dependencies

DCDC U8 component is either TPS82140 (2 A) or MUN12A (3 A) depending on the variant.

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

See Xilinx data sheet for additional information. User should also check related base board documentation when intending base board design for TE0724 module.

Power-On Sequence

The TE07024 TE0724 SoM meets the recommended criteria to power up the Xilinx Zynq MPSoC properly by keeping a specific sequence of enabling the on-board DC-DC converters dedicated to the particular functional units of the Zynq chip and powering up the on-board voltages. For a detailed description of the configurabel configurable Power Management IC please refer to the datasheet of of dialog semicondutor DA9062.

...

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

...

Power Rail Name | B2B JM1 Pins | Direction | Notes |

|---|---|---|---|

| VIN | 154, 156, 158,160 | Input | Main supply voltage from the carrier board. |

| VCCIO_35 | 54 | Input | PL Bank 35 supply voltage. |

| VLDO1 | 83 | Output | 3.3V (100mA) |

| VLDO2 | 94 | Output | 1.8V (300mA) |

| VLDO34 | 53 | Output | 2.5V (600mA) |

| 3.3V | 43, 74 | Output | Additional module on-board 3.3V voltage supply (1A2 A or 3 A variant dependent). |

| 1.0V | - | Buck1 & Buck2 of U4. | |

| 1.8V | -63 | Output | Buck3 of U4. |

| VDD_DDR | - | DDR supply voltage powered by Buck4 of U4. | |

VBAT | 152 | Output/Input | Battery charger to the carrier board(out) and supply for RTC and 32kHz crystal (in). |

Table 14: Module power rails.

...

Bank | Schematic Name | Voltage | Voltage Range |

|---|---|---|---|

| 500 MIO | 13.8V 3V | 13.8V3V | - |

| 501 MIO | 1.8V | 1.8V | - |

| 502 DDR3 | VDD_DDRV | 1.35V | - |

| 34 HR | 3.3V | 3.3V | - |

| 35 HR | VCCIO_35 | User | 1.2V to 3.3V |

...

Recommended Operating Conditions

| Parameter | Min | Max | Units | Reference Document |

|---|---|---|---|---|

| VIN supply voltage |

| (variant "-Z" with MUN12A for U8) | 4.5 |

| 5.5 | V |

| VIN supply voltage (all other variants) | 3.6 | 5.5 | V | |

| Operating temperature | -40 | 85 | °C |

Table 19: Module recommended operating conditions.

...

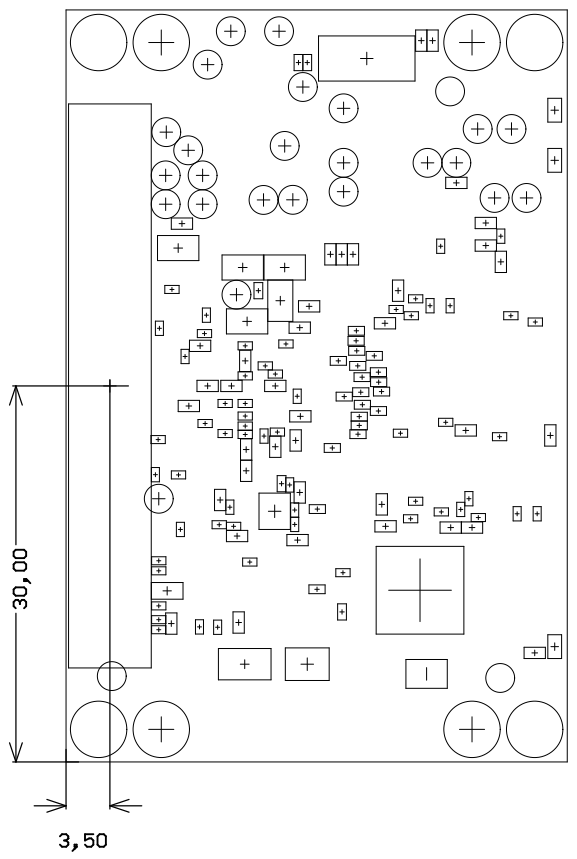

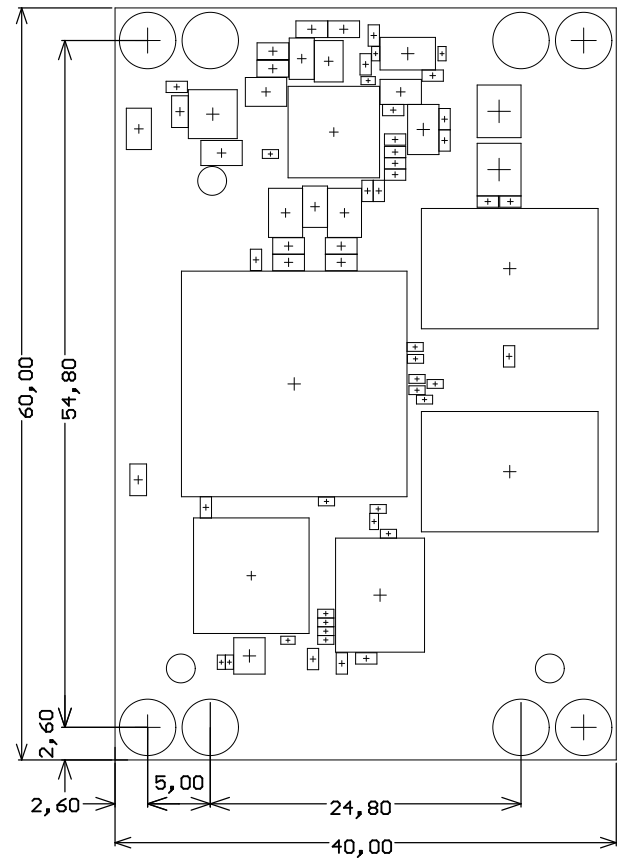

All dimensions are given in millimeters.

| Scroll Title | ||

|---|---|---|

| ||

Revision History

Hardware Revision History

| Date | Revision | Notes |

|---|---|---|

| 2020-11-05 | 04 | Changed DDR3, Flash, see PCN |

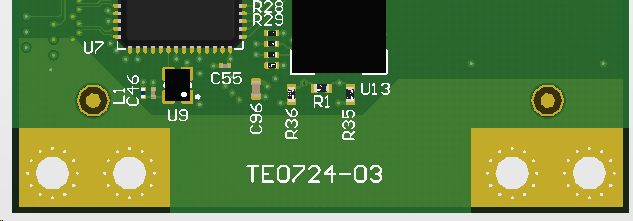

| 2019-03-12 | 03 | changed 3.3V DCDC |

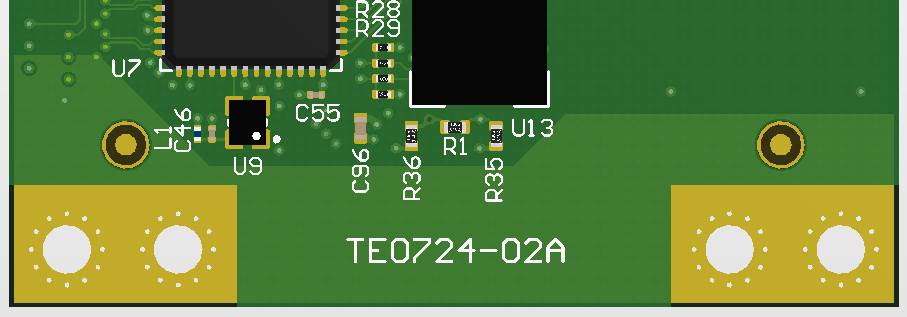

| 02A | Electrical same as REV 02. | |

| 02 | First production release | |

| - | 01 | Prototypes |

...

Hardware revision number can be found on the PCB board together with the module model number separated by the dash.

| Scroll Title | ||

|---|---|---|

| ||

Document Change History

...

Date | Revision | Contributors | Description | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

|

| ||||||||||||||||||||||||||

| 2020-11-17 | v.58 | Martin Rohrmüller |

| |||||||||||||||||||||||||||

| 2019-10-31 | v.56 | Martin Rohrmüller |

| |||||||||||||||||||||||||||

| 2019-10-30 | v.55 | John Hartfield |

| |||||||||||||||||||||||||||

2019-06-27 | v.54 | Martin Rohrmüller |

| |||||||||||||||||||||||||||

2019-06-11 | v.53 | Guillermo Herrera |

| |||||||||||||||||||||||||||

2019-03-29 | v.51 | Martin Rohrmüller |

| |||||||||||||||||||||||||||

2018-11-20 | v.44 | John Hartfiel |

| |||||||||||||||||||||||||||

2018-10-10 | v.43 | John Hartfiel |

| |||||||||||||||||||||||||||

2018-10-09 | v.42 | Martin Rohrmüller |

| |||||||||||||||||||||||||||

2018-10-01 | v.41 | Martin Rohrmüller |

| |||||||||||||||||||||||||||

2018-09-21 Sept 2018 | v.39 | Martin Rohrmüller |

| |||||||||||||||||||||||||||

2018-07-20 Jul 2018 | v.37 | John Hartfield |

| |||||||||||||||||||||||||||

2018-07-06 | v.34 | Martin Rohrmüller |

| |||||||||||||||||||||||||||

| --- | all |

|

|

Table 21: Document change history.

...

| Include Page | ||||

|---|---|---|---|---|

|