Page History

...

Electronic Drive Development Platform (EDDP) provides all necessary software and hardware components for development and evaluation of motor control applications. While those these components (both software and hardware) can also be used separatly separately, this manual describes EDDP usage with default reference hardware platform (EDDP Kit) only.

| Note |

|---|

Hardware components/boards delivered in EDDP Kit are not intended to be used in finished final products. All the software and hardware parts of the EDDP are intended for Developers developers evaluating Motor Control Applications with Xilinx FPGA and/or SoC Devicesdevices. |

Requirements for Functional Test

...

| Note |

|---|

Software version that was used in EMC test: (Visible in the GUI main screnscreen) 2017-7-31 (SVN Tag 5745). |

Requirements for Development

For Requrements for development with SDSoC additonal items are required:

- All items listed under Requirements for Functional Test.

- Basic knowledge of Xilinx All Programmable FPGA and/or SoC devices, basic knowledge of Xilinx SDK and C/C++ programming in order to be able to adapt the firmware to your requirements.

- A PC capable of running Xilinx SDSoC 2017.1 development environment.

- Valid Xilinx SDSoC License license or Vouchervoucher.

For Requirements for development with HLS additonal items are required:

- All items listed under Requirements for Functional Test.

- Basic knowledge of Xilinx All Programmable FPGA and/or SoC devices, basic knowledge of Xilinx SDK and C/C++ programming in order to be able to adapt the firmware to your requirements.

- A PC capable of running Xilinx Vivado 2017.1

...

The radio buttons "Forward" and "Reverse" can be used to change the direction; the target slider will be changed accordingly.

Motor/Encoder

The default motor is supplied in the EDDP Kit; see the chapter Reference Motor for details. Use of custom motors is outside the scope of this manual.

Block Diagram

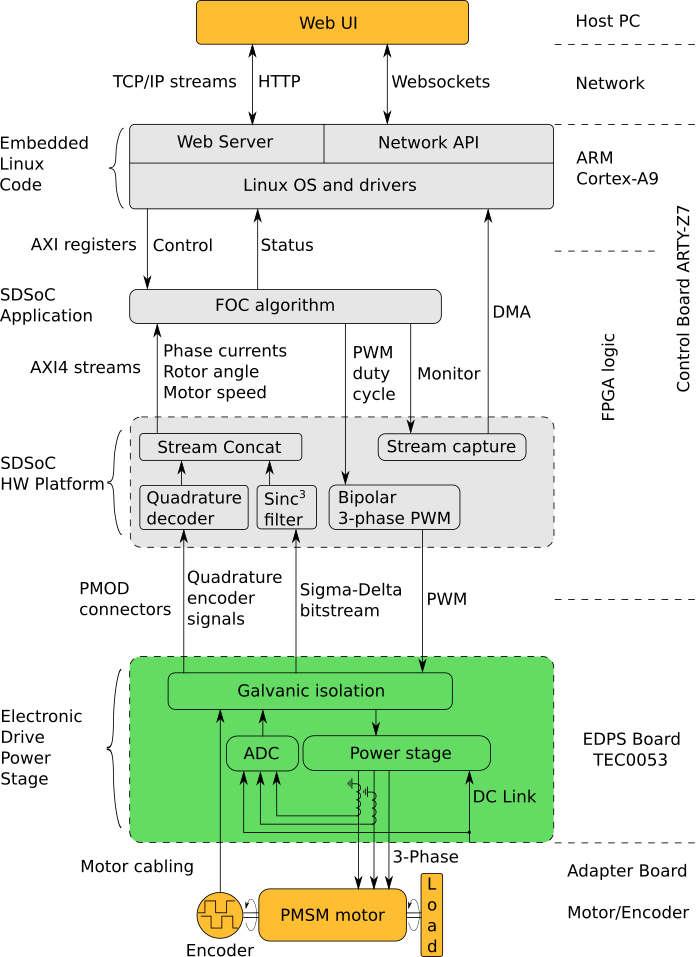

Figure 8: Block diagram of the TEC0060.

...

- The Linux OS manages the hardware and provides execution environment for the programs to run in, which includes a TCP/IP network stack. The drivers included provide access to the control and status registers of the FOC algorithm and to the DMA buffer of the monitor data stream.

- The Network API is a server program, which provides an API built on top of Websockets protocol to control and monitor the FOC algorithm and to capture the monitor data stream.

- The Web Server, which is used to host the Web UI.

The Web UI running in a web browser on the Host PC enables use of the EDDP Kit from anywhere in the network.

...

List of the additional documents

| Title | Description |

|---|---|

| FOC SDSoC | Implementation of a Field-Oriented Control algorithm in C++ with Vivado SDSoC |

| SDSoC Hardware Platform ARTY-Z7 | A basis for building Vivado SDSoC applications running on an Arty-Z7 board connected to a TEC0053 board |

| AXI4-Stream AD7403 | An IP core for filtering the delta-sigma bitstream read from one or more ADC-s of type of AD7403 to an AXI4-Stream of samples |

| AXI4-Stream Encoder | An IP core for converting impulses from a relative index encoder with an index signal to an AXI4-Stream of position and speed data |

| AXI4-Stream PWM | An IP core for generating PWM signals according to the input AXI4-Stream |

| AXI4-Stream Concat | An IP core for concatenating AXI4-Streams |

| Web GUI | A Web UI to control and monitor an EDPS board over the Network API |

| Network API | A communication protocol, based on Websockets, to control an EDPS board |

| Embedded Linux Code | A server program interfacing to an EDPS board and implementing the Network API and the functions of a Web Server |

...