Page History

...

| HTML |

|---|

<!-- General Notes: Designate all graphics and pictures with a number and a description. For example "Figure 1: TE07xx-xx Block Diagram" or "Table 1: Initial delivery state". "Figure x" and "Table x" have to be formatted to bold. --> |

| Scroll Ignore |

|---|

| Scroll pdf ignore | |

|---|---|

Table of Contents

|

...

| # | FTDI Channel A | FTDI Channel B | Pins A to G | Notes | |

|---|---|---|---|---|---|

| 1 | JTAG/SPI (MPSSE) | UART | JTAG, UART | JTAG compatible to Xilinx, Lattice and open-source software that uses FTDI MPPSE | |

| 2 | JTAG/SPI (MPSSE) | JTAG/SPI (MPSSE) | JTAG, JTAG | Dual JTAG, only Channel A is Xilinx compatible | |

| 3 | UART | UART | UART, UART | Dual UART | |

| 4 | I2C | UART | I2C, UART | ||

| 5 | MPSSE | 8x GPIO | |||

| 6 | UART | 8x GPIO | |||

| 7 | UART | UART | not used | UART to UART loopback | |

| 8 | not used | Fast Serial | FTDI 4-wire fast serial adapter, custom EEPROM is needed to enable this mode | ||

| 9 | CPLD update only | not used | user defined | Standalone Module with CPLD and 8 user programmable I/O |

...

- Xmod form-factor

- size: 20 x 25 mm

- M3 mounting hole

- FT2232H

- USB2.0 port High Speed (480 Mbps) and Full Speed (12 Mbps) compatible

- Entire USB protocol handled on the chip

- USB2.0 to JTAG, SPI and I²C conversion provided by the IC's Multi-Protocol Synchronous Serial Engine (MPSSE)

- USB2.0 to UART conversion

- Channel B UART RX/TX LED's

- Mini-USB B connector (more rigid then micro-USB)

- 93C56 EEPROM

- Lattice XO2-256 CPLD

- on board programmable using Lattice tools

- 8 universal I/O pins

- VCCIO either 3.3V or user supplied (1.8 to 3.3V)

- RED user LED

- 12 MHz clock from on-board Oscillator

- Variable power supply of the XMOD adapter board

- by Mini USB2.0 connector

- by base-board through pin header J2

- GREEN Power-on LED

- User button

- 4 position DIP switch

- Choose CPLD program mode

- FTDI EEPROM disable (not implemented in PCB REV 1)

- Use VIO same as VCC

- Use VCC from USB

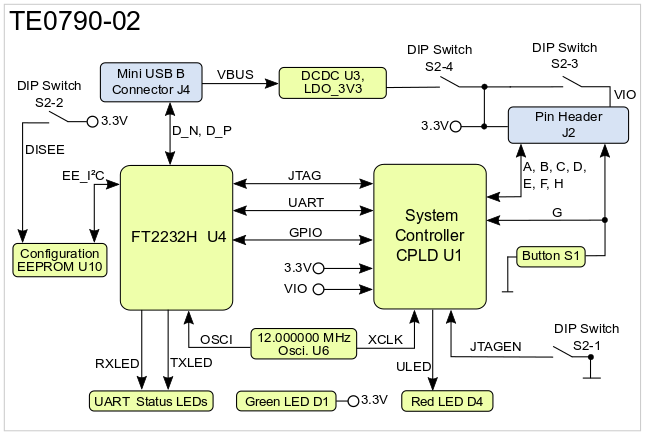

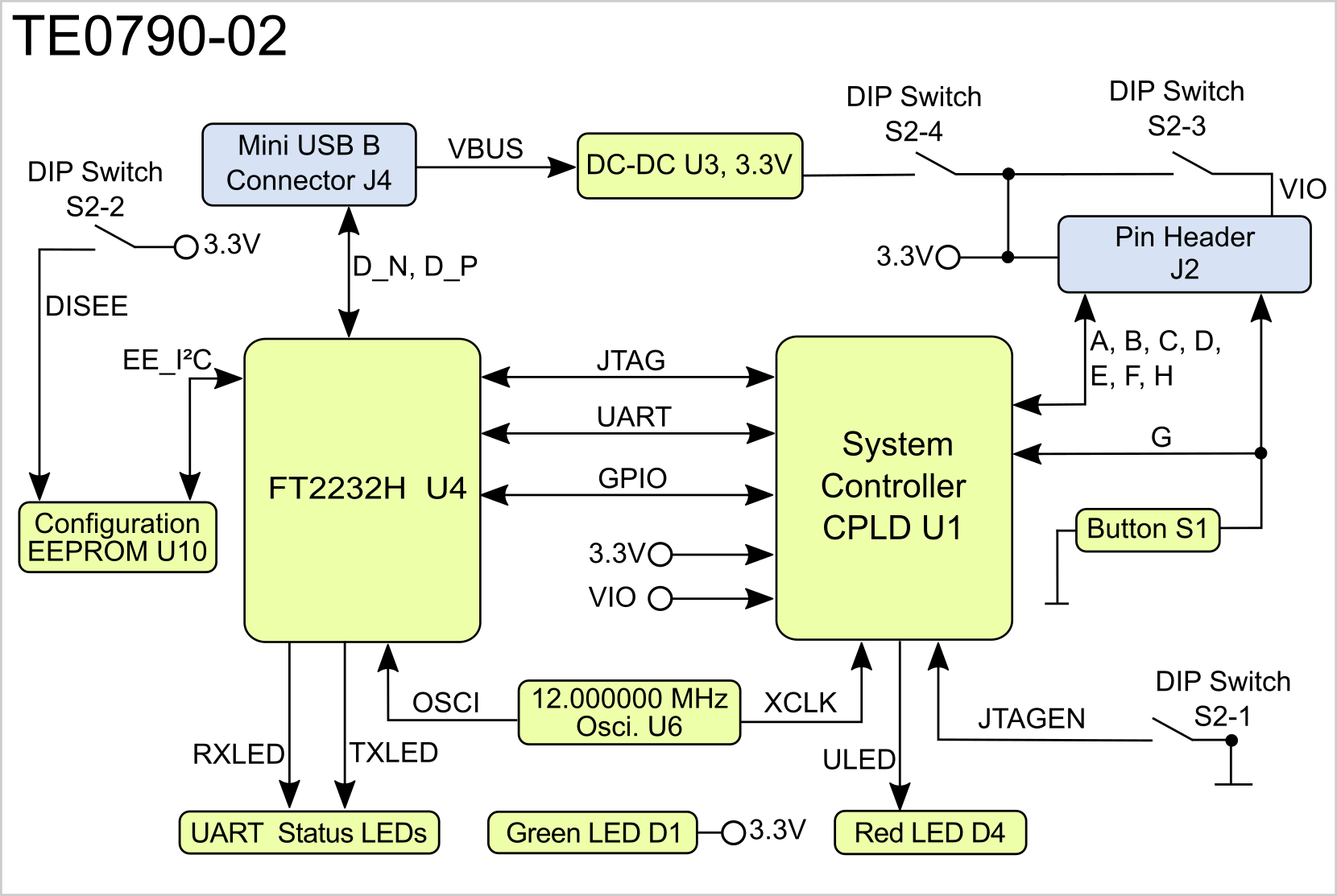

Block Diagram

Figure 1: TE0790-02 block diagram.

...

| Signal | J2 Pin Name | J2 Pin Name | Signal | ||

|---|---|---|---|---|---|

| GND | 1* | GND | |||

| User Defined | C | A | User Defined | ||

| VIO | VDD 3.3V | ||||

| User Defined | D | B | User Defined | ||

| User Defined | F | E | User Defined | ||

| User Defined | H | G | User Defined / Button (Reset_n) |

Table 3: Pin header J2 signal assignment. *pin 1 on header J2

Top View | Bottom View flipped |

Figure 3: J2 pin header signal assignment

...

| FTDI | Signal | Pull up/down | J2 Pin Name | J2 Pin Name | Pull up/down | Signal | FTDI | |||

|---|---|---|---|---|---|---|---|---|---|---|

| GND | - | 1* | - | GND | ||||||

| ADBUS0 | TCK (output from adapter) | C | A | up | UART RXD (input to adapter) | BDBUS1 | ||||

| VIO | - | - | VDD 3.3V | |||||||

| ADBUS2 | TDO (input to adapter) | up | D | B | UART TXD (output from adapter) | BDBUS0 | ||||

| ADBUS1 | TDI (output from adapter) | F | E | down | LED | |||||

| ADBUS3 | TMS (output from adapter) | H | G | up | Button (Reset_n) |

Table 4: Pin header J2 signal assignment with standard configuration firmware. *pin 1 on header J2

...

| FTDI | Signal | Pull up/down | J2 Pin Name | J2 Pin Name | Pull up/down | Signal | FTDI | |||

|---|---|---|---|---|---|---|---|---|---|---|

| GND | - | 1* | - | GND | ||||||

| ADBUS0 | TCK (output from adapter) | C | A | UART TXD (output from adapter) | BDBUS0 | |||||

| VIO | - | - | VDD 3.3V | |||||||

| ADBUS2 | TDO (input to adapter) | up | D | B | up | UART RXD (input to adapter) | BDBUS1 | |||

| ADBUS1 | TDI (output from adapter) | F | E | down | LED | |||||

| ADBUS3 | TMS (output from adapter) | H | G | up | Button (Reset_n) |

Table 5: Pin header J2 signal assignment with standard, but RXD-TXD swapped configuration firmware. *pin 1 on header J2

...

| FTDI | Signal | Pull up/down | J2 Pin Name | J2 Pin Name | Pull up/down | Signal | FTDI | |||

|---|---|---|---|---|---|---|---|---|---|---|

| GND | - | 1* | - | GND | ||||||

| BDBUS1 | UART RXD (input to adapter) | up | C | A | TCK (output from adapter) | ADBUS0 | ||||

| VIO | - | - | VDD 3.3 V | |||||||

| BDBUS0 | UART TXD (output from adapter) | D | B | TMS (output from adapter) | ADBUS3 | |||||

| ADBUS1 | TDI (output from adapter) | F | E | up | TDO (input to adapter) | ADBUS2 | ||||

| not used | H | G | CPLD User LED 'ULED' |

Table 6: Pin header J2 signal assignment with DIPFORTy firmware.

...

The System Controller CPLD (U1) is provided by Lattice Semiconductor LCMXO2-256HC (MachXO2 Product Family). The The SC-CPLD is the central system management unit where essential control signals are logically linked by the implemented logic in CPLD firmware, which generates output signals to control the system, the on-board peripherals and the interfaces.

...

The internal routing of the signals on the System Controller CPLD between the USB2.0 interface and pin header J2 J2 depends on its configured firmware. CPLD can be set into JTAG chain via S2-1 DIP Switch. Refer to the Resources Site of the TE0790 the TE0790 CPLD Firmware for more information about the currently available System Controller CPLD firmware and for download.

...

The DIP-switch S2 is to set different modes of powering the on-board peripherals and their components, the I/O supply voltages .Further functionalities are to secure the EEPROM content and to enable configuring programming the SC adapter board CPLD by JTAG interface:

| S2 | ON | OFF | Default | Description |

|---|---|---|---|---|

| 1 | Normal mode | Module Adapter board CPLD update mode | ON | Update Mode JTAG access to SC CPLD only |

| 2 | Do not use (illegal setting) | Normal mode | OFFDo not change from default, secure configuration EEPROM | Must be in OFF state always. |

| 3 | VIO connected to 3.3V | Power VIO from pin header J2 | OFF | SC CPLD User I/O -voltage from/to pin headerVoltage |

| 4 | Power 3.3V from USB | Power 3.3V from pin header J2 | OFF | Power on-board peripherals (FTDI chip & SC CPLD, ...) |

...

| S2-3 | S2-4 | 3.3V (VCC) Pin 5 | VIO Pin 6 | Description |

|---|---|---|---|---|

| OFF | OFF | 3.3V from base (input**) | VIO from base (input**) | 3.3V (pin 5) and VIO (pin 6) sourced from base |

| OFF | ON | 3.3V from USB* (output**) | VIO from base (input**) | VIO sourced from base by Pin 6 |

| ON | OFF | 3.3V from base (input**) | 3.3V from base (input**) | VIO sourced by Pin 6 and drive Pin 5and 3.3V source by base (Pin 5 and Pin 6 are shorted and both must be sourced by 3.3V) |

| ONON | ON | 3.3V from USB* (output**) | 3.3V from USB* (output**) | 3.3V (pin 5) and VIO (pin 6) sourced USB (Pin 5 and Pin 6 are shorted and both are 3.3V) |

- *max. 100mA for external components (It's not recommended to supply FPGA Module)

Attention: Do not use this setting, if base power supply is connected to this pins! For more details see Power supply of the adapter board section. - **view of XMOD

Table 8: DIP-switch S2 power setting descriptionTable 8: DIP-switch S2 power setting description. *Attention: don't supply voltage from base if pin sourced from USB!.

User Push Button

The user push button S1 directly connected to the SC CPLD manipulates pin G of the pin header J2 by driving it to GND.

...

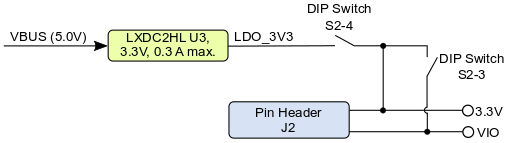

Power supply of the adapter board

The adapter on-board's peripherals are powered XMOD can be powered via USB or with 3.3V as supply voltage. If 3.3V and VIO is supplied only by the LDO DCDC U3 (S2-3 and S2-4 ON), the I/O-pins of header J2 deliver max. ~100mA.

If module is powered from base then S2-4 (and most likely S2-3 (VIO) too) must be OFF.on J2 pins, depending on DIP-switch settings. Max. ~100mA for external components are available on J2 3.3V Pin, if the power supply via USB is used.

Following diagram shows how the settings Following diagram shows how the settings of the DIP-switches S2-3 and S2-4 determines the configuration of the on-board voltages:

Figure 4: TE0790 on-board voltages configuration

...

Date | Revision | Contributors | Description | ||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||||||

2018-01-18 | v.37 | John Hartfiel |

| ||||||||||||||||||||||||||

| 2017-11-16 | v.34 | Ali Naseri |

| ||||||||||||||||||||||||||

2017-10-26 | v.27 Page info | | modified-date | modified-date | dateFormat | yyyy-MM-ddJohn Hartfiel |

| ||||||||||||||||||||||

| 2017-10-19 | v.26 | Ali Naseri |

| ||||||||||||||||||||||||||

| -- | all |

|

|

Table 15: Document change history.

...

| Include Page | ||||

|---|---|---|---|---|

|