Page History

...

RGPIO_EXT External Interface

| Port Name | IO | Description |

|---|---|---|

| RGPIO_M_CLK | out | RGPIO Master Clock |

| RGPIO_M_RX | in | RGPIO Master RXD |

| RGPIO_M_TX | out | RGPIO Master TXD |

| Port Name | IO | Description |

|---|---|---|

| RGPIO_S_CLK | out | RGPIO Slave Clock |

| RGPIO_S_RX | in | RGPIO Slave RXD |

| RGPIO_S_TX | out | RGPIO Slave TXD |

RGPIO_M_USR Interface

| Port Name | IO | Description |

|---|---|---|

| RGPIO_M_OUT | out | Data output to slave device |

| RGPIO_M_IN | in | Data input from slave device |

| RGPIO_M_RESERVED_OUT | out | Reserved for future usage |

| RGPIO_M_RESERVED_IN | in | Reserved for future usage |

| RGPIO_M_SLAVE_ACTIVATION_CODE | out | Activation code from external slave for information only |

| RGPIO_M_ENABLE | in | Enable RGPIO communication |

| RGPIO_M_USRCLK | in | RGPIO transmission CLK for master and slave |

| RGPIO_M_RESET_N | in | RGPIO Reset |

RGPIO_M_USR Interface

| Port Name | IO | Description |

|---|---|---|

| RGPIO_S_OUT | out | Data output to master device |

| RGPIO_S_IN | in | Data input from master device |

| RGPIO_S_RESERVED_OUT | out | Reserved for future usage |

| RGPIO_S_RESERVED_IN | in | Reserved for future usage |

| RGPIO_S_MASTER_ACTIVATION_CODE | out | Activation code from external master for information only |

| RGPIO_S_ENABLED | out | Interface status |

Designing with the Core

This chapter includes guidelines and additional information to facilitate designing with the core.

...

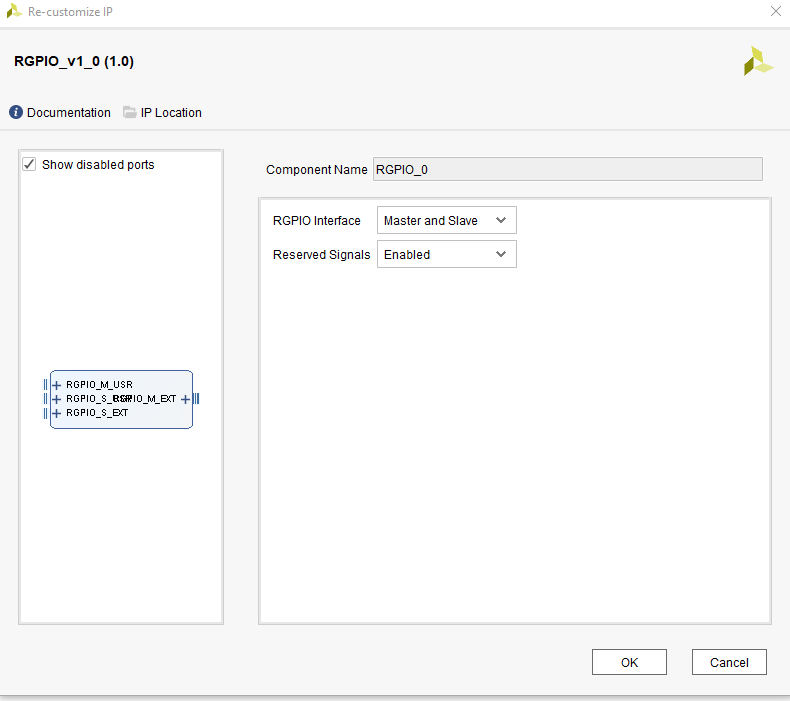

Customizing and Generating the Core

This section includes information about using Xilinx® tools to customize and generate the core in the Vivado Design Suite.

- RGPIO Interface: Master, Slave or both are possible

- Reserved Signals: Active/Deactivate reserved signals as interface

This section includes information about using Xilinx® tools to customize and generate the core in the Vivado Design Suite.

Constraining the Core

This section contains information about constraining the core in the Vivado Design Suite.

Required Constraints

This section is not applicable for this IP coreLoc constrains and IO Standard depends on module and usage.

Device, Package, and Speed Grade Selections

This section is not applicable for this IP core.

Clock Frequencies

This section is not applicable for this IP core.

Clock Management

Maximum RGPIO output CLK depends on Master and Slave device implementation. In the most cases maximum frequency of 25MHz is always allowed.

Clock Management

This section is not applicable for this IP core.

Clock Placement

This section is not applicable for this IP core.

...

Appx. A: Change History and Legal Notices

Document Change History

| Date | Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

|

Legal Notices

| Include Page | ||||

|---|---|---|---|---|

|

...