Page History

...

| Date | Vivado | Project Built | Authors | Description |

|---|---|---|---|---|

| 2018-06-21 | 2017.4 | TE0841-test_board_noprebuilt-vivado_2017.4-build_11_20180621164459.zip | John Hartfiel |

|

| 2018-05-15 | 2017.4 | TE0841-test_board_noprebuilt-vivado_2017.4-build_08_20180515144542.zip TE0841-test_board-vivado_2017.4-build_08_20180515144523.zip | John Hartfiel |

|

...

| Module Model | Board Part Short Name | PCB Revision Support | DDR | QSPI Flash | Others | Notes |

|---|---|---|---|---|---|---|

| TE0841-01-035-1C | 01_35_1c | REV01 | 2x 512MB DDR4 | 32MB | --- | |

| TE0841-01-035-1I | 01_35_1i | REV01 | 2x 512MB DDR4 | 32MB | --- | |

| TE0841-01-035-2I | 01_35_2i | REV01 | 2x 512MB DDR4 | 32MB | --- | |

| TE0841-01-040-1C | 01_40_1c | REV01 | 2x 512MB DDR4 | 32MB | --- | |

| TE0841-01-040-1I | 01_40_1i | REV01 | 2x 512MB DDR4 | 32MB | --- | |

| TE0841-01-040-2I | 01_40_2i | REV01 | 2x 512MB DDR4 | 32MB | --- | |

| TE0841-02-035-1C | 02_35_1c | REV02 | 2x 1GB DDR4 | 64MB | --- | |

| TE0841-02-035-1I | 02_35_1i | REV02 | 2x 1GB DDR4 | 64MB | --- | |

| TE0841-02-035-2I | 02_35_2i | REV02 | 2x 1GB DDR4 | 64MB | --- | |

| TE0841-02-040-1C02_40_1c-02-040-1C | 02_40_1c | REV02 | 2x 1GB DDR4 | 64MB | --- | |

| TE0841-02-040-1I | 02_40_1i | REV02 | 2x 1GB DDR4 | 64MB | --- | |

| TE0841-02-040-1IL | 02_40_1i | REV02 | 2x 1GB DDR4 | 64MB | low profile B2B connector |

Design supports following carriers:

...

- Speed: 9600

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

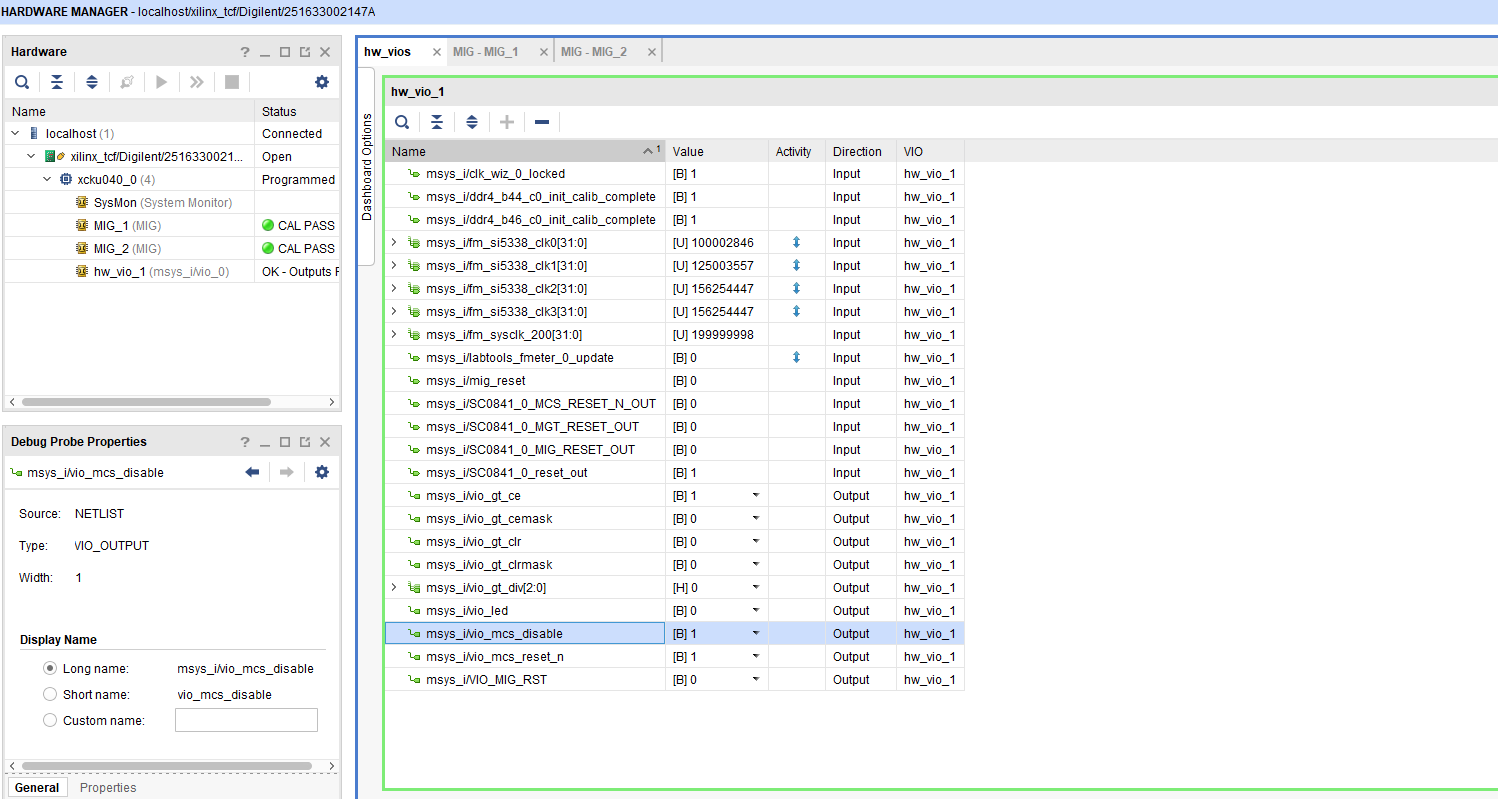

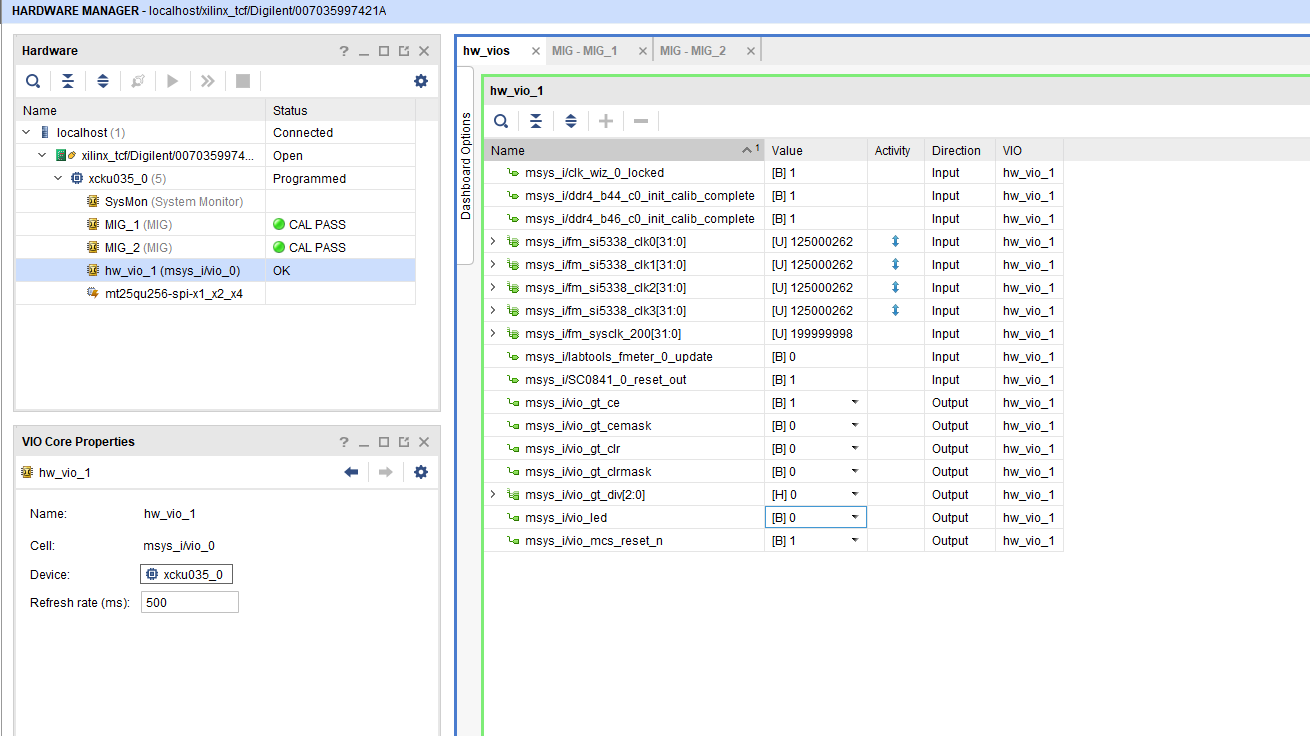

Vivado HW Manager:

- Open Vivado HW-Manager and add VIO signal to dashboard (*.ltx located on prebuilt folder).

- Set radix from VIO signals (fm_si...) to unsigned integer.

Note: Frequency Counter is inaccurate and displayed unit is Hz - SI will be configured with MCS firmware, default all off on PCB REV01, PCB REV02 SI5338 will be preconfigured.

- LED control via VIO

- MGT CLK Freq can be changed over BUFG_GT control signals divider

- MCS Reset possible via VIO

- MIG Reset is possible over VIO

- MCS can be disabled over VIO (For PCB REV01 MCS is enabled, fpr PCB REV02 MCS is disabled by default VIO)

- Set radix from VIO signals (fm_si...) to unsigned integer.

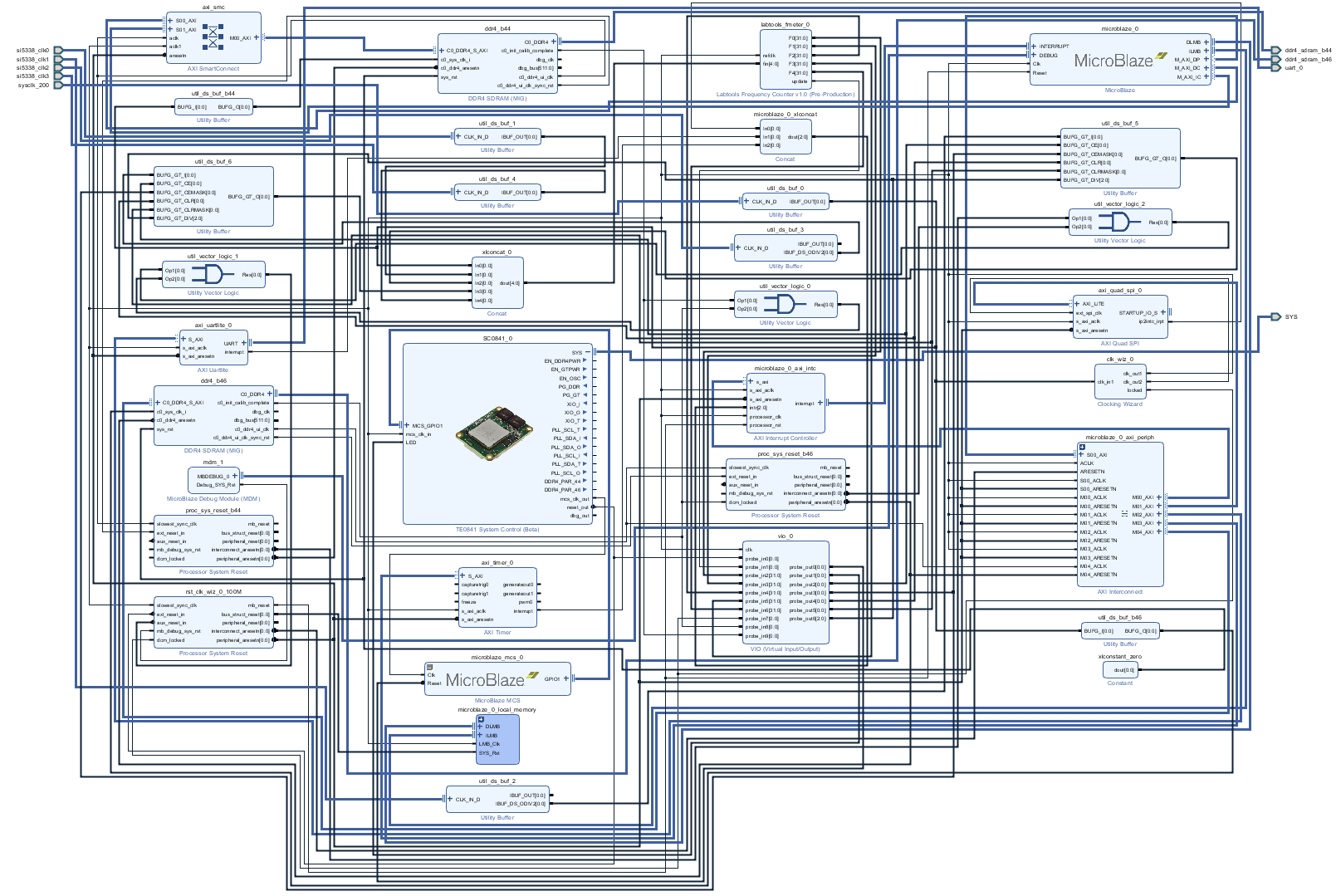

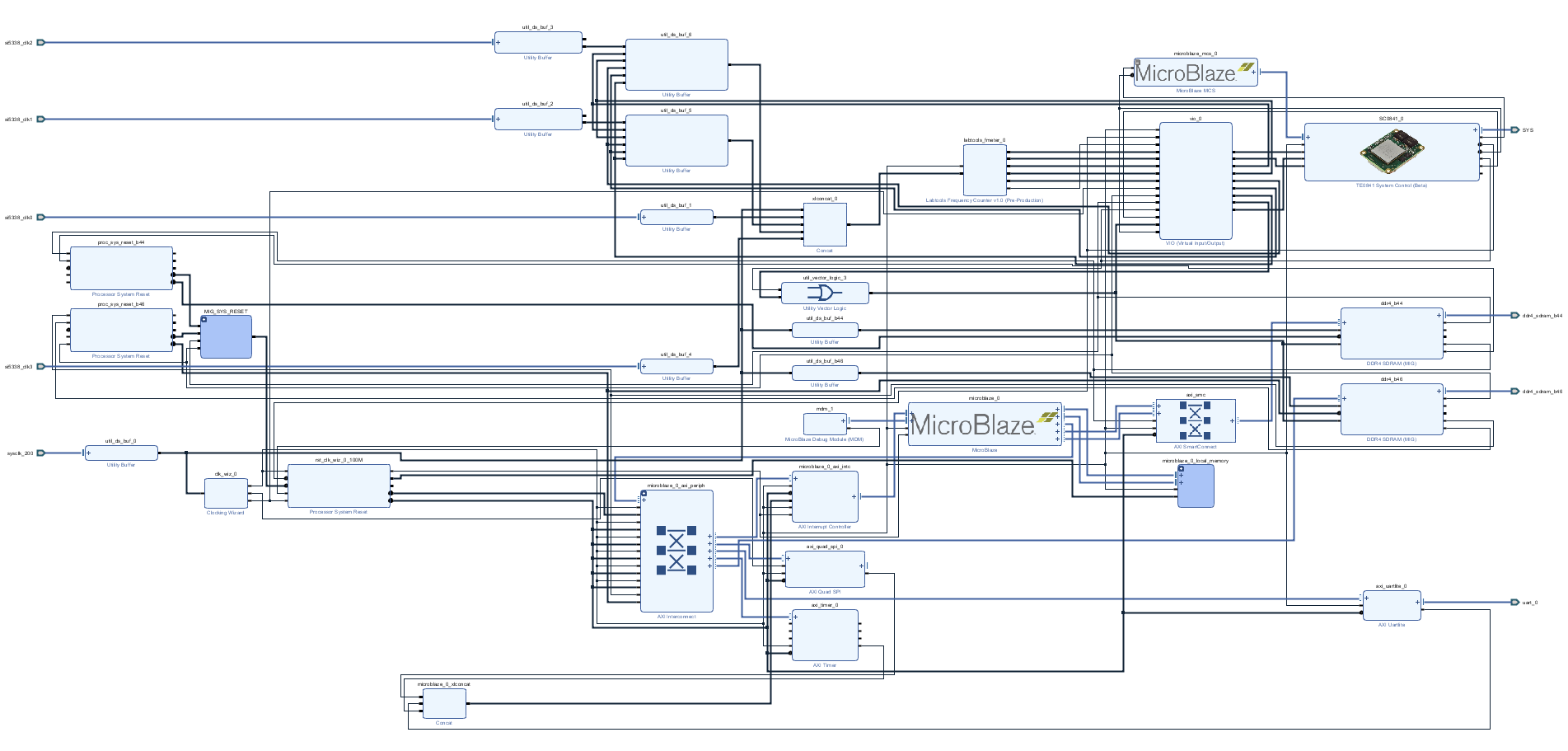

System Design - Vivado

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

Block Design

Constrains

Basic module constrains

...

| Code Block | ||||||

|---|---|---|---|---|---|---|

| ||||||

set_false_path -from [get_clocks {msys_i/util_ds_buf_5/U0/BUFG_GT_O[0]}] -to [get_clocks -of_objects [get_pins msys_i/clk_wiz_0/inst/mmcme3_adv_inst/CLKOUT0]]

set_false_path -from [get_clocks {msys_i/util_ds_buf_6/U0/BUFG_GT_O[0]}] -to [get_clocks -of_objects [get_pins msys_i/clk_wiz_0/inst/mmcme3_adv_inst/CLKOUT0]]

set_false_path -from [get_clocks -of_objects [get_pins msys_i/clk_wiz_0/inst/mmcme3_adv_inst/CLKOUT0]] -to [get_clocks {msys_i/util_ds_buf_6/U0/BUFG_GT_O[0]}]

set_false_path -from [get_clocks -of_objects [get_pins msys_i/clk_wiz_0/inst/mmcme3_adv_inst/CLKOUT0]] -to [get_clocks {msys_i/util_ds_buf_5/U0/BUFG_GT_O[0]}]

set_false_path -from [get_clocks -of_objects [get_pins msys_i/clk_wiz_0/inst/mmcme3_adv_inst/CLKOUT0]] -to [get_clocks {msys_i/util_ds_buf_1/U0/IBUF_OUT[0]}]

set_false_path -from [get_clocks -of_objects [get_pins msys_i/clk_wiz_0/inst/mmcme3_adv_inst/CLKOUT0]] -to]] -to [get_clocks {msys_i/util_ds_buf_4/U0/IBUF_OUT[0]}]

set_false_path -from [get_clocks {msys_i/util_ds_buf_0/U0/IBUF_OUT[0]}] -to [get_clocks -of_objects [get_clockspins {msys_i/utilclk_dswiz_buf_40/U0inst/IBUF_OUT[0]}mmcme3_adv_inst/CLKOUT0]]

set_false_path -from [get_clocks {msys_i/util_ds_buf_1/U0/IBUF_OUT[0]}] -to [get_clocks -of_objects [get_pins msys_i/clk_wiz_0/inst/mmcme3_adv_inst/CLKOUT0]]

set_false_path -from [get_clocks {msys_i/util_ds_buf_4/U0/IBUF_OUT[0]}] -to [get_clocks -of_objects [get_pins msys_i/clk_wiz_0/inst/mmcme3_adv_inst/CLKOUT0]]

|

...

Modified Xilinx SREC Bootloader. Changes: Correct flash typ and SRec Start address, some additional console outputs, see source code

Changed xilisf_v5_9 to support N25Q512_1V8 for SREC (changes on xilisf.c and xilisf_intelstm.h)

Template location: \sw_lib\sw_apps\srec_spi_bootloader

...

| Date | Document Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||

| v.3 | John Hartfiel |

| |||||||||||||||||||||||

| 2018-04-16 | v.1 |

|

| ||||||||||||||||||||||

| All |

|

...

Overview

Content Tools